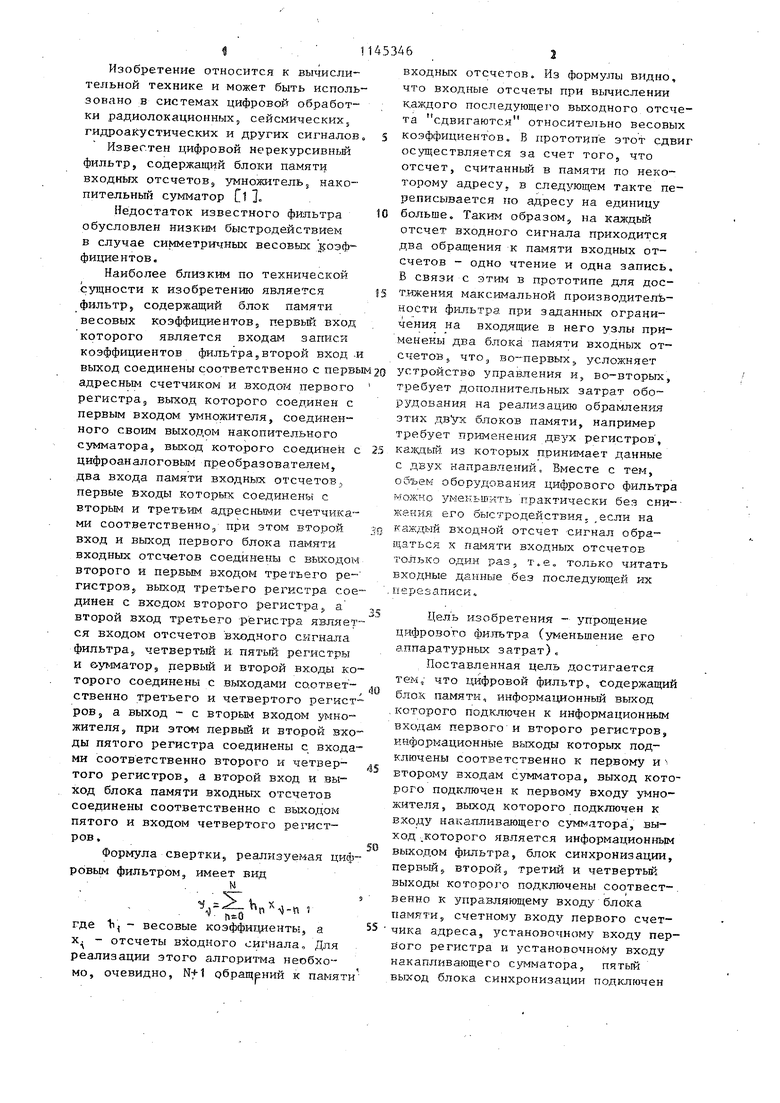

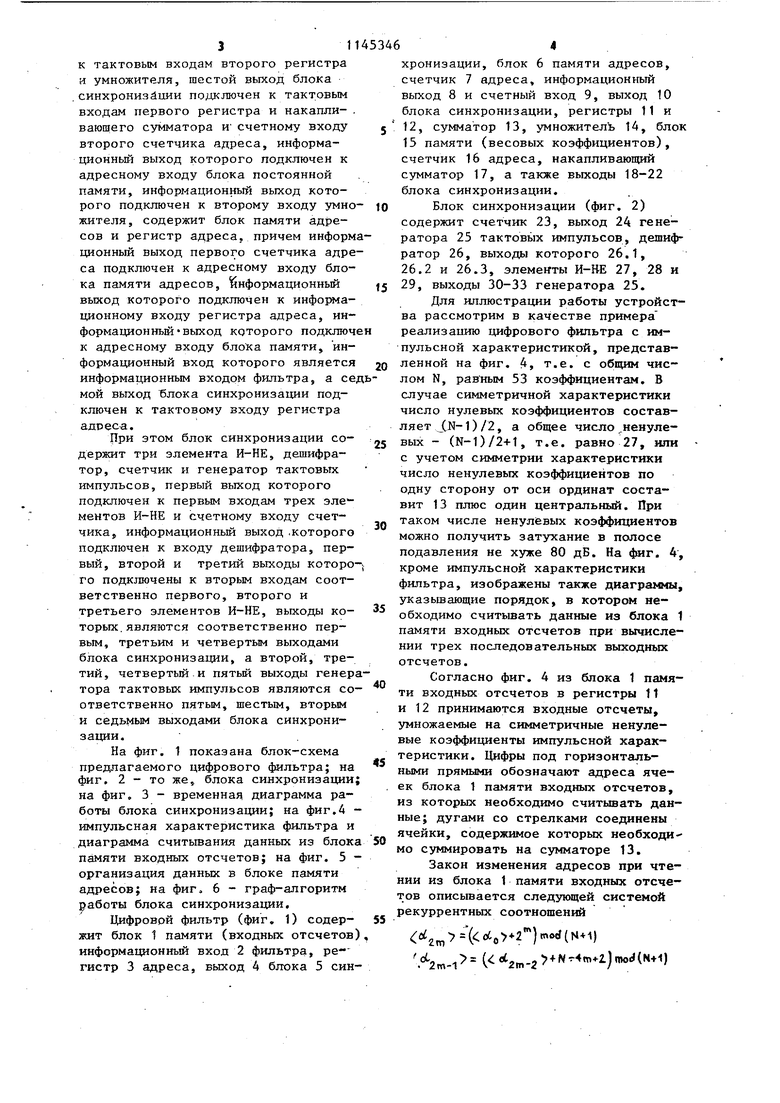

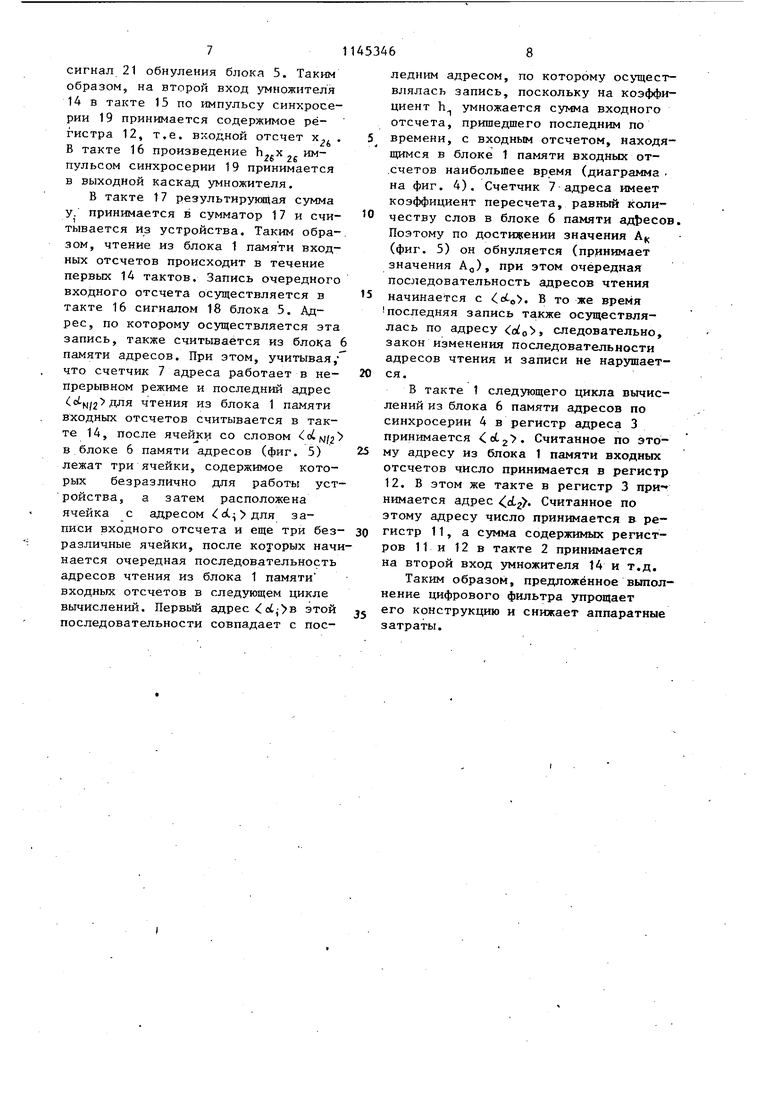

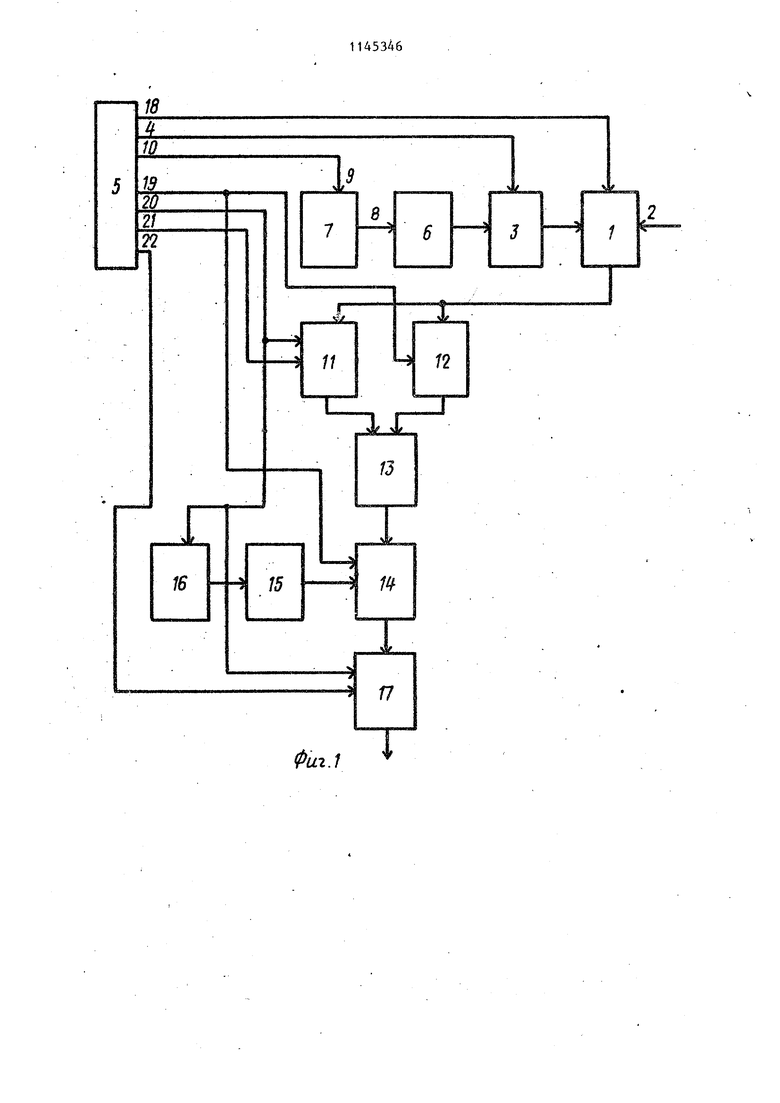

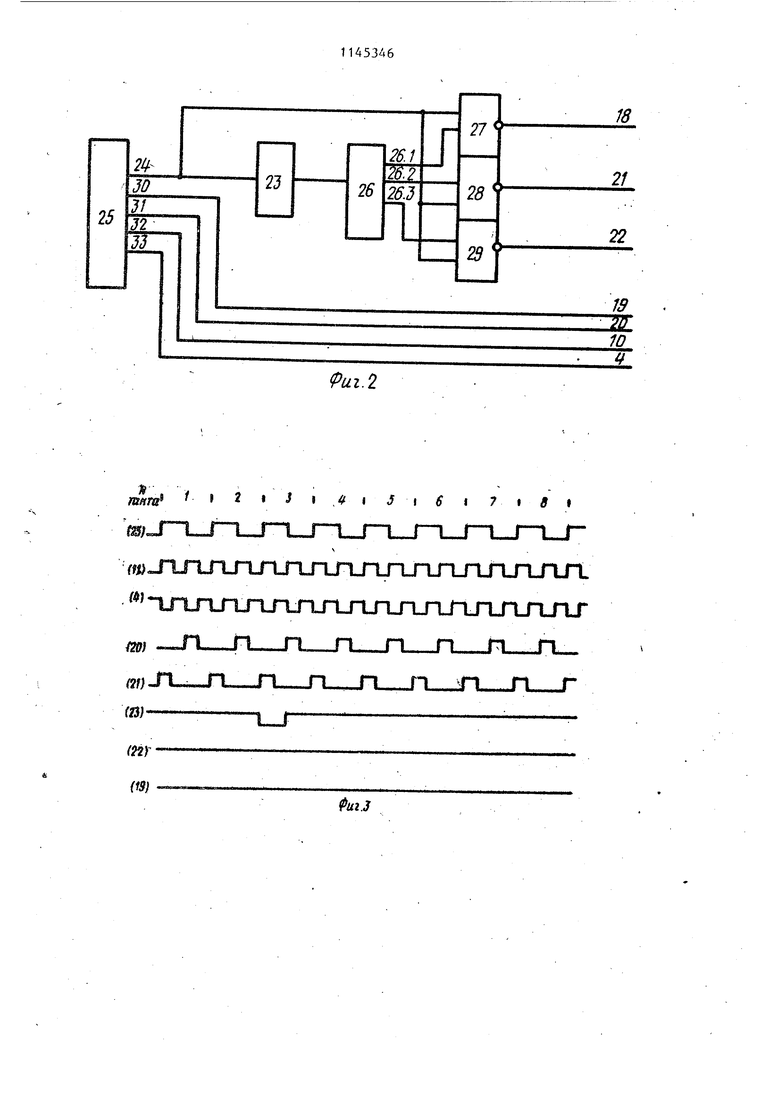

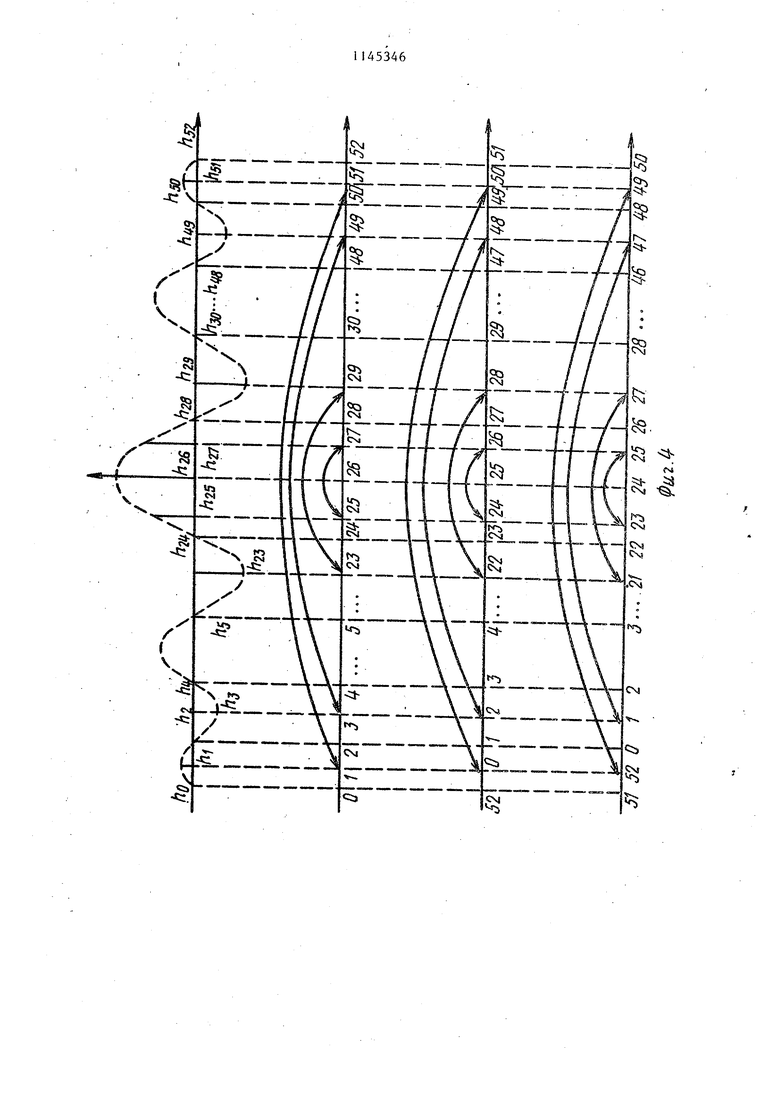

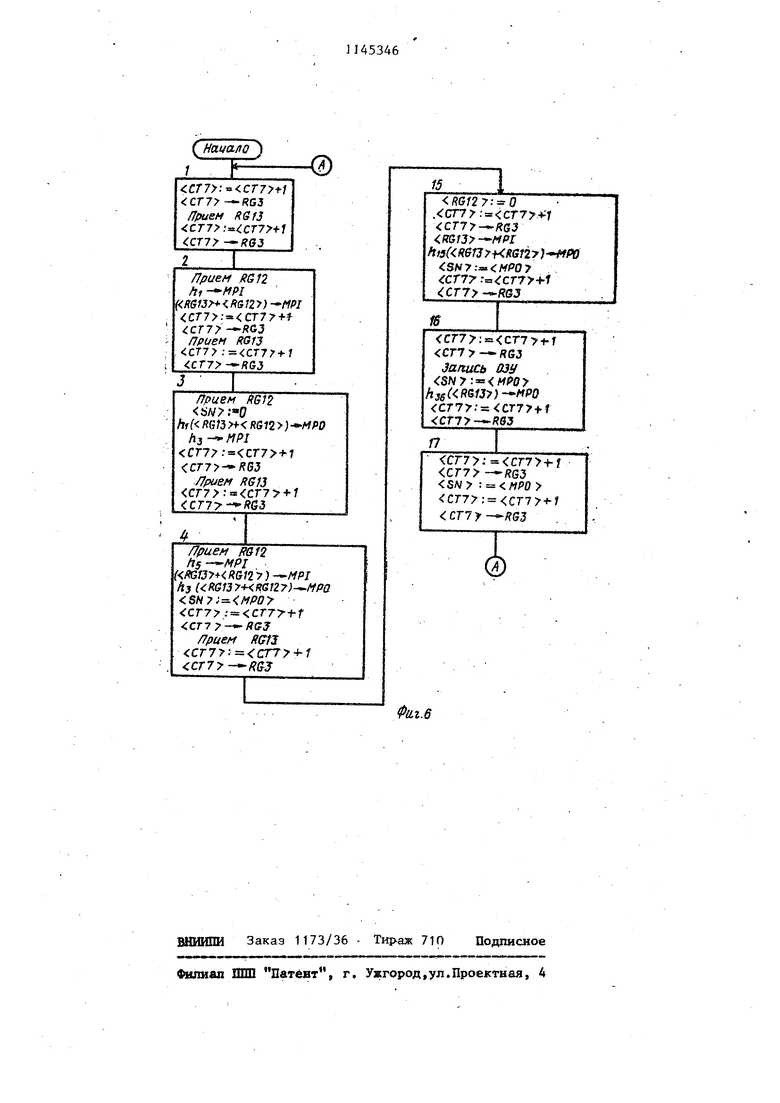

Изобретение относится к вычислительной технике и может быть исполь зовано в системах цифровой обработки радиолокационных5 сейсмических5 гидроакустических и других сигналов ИзвеГ-тен цифровой нерекурсивньй фильтр, содержащий блоки памяти входных отсчетов5 умножительj накопит ельньй сумматор Cl 1 Недостаток известного фильтра обусловлен низким быстродействием в случае симметрш-гных весовых |:оэффициентов. Наиболее близким по технической сущности к изобретению является фильтр5 содержащий блок памяти весовых коэффициентов, первый вход которого является входам записи коэффициентов фильтра,второй вход выход соединены соответственно с первы адресным счетчиком и входом первого регистра3 выход которого соединен с первым входом умножителя, соединенного своим выходом накопительного сумматора, выход которого соединей с цифроаналоговым преобразователем, два входа памяти входных отсчетов, первые входы которых соединены с вторым и третьим адресньгми счетчиками соответственно, при этом второй вход и вьпсод первого блока памяти входных отсчетов соединены с выходом второго и первым входом третьего регистроВу выход третьего регистра сое динен с входом второго регистра., а второй вход третьего регистра являет ся входом отсчетов входного сигнала фильтра5 четвертый и пятьй регистры и оумматорз первый и второй входы ко торого соединены с выходами со.ответственно третьего и четвертого регнст с вторЬй-1 входом умноров, а выход жителя, при этом первый и второй вхо ды пятого регистра соединены с входа ми соответственно второго и четвертого регистров, а второй вход и выход блока памяти входных отсчетов соединены соответственно с выходом пятого и входом четвертого регистров , Формула свертки, реализуемая циф ровым фильтром, имеет вид JL Ь, - весовые коэффнн иенты, а х - отсчеты входного сигнала„ Для реализации этого алгоритма необхомо, очевидно, N+1 обращений к памяти 62 входных отсчетов. Из формуоты видно, что входные отсчеты при вычислении каждого последующего выходного отсчета сдвигаются относительно весовых коэффициентов. В прототипе этот сдвиг осуществляется за счет того, что отсчет, считанньй в памяти по некоторому адресу, в следующем такте переписывается по адресу на единицу больше. Таким образом, на каждый отсчет входного сигнала приходится два обращения к памяти входных отсчетов - одно чтение и одна запись. В связи с этим в прототипе для дост.ижения максимальной производительности фильтра при заданных ограничения на входдщие в него узлы применены два блока памяти входных отсчетов чтОд во-первыхJ усложняет устройство управления и, во-вторых, требует дополнительных затрат оборудования на реализацию обрамления этих двух блоков памяти, например требует применения двух регистров , каж,аый из которых принимает данные с двух направлений. Вместе с тем, объем оборудования цифрового фильтра чожко уменьшить практически без сни- -жения его быстродействия, если на каждый входной отсчет сигнал обра1цаться к памяти входных отсчетов только один раз. т.е„ только читать входные данные без последующей их перезаписи,. Цель изобретения - упрощение цифрового фильтра (уменьшение его аппаратурных затрат). Поставленная цель достигается тем, что цифровой фильтр, содержащий блок памяти, информационный выход ,которого подключен к информационным входам первого и второго регистров, информационные выходы которых подключены соответственно к первому и второму входам сумматора, выход которого подключен к первому входу умножителя, выход которого подключен к входу накапливающего сумматора, выход .которого является информационным выходом фильтра, блок синхронизации, первьЙ5 второй, третий и четвертый выходы которого подключены соотвест-. венно к управляющему входу блока памяти, счетному входу первого счетчика адреса, установо шому входу перйого регистра и установочному входу накапх1ивающего сумматора, пятый выход блока синхронизации подключен к тактовым входам второго регистра и умножителя, шестой выход блока синхронизации подключен к тактовым входам первого регистра и накапливающего сумматора и счетному входу второго счетчика адреса, информационньй выход которого подключен к адресному входу блока постоянной памяти, информационный выход которого подключен к второму входу умно жителя, содержит блок памяти адресов и регистр адреса, причем информ ционный выход первого счетчика адре са подключен к адресному входу блока памяти адресов, йнформационньм выход которого подключен к инфо1 1ационному входу регистра адреса, информационный -выход которого подключ к адресному входу блока памяти, информационный вход которого является информационным входом фильтра, а се мой выход Блока синхронизации подключен к тактовому входу регистра адреса. При этом блок синхронизации содержит три элемента И-НЕ, дешифратор, счетчик и генератор тактовых импульсов, первый выход которого подключен к первым входам трех элементов И-НЕ и счетному входу счетчика, информационный выход .которого подключен к входу дешифратора, первый, второй и третий выходы которо го подключены к вторым входам соответственно первого, второго и третьего элементов И-НЕ, выходы которых, являются соответственно первым, третьим и четвертым выходами блока синхронизации, а второй, третий, четвертый и пятый выходы генер тора тактовых импульсов являются со ответственно пятым, шестым, вторым и седьмым выходами блока синхронизации. На фиг. 1 показана блок-схема предлагаемого цифрового фильтра; на фиг, 2 - то же, блока синхронизации на фиг. 3 - временная диаграмма работы блока синхронизации; на фиг.4 импульсная характеристика фильтра и диаграмма считьгоания данных из блок памяти входных отсчетов; на фиг. 5 организация данных в блоке памяти адресов; на фиг, 6 - граф-алгоритм работы блока синхронизации. Цифровой фильтр (фиг. 1) содержит блок 1 памяти (входных отсчетов информационный вход 2 фильтра, регистр 3 адреса, выход 4 блока 5 син хронизации, блок 6 памяти адресов, счетчик 7 адреса, информационный выход 8 и счетный вход 9, выход 10 блока синхронизации, регистры 11 и 12, сумматор 13, умножитель 14, блок 15 памяти (весовых коэффициентов), счетчик 16 адреса, накапливающий сзп матор 17, а также выходы 18-22 блока синхронизации. Блок синхронизации (фиг. 2) содержит счетчик 23, выход 24 генератора 25 тактовых импульсов, дешифратор 26, выходы которого 26.1, 26,2 и 26.3, элементы И-ВЕ 27, 28 и 29, выходы 30-33 генератора 25. Для иллюстрации работы устройства рассмотрим в качестве примера реализапию цифрового фильтра с импульсной характеристикой, представленной на фиг. 4, т.е. с общим числом N, равным 53 коэффициентам. В случае симметричной характеристики число нулевых коэффициентов составляет CN-1) /2, а общее число .ненулевых - (N-1)/2+1, т.е. равно 27, или с учетом симметрии характеристики число ненулевых коэффициентов по одну сторону от оси ординат составит 13 плюс один центральный. При таком числе ненул1евых коэффициентов можно получить затухание в полосе подавления не хуже 80 дБ. На фиг. 4, кроме импульсной характеристики фильтра, изображены также диаграммы, указьшающие порядок, в котором необходимо считьшать данные из блока 1 памяти входных отсчетов при вычислении трех последовательных выходных отсчетов. Согласно фиг. 4 из блока 1 памяти входных отсчетов в регистры 11 и 12 принимаются входные отсчеты, умножаемые на симметричные ненулевые коэффициенты импульсной характеристики. Цифры под горизонтальными прямыми обозначают адреса яче- ек блока 1 памяти входных отсчетов, из которых необходимо считьшать данные; дугами со стрелками соединены ячейки, содержимое которых необходимо суммировать на сумматоре 13. Закон изменения адресов при чтении из блока 1 памяти входных отсчетов описьшается следующей системой рекуррентных соотношений ()(NM) 2m Лт-1(.4„,.1)шо(К+1) ((()tncc(N+l| , m 1,... N/2-1 , где ei,- - содержимое ячейки блока 6 памяти с адресом i (,1,,. „ ,N) . Таким образом, ;в блоке 6 памяти адресов последовательно записаны (N+1 последовательность адресов 0,1, ,,., N. Рассмотрим вычисление i ro-результирующего отсчета фильтра-. Каждый цикл вычисления очередного отсч та результата состоит из 17-ти тактов синхросерии (11) генератора 25 см, диаграмму на фиг„ 2,,3)е На фиг„ представлен.граф-алгоритм работы блока 5. Номера оперативных вершин совпадают с номерами тактов работы устройства. При изображении алгорит ма приняты следующие обозначения -счетчик адреса; - регистр адреса 3; -регистр 115 -регистр 12; -входной каскад умножите--ля 14| выходной каскад умножителя 14| накопительный сумматор 17 j блок 1 памяти отсчетов; А содержимое узла А; Ьодержш4ому узла А присвои значение 5 равное содержи-рю му узла В| I содержимое узла А переслат в узел В, В первом такое счетчик 7-адреса по импульсу синхросерии 10 увеличивает свое состояние на единицу, из блока 6 памяти адресов по синхросерии 4 (диаграмма на фиг. 3) в регистр 3 адреса .принимается адрес Считанное по этому адресу изблока 1. памяти входных отсчетов чис ло х по сигналу 19 блока 5 принима ется в регистр 12, В этом же такте по синхросерии 10 счетчик адреса 7 изменяет свое состояние на единицу а из блока 6 памяти адресов в регистр 3 по сигналу4 принимается ад рес оС , По сигналу 20 в такте 2 в регистр .11 принимается число х читанное из блока 1 памяти входных отсчетов. Значения входных отсчетов, хранимые на регистрах 11 и 12, суммируются в такте 2 сумматором 13 и по сигналу 19 вычисленная сумма принимается на второй вход умножителя 14„ По этому же сигналу на первый вход умножителя 14 принимается значение коэффициента h, считанного из памяти коэффициентов 15 по адресу, задаваемому адресным счетчиком 16, на счетный вход которого подается синхросерия 20 генератора 25 (диаграмма на фиг, 3), По следующему импульсу синхросерии 19 (в такте 3) сформированное произведение у h( j ) (диаграмма на фиг, 4) принимается в выходной каскад умножителя 14, В первой половине такта 3 по сигналу 22 обнуляется ,тop 17 и в такте 4 по импульсу синхросерии 20 произведение у записывается в сумматор 17, Одновременно в такте 2 (диаграмма на фиг, 6) счетчик 7 адреса увеличивает свое состояние на единицу, в. регистр 3 адреса из блока 6 памяти адресов принимается адрес , по этому адресу из блока 1 памяти входных отсчетов в регистр 1Й прини }ается число X, , счетчик 7 вновь увеличивает не единицу свое состояние, а в регистр 3 принимается адрес с/з, по которому в такте З.из блока 1 памяти входных отсчетов в регистр 11 принимается число . Считанные в тактах 2 и 3 из блока 1 памяти входных отсчетов числа Хд и 3 такте 3 складываются на сумматоре 13 и по импульсз - синхросерии 19 принимаются на второй вход умножите ля 14. По этому же сигналу на первый вход умножителя 14 из блока 15 памяти коэффициентов принимается значение коэффициента h. Произведение () в такте 4. по импульсу синхросерии 19 принимается в выходной каскад умножителя 14. В такте 5 по импульсу синхросерии 20 в сумматор 17 принимается сумма вновь сформированного произведения у.с ранее накопленньм произведением у . Аналогичным образом устройство работает до такта 14. В такте 15, в отличие от предьщущйх (диаграммы на фиг. 4, 6), на центральньш коэффициент умножается не сумма двух входных отсчетов, а один отсчет , по этой причине в такте 15 на устаноиочньй вход регистра 11 подается

сигнал 21 обнуления блока 5. Таким образом, на второй вход умножителя 14 в такте 15 по импульсу син ;росерии 19 принимается содержимое регистра 12, т.е. входной отсчет х . В такте 16 произведение импульсом синхросерии 19 принимается в выходной каскад умножителя.

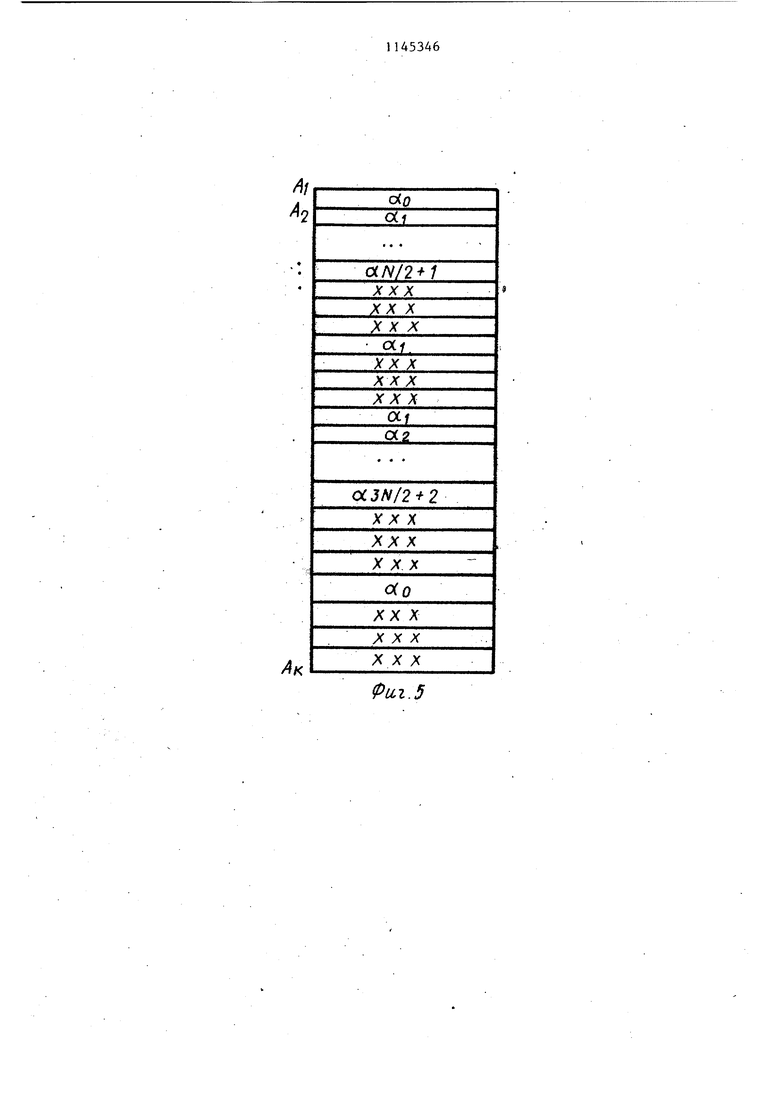

В такте 17 реэультирукадая сумма у. принимается в сумматор 17 и считывается из устройства. Таким образом, чтение из блока 1 памяти входных отсчетов происходит в течение первых 14 тактов. Запись очередного входного отсчета осуществляется в такте 16 сигналом 18 блока 5. Адрес, по которому осуществляется эта запись, также считывается из блока 6 памяти адресов. При этом, учитывая, что счетчик 7 адреса работает в непрерывном режиме и последний адрес о-м/г для чтения из блока 1 памяти входных отсчетов считывается в такте 14, после ячeЙJcи со словом (.d. в блоке 6 памяти адресов (фиг. 5) лежат три ячейки, содержимое которых безразлично для работы устройства, а затем расположена ячейка с адресом (.для записи входного отсчета и еще три безразличные ячейки, после которых начинается очередная последовательность адресов чтения из блока 1 памяти входных отсчетов в следующем цикле вычислений. Первьй адрес этой последовательности совпадает с последним адресом, по которому осуществлялась запись, поскольку на коэффициент h умножается сумма входного отсчета, пришедшего последним по времени, с входным отсчетом, находящимся в блоке 1 памяти входных от,счетов наибольшее время (диаграмма . на фиг. 4). Счетчик 7адреса имеет коэффициент пересчета, равный количеству слов в блоке 6 памяти адресов Поэтому по достижении значения А, (фиг. 5) он обнуляется (принимает значения ), при этом очередная последовательность адресов чтения начинается с оСо. В то же время последняя запись также осуществлялась по адресу о(,, следовательно, закон изменения последовательности адресов чтения и записи не нарушается.

В такте 1 следующего цикла вычислений из блока 6 памяти адресов по синхросерии 4 в регистр адреса 3 принимается оС2. Считанное по этому адресу из блока 1 памяти входных отсчетов число принимается в регистр 12. В этом же такте в регистр 3 при- нимается адрес Считанное по этому адресу число принимается в регистр 11, а сумма содержимых регистров 11 и 12 в такте 2 принимается на второй вход умножителя 14 и т.д.

Таким образом, предложенное выполнение цифрового фильтра упрощает его конструкцию и снижает аппаратные затраты.

Фиг.1

г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Цифровой фильтр | 1988 |

|

SU1555826A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1983 |

|

SU1149275A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

1. ЦИФРОВОЙ ФИЛЬТР, содержащий блок памяти, информационный выход которого подключен к информационным входам первого и второго регистров, информационные выходы которых подключены соответственно к первому и второму входам сумматора, выход которого подключен к первому входу умножителя, выход которого подключен к входу накапливающего сумматора, выход которого является информационньм выходом фильтра, блок синхронизации, первый, второй, третий и четвертый выходы которого подклю-. чены соответственно к управляющему входу блока памяти, счетному входу первого счетчика адреса, установочному входу первого регистра и установочному входу накапливающего сумматора, пятый выход блока синхро- низации подключен к тактовым входам второго регистра и умножителя, шестой выход блока синхронизации подключен к тактовым входам первого ре гистра и накапливающего сумматрра и счетному входу второго г.четчика адf й. .л-...« , ..-,, f te,::- УI реса, информационный выход которого подключен к адресному входу блока постоянной памяти, информационный выход которого подключен к второму ВХОДУ умножителя, отличающийся тем, что, с целью упрощения фильтра, он содержит блок памяти адресов и регистр адреса, причем информационный выход первого счетчика адреса подключен к адресному входу блока памяти адресов, информационный выход которого подключен к информационному входу регистра адреса, информационный выход которого подключен к адресному входу блока памяти, информационный вход которого является информационным входом (Л фипьтра, а седьмой выход блока синх-, ронизации подключен к тактовому входу регистра адреса. 2. Цифровой фильтр по п. Г, о т личающийся тем, что блок синхронизации содержит три элемента , И-НЕ, дешифратор, счетчик и генера ел тор тактовых ш пульсов, первый выход которого подключен к первым входам со первого, второго и третьего элементов И-НЕ и счетному входу счетчика, 4 информационный выход которого пода ключен к входу дешифратора, первый, второй и третий выходы которого подключены к вторым, входам соответственно первого, второго и третьего элементов И-НЕ, выходы которых являются соответственно первым, третьим и четверым выходами блока синхронизации, а второй, третий, четвертый и пятый выходы генератора тактовых импульсов являются соответственно пятым, шестым, вторым и седьмым выходами блока синхронизации.

J / I 2 I J 41 I J I tf I t 8 t

тнш

гш jijrnjanJTJTJTJnjTjn

njlJTJlJ-lJlJlJlJlJT.rL

)

fw;

U2.J

Гх

.

i:

fsl

чCN5 -С

И

См

Cs

,Css

«

СМ

«

f

Фаг.5

Hwa/iO }

Т

/

СГ77--RG3

ff/УиеМ RGtS

С7-7/-/ 6J

Прием KG 12

hi -W/ (KGJ3) K6}2f) C77 : « Cr77+f 4;СГ7 -«GJ

Прием KG13

CT7

Прием R5l

f R672 )

/Jj--/7W СГ77.

Лрием KGf3 СГ77-- / бЗ

/ г/гл- Л5 .

С лсо + /ге/2

Лз i RG13-7+ KG127)

:cr77.- cr7 --f-f сг77- /ге1

Лрием RGn СТ7У СГТ7- 1

15

0 ..Г /«JfJ -/ / r His(R6r37i KGn7}4 PO

. CT77

:сг7 -«6J

СГ7 -Я6Д

Janucb ОЗУ

SN7:« W 0

Ада яеш -««Р5 cr77. cr7.f

/7

СГ7 SW . MPD CT7y- KG3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой фильтр | 1975 |

|

SU636616A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-03-15—Публикация

1983-11-25—Подача