СП

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1501047A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Последовательное устройство для цифровой фильтрации | 1986 |

|

SU1339874A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Многоканальный накапливающий сумматор по произвольным модулям | 2024 |

|

RU2837596C1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1363248A1 |

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в системах цифровой обработки сигналов. Цель изобретения - повышение быстродействия. Фильтр содержит М вычислительных модулей (М - порядок фильтра), Каждый модуль состоит из умножителя 4, р-разрядного сумматора 5, т-раз- рядных элементов 6 и 7 задержки, р-разрядного элемента 8 задержки, одноразрядного элемента 9 задержки и т-раз- рядного сумматора 10.2 ил,

о ю

CJ

о

00

Фиг, 2

Изобретение относится к цифровой вычислительной технике и предназначено для использования в системах цифровой обработки сигналов.

Цель изобретения - повышение быстродействия цифрового фильтра.

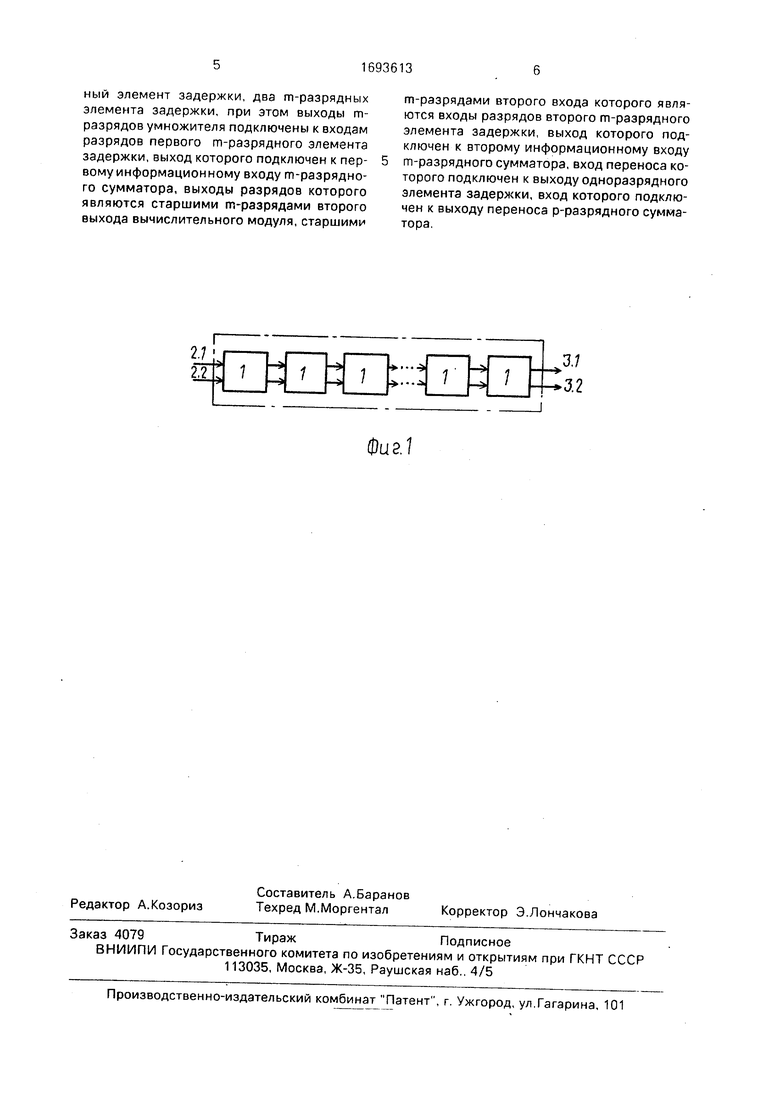

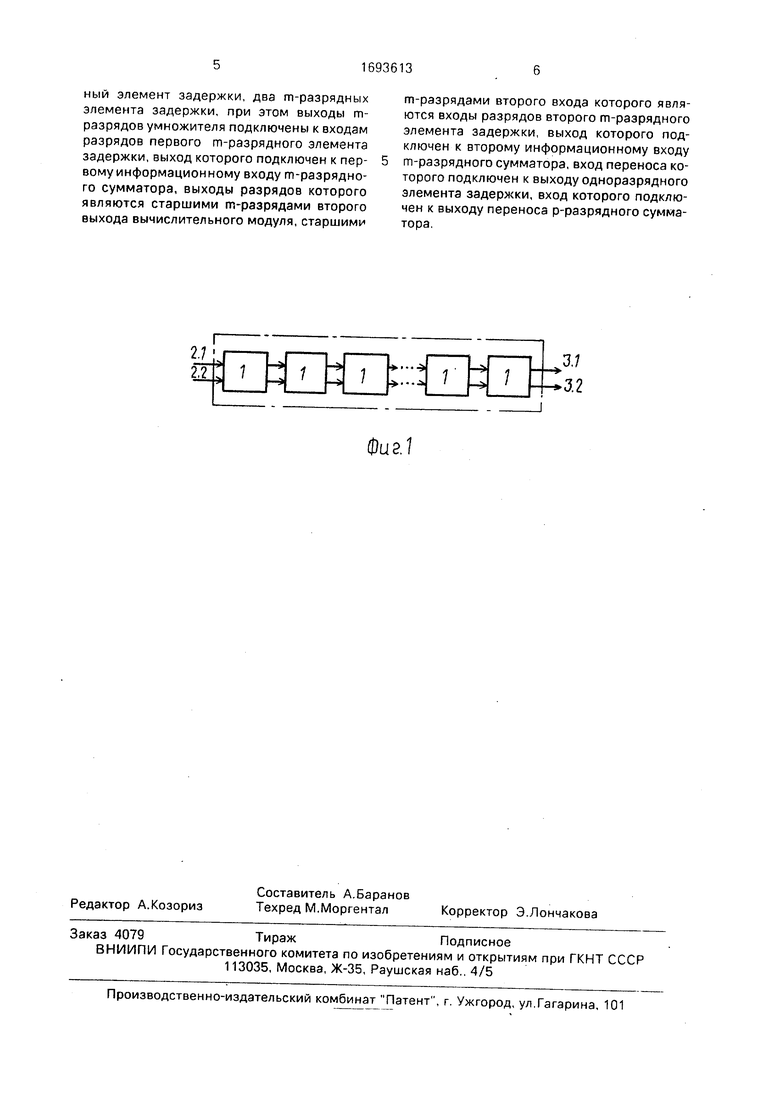

На фиг,1 изображена функциональная схема цифрового фильтра; на фиг.2 - функциональная схема вычислительного модуля цифрового фильтра.

Цифровой фильтр (фиг.1) содержит вычислительный модуль 1, информационные входы 2.1 и 2.2 и информационные выходы 3.1 и 3.2. Вычислительный модуль (фиг.2) цифрового фильтра 1 содержит умножитель 4, р-разрядный сумматор 5, т-разрядные элементы 6 и 7 задержки, р-разрядный элемент 8 задержки, одноразрядный элемент 9 задержки, m-разрядный сумматор 10, т- разрядный первый вход 11 модуля, т- разрядный второй вход 12 модуля, m-разрядный первый выход 13 модуля, т- разрядный второй выход 14 модуля.

Фильтр работает следующим образом.

Пусть по l-му тактовому импульсу (в i-й момент времени) на информационный вход 2.1 цифрового фильтра поступает входной отсчет xk (i, k - произвольные целые числа). Он устанавливается на входах умножителей 4 каждого j-ro модуля ,г). Синхронно с входным отсчетом на вторых входах каждого J-ro модуля устанавливаются р младших разрядов (k-1)-ro частичного результата. В i-м такте происходит умножение xk на соответствующие коэффициенты aj и суммирование р младших разрядов произведения xk aj и р младших разрядов (k-1)-ro частичного результата элемента 8 задержки. К концу 1-го такта суммирование сумматора 5 заканчивается и m старших разрядов нового k-ro частичного результата устанавливаются на втором выходе j-ro модуля. Пока идет суммирование в сумматоре 5 j-ro модуля (,г), в сумматоре 10 ()ro модуля суммируются старшие т разрядов произведения xk aj-i и старшие m разрядов (к-1)- го частичного результата. К концу i-ro.такта суммирование в сумматоре 10 заканчивается, и m старших разрядов (k-1)-ro частичного остатка устанавливаются на втором выходе 0-1)-го модуля. По (1+1)-му тактовому импульсу р младших разрядов k-ro частичного результата запоминаются в элементе 8 задержки и устанавливаются на соответствующих разрядах второго выхода j-й ячейки ,г), сигнал переноса из р-го разряда сумматора 5 запоминается в одноразрядном элементе 9 задержки и устанавливается на входе переноса сумматора 10. Одновремени

но с этим старшие m разрядов произведения xk aj и m старших разрядов (k-1)-ro частичного результата с выхода )-го модуля ,r запоминается соответственно в эле- 5 ментах 6 и 7 задержки. Кроме того, по (1+1)-му тактовому импульсу на вход 2.1 устройства поступает новый входной отсчет

Xk+1.

В (1+1)-м такте т старших разрядов про- 10 изведения xk aj суммируются с m старшими разрядами (k-1)-ro частичного результата в сумматоре 10 и в конце (i+1)-ro такта m разрядов k-ro частичного результата устанавливается на соответствующих разрядах 15 второго выхода j-ro модуля ().

Пока идет суммирование в сумматоре 10 j-ro модуля, в умножителе 4 формируется произведение хы aj и в сумматоре 5 р младших разрядов этого произведения суммируются с р младшими разрядами k-ro частичного результата с выхода 0 1Но модуля .г).

Дальнейшая работа предлагаемого фильтра проходит аналогично.

Формула изобретения

Цифровой фильтр, содержащий M (M - порядок фильтра) вычислительных модулей, причем первый и второй выходы m-ro (, M-1) вычислительного модуля подключены соответственно к первому и второму входам (m+1)-ro вычислительного модуля, первый и второй выходы М-го вычислительного модуля являются соответственно первым и вторым информационными выходами фильтра, первым и вторым информационными входами которого являются соответственно первый и второй входы первого вычислительного умножителя, р-разрядный сумматор и р-разрядный элемент задержки, при этом выходы р-разрядного умножителя подключены к первому входу р-разрядного сумматора, информационный выход которого подключен к входу р-разрядного элемента задержки, первый вход умножителя подключен к первому входу вычислительного модуля,р-разрядами второго входа которого являются разряды второго входа р-разрядного сумматора, первый выход вычислительного модуля соединен с его 50 первым входом, а выходы разрядов р-разрядного элемента задержки являются р-раз- рядами второго выхода вычислительного модуля, второй вход умножителя является входом задания коэффициента вычисли- 55 тельного модуля, отличающийся тем, что, с целью повышения быстродействия, в каждый вычислительный модуль введены гл- разрядный сумматор (р+гп - разрядность обрабатываемой информации), одноразряд20

25

30

35

40

45

ный элемент задержки, два т-разрядных элемента задержки, при этом выходы т- разрядов умножителя подключены к входам разрядов первого m-разрядного элемента задержки, выход которого подключен к первому информационному входу т-разрядно- го сумматора, выходы разрядов которого являются старшими m-разрядами второго выхода вычислительного модуля, старшими

m-разрядами второго входа которого являются входы разрядов второго т-разрядного элемента задержки, выход которого подключен к второму информационному входу m-разрядного сумматора, вход переноса которого подключен к выходу одноразрядного элемента задержки, вход которого подключен к выходу переноса р-разрядного сумматора.

Фиг.1

| Рабинер Л,Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| М.: Мир, 1978, с.607 | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-11-23—Публикация

1989-05-25—Подача