1 .13 Изобретение относится к вычислительной технике, в частности к приоритетным устройствам, и может быть использовано в вычислительных системах коллективного пользования, в узлах коммута1дии сетей ЭВМ для обслуживания запросов с минимизацией задержек.

Цель изобретения - расширение области применения устройства за счет внеочередного обслуживания запросов максимального приоритета.

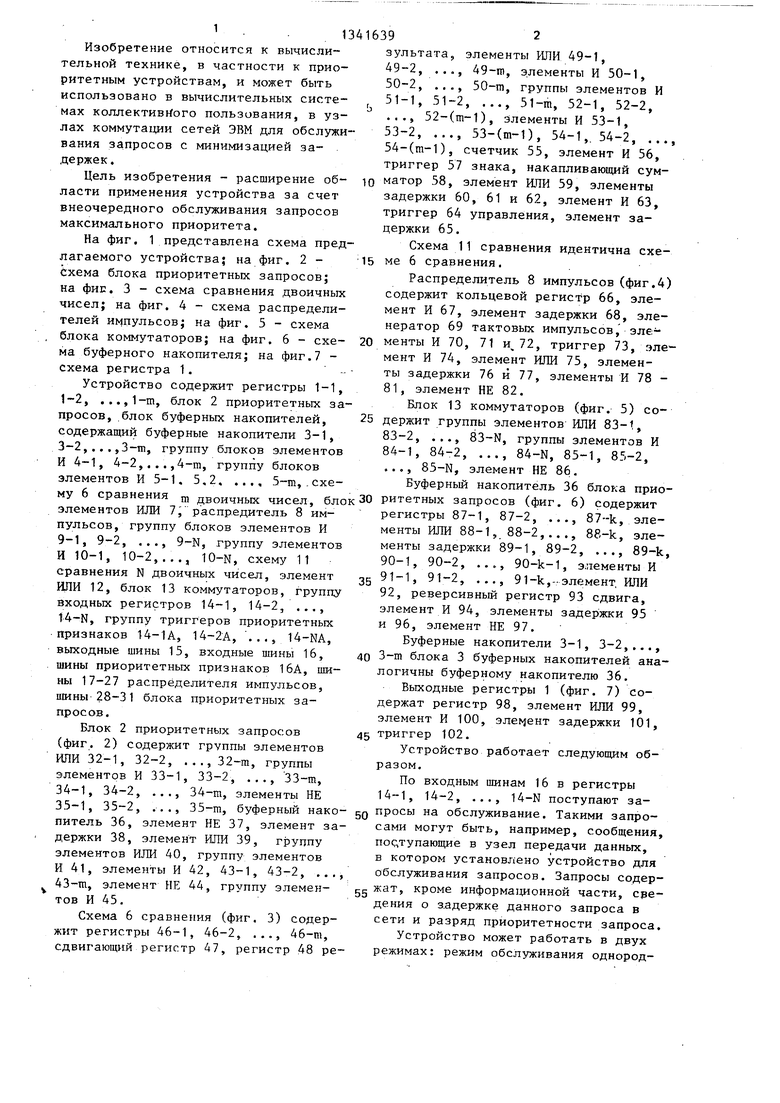

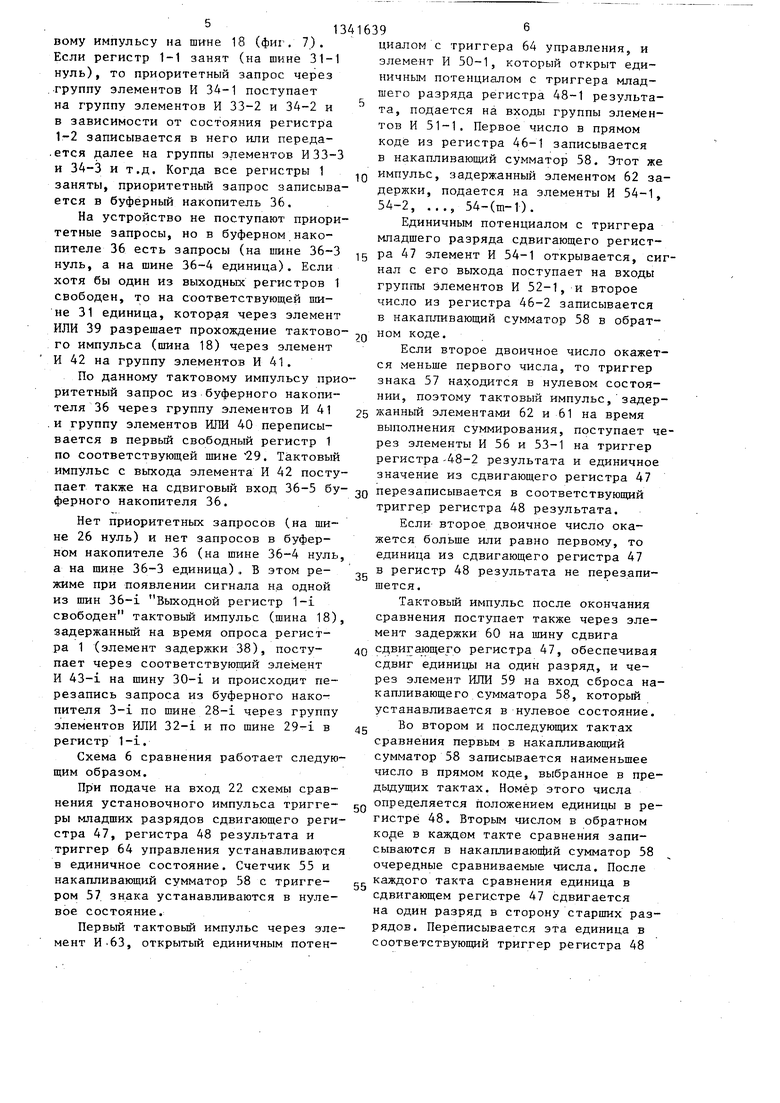

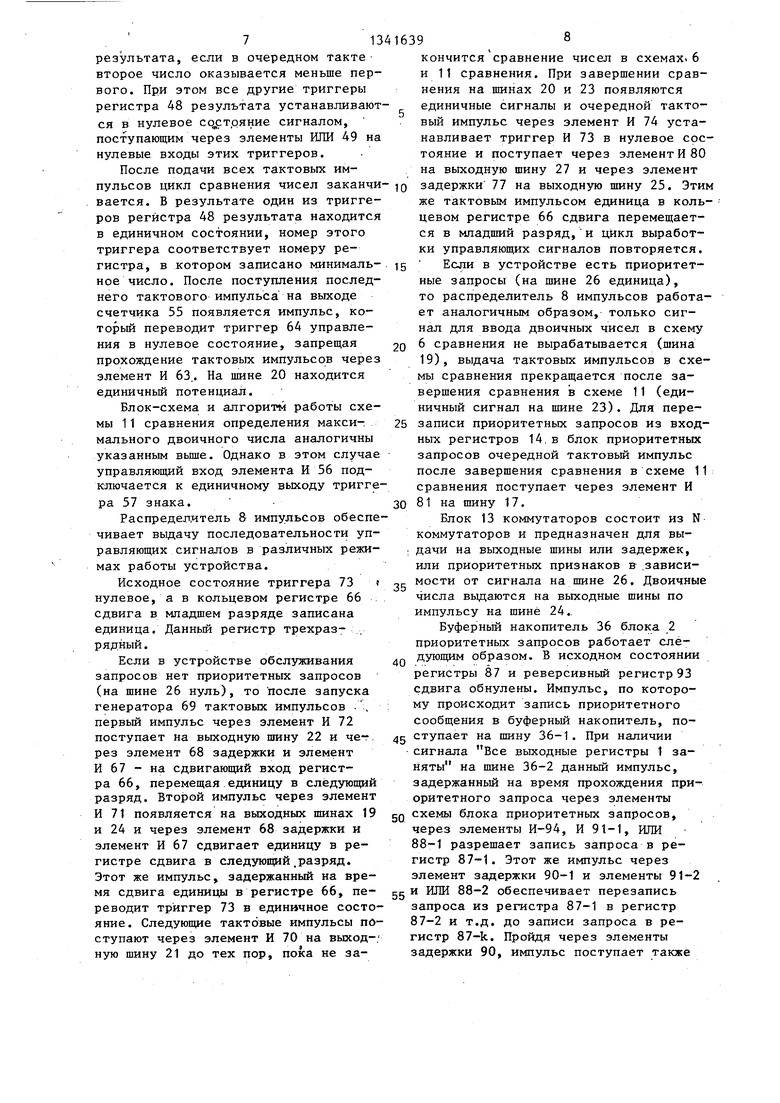

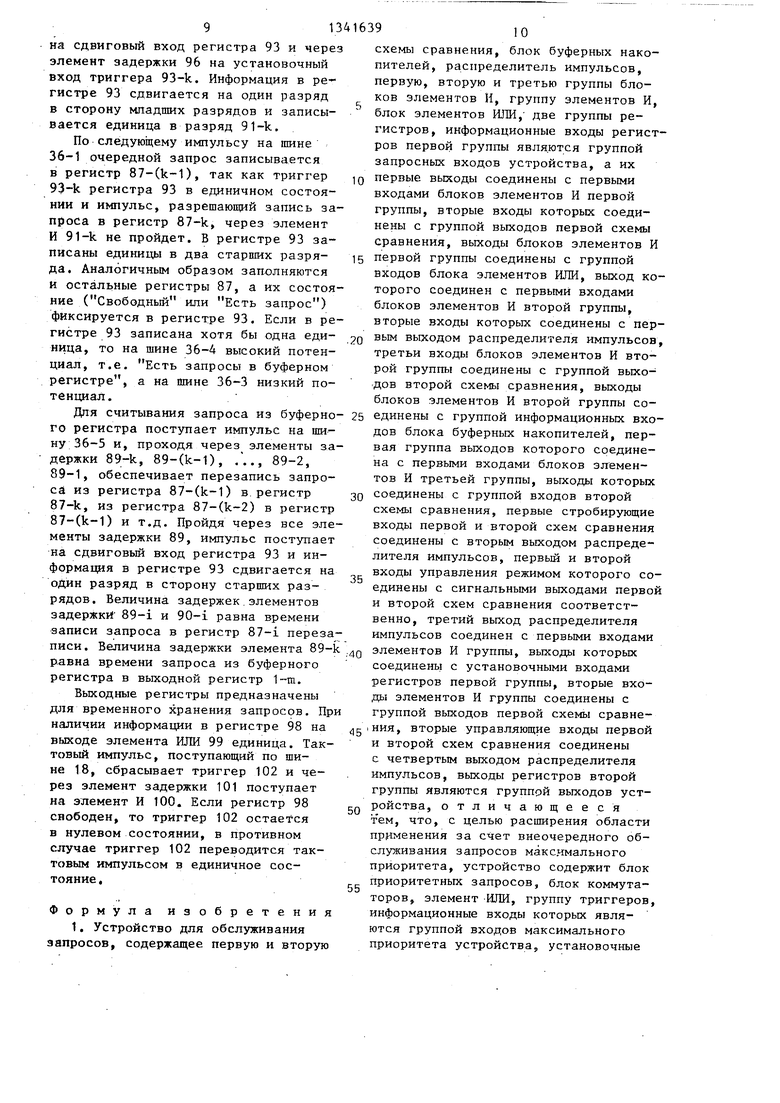

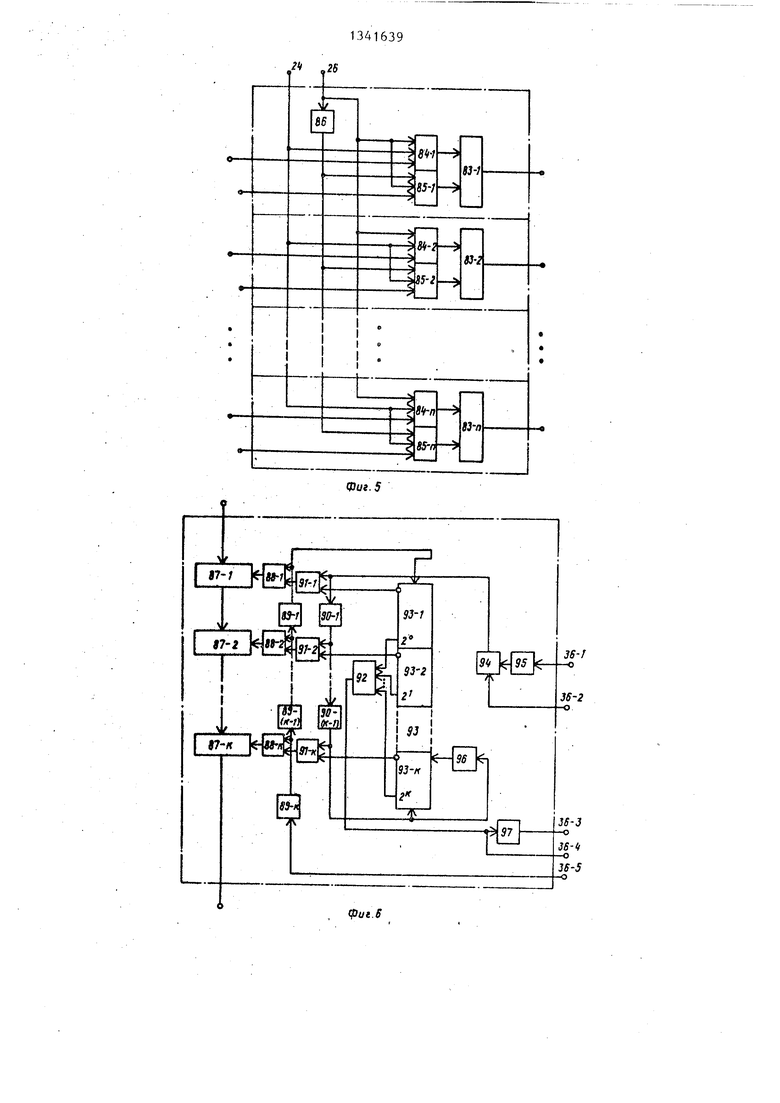

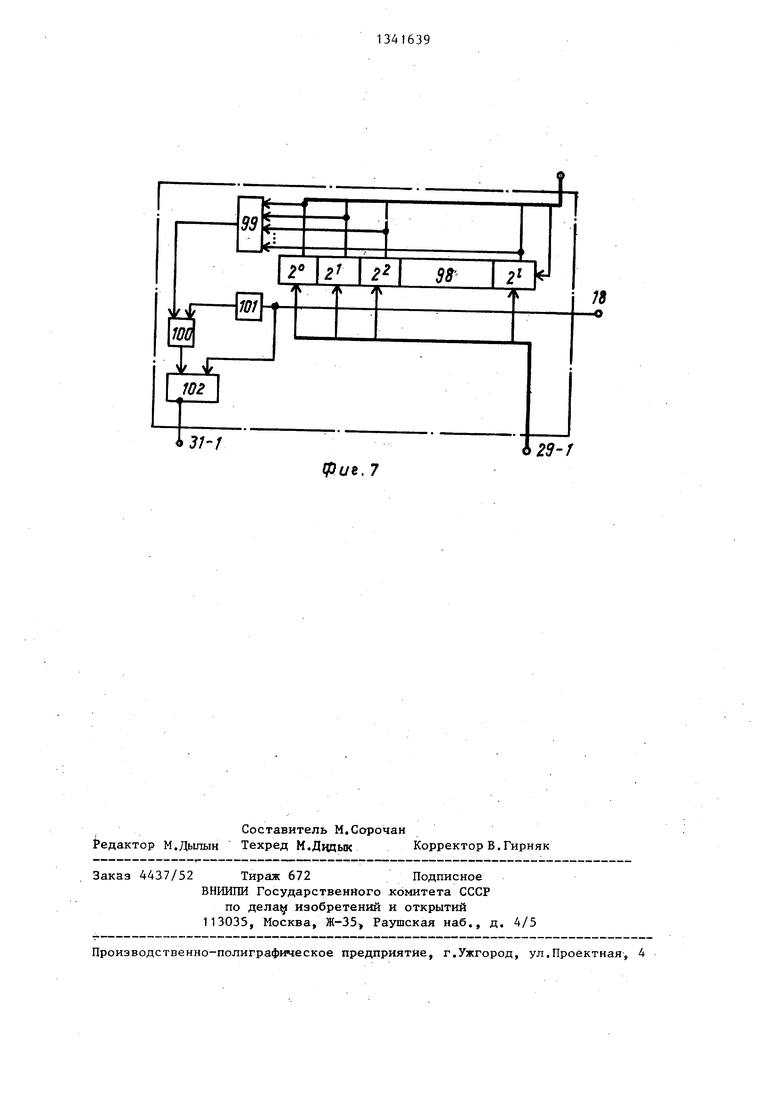

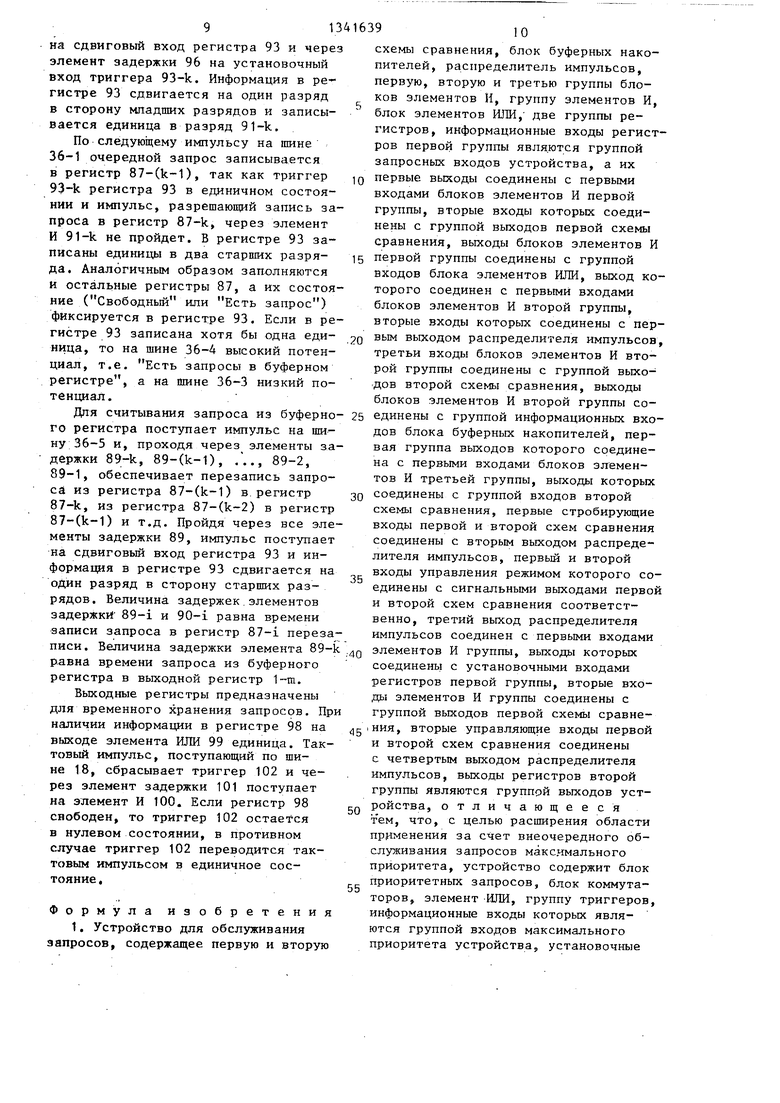

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 - Схема блока приоритетных запросов; на фиЕ. 3 - схема сравнения двоичных чисел; на фиг. 4 - схема распределителей импульсов; на фиг. 5 - схема блока коммутаторов; на фиг. 6 - схема буферного накопителя; на фиг.7 - схема регистра 1.

Устройство содержит регистры 1-1, 1-2, ...,1-т, блок 2 приоритетных запросов, блок буферных накопителей, содержащий буферные накопители 3-1, 3-2,...,3-т, группу блоков элементов И 4-1, 4-2,...,4-т, группу блоков элементов И 5-1. 5,25-т,- схему 6 сравнения „i двоичных чисел, бло элементов ИЛИ 7, распредитель 8 импульсов, группу блоков элементов И 9-1, 9-2, ..., 9-N, группу элементов И 10-1, 10-2,..., 10-N, схему 11 сравнения N двоичных чисел, элемент ИЛИ 12, блок 13 коммутаторов, группу входных регистров 14-1, 14-2, ..., 14-N, группу триггеров приоритетных признаков 14-1А, 14-2А, ..., 14-NA, выходные шины 15, входные шины 16, . шины приоритетных признаков 16А, шины 17-27 распределителя импульсов, шины 28-31 блока приоритетных запросов.

Блок 2 приоритетных запросов (фиг. 2) содержит группы элементов ИЛИ 32-1, 32-2, ..., 32-т, группы элементов И 33-1, 33-2, .,., 33-т, 34-1, 34-2, ..., 34-т, элементы НЕ 35-1, 35-2, ..., 35-т, буферный накопитель 36, элемент НЕ 37, элемент задержки 38, элемент ИЛИ 39, группу элементов ИЛИ 40, группу элементов И 41, элементы И 42, 43-1, 43-2, .., 43-т, элемент НЕ 44, группу элементов И 45,

Схема 6 сравнения (фиг. 3) содержит регистры 46-1, 46-2, ..,, 46-т, сдвигающий регистр 47, регистр 48 ре92

ультата, элементы ИЛИ 49-1, 9-2, ..., 49-in, элементы И 50-1, 0-2, .,., 50-т, группы элементов И 51-1, 51-2, ..., 51-т, 52-1, 52-2, ..., 52-(т-1), элементы И 53-1,

3-253-(т-1), 54-1,. 54-2

54-(т-1), счетчик 55, элемент И 56, риггер 57 знака, накапливающий сум- атор 58, элемент ИЛИ 59, элементы задержки 60, 61 и 62, элемент И 63, риггер 64 управления, элемент заержки 65.

Схема 11 сравнения идентична схе- ме 6 сравнения.

Распределитель 8 импульсов (фиг.4) содержит кольцевой регистр 66, элемент И 67, элемент задержки 68, эле- нератор 69 тактовых импульсов, эле- менты И 70, 71 , триггер 73, элемент И 74, элемент ИЛИ 75, элементы задержки 76 и 77, элементы И 78 - 81, элемент НЕ 82.

Блок 13 коммутаторов (фиг. 5) со- держит группы элементов ИЛИ 83-t, 83-2, ..., 83-N, группы элементов И 84-1, 84-2, ..., 84-N, 85-1, 85-2, ..., 85-N, элемент НЕ 86.

Буферный накопитель 36 блока прио- ритетных запросов (фиг. 6) содержит регистры 87-1, 87-2, ..., 87--k, элементы ИЛИ 88-1, 88-2,..., 88-k, элементы задержки 89-1, 89-2, ..., 89-k, 90-1, 90-2, ..., 90-k-1, элементы И 91-1, 91-2, ..., 91-k,-. элемент, ИЛИ 92, реверсивный регистр 93 сдвига, элемент И 94, элементы задержки 95 и 96, элемент НЕ 97.

Буферные накопители 3-1, 3-2,..., 3-т блока 3 буферных накопителей аналогичны буферному накопителю 36.

Выходные регистры 1 (фиг. 7) содержат регистр 98, элемент ИЛИ 99, элемент И 100, элемент задержки 101, триггер 102.

Устройство работает следующим образом.

По входным шинам 16 в регистры 14-1, 14-2, ..., 14-N поступают за- просы на обслуживание. Такими запросами могут быть, например, сообщения, поступающие в узел передачи данных, в котором установх ено устройство для обслуживания запросов. Запросы содер- жат, кроме информаи юнной части, сре- дения о аадержке данного запроса в сети и разряд приоритетности запроса.

Устройство может работать в двух режимах: режим обслуживания однород31

ного потока запросов; режим обслуживания неоднородного потока запросов.

При обслуживании однородного потока запросов во входных регистрах 14 нет приоритетных сообщений (триггеры приоритетных признаков в нулевом состоянии). После запуска устройства на выходе 22 распределителя импульсов появляется импульс, устанавливающий схемы сравнения двоичных чисел 6 и 1 в исходное состояние. При поступлении импульса на шину 24 информация о задержках запросов в сети из входных регистров 14 через блок 13 коммутаторов поступает в схему 11 срав

нения, а по импульсу на шине 19 дво- ичные числа, равные Количеству запросов в каждом из буферных накопителей 3-1, 3-2, ..., З-т, поступают на схему 6 сравнения через группу блоков элементов И 4-1, 4-2, ..., 4-т,

По тактовым импульсам, управляющим работой схем сравнения, сравниваются числа, записанные во входные регистры схем сравнения.

В схеме 6 сравнения определяется, в каком из буферных накопителей 3

меньше запросов. Единичный сигнал по- ЗО су на: шине 17 переписать приоритетявляется при этом на соответствующей выходной шине схемы сравнения.

Аналогичным образом, в схеме 11 сравнения определяется, в каком из входных регистров 14 находится запро с максимальной задержкой. При этом , на соответствующем выходе схемы.сравнения также появляется единичный сигнал.

После завершения операций сравнения в схемах сравнения по шинам 20 и 23 поступают сигналы, по которым распределителем 8 импульсов вырабатывается импульс (шина 27), разрешающи через соответствующие элементы И 9, ИЛИ 7 и И 5 переписать запрос с мак- сималь.ной задержкой из входного регистра 14 в буферный накопитель 3 с минимальной очередностью. После этого по шине 25 из распределителя импульсов данный входной регистр об- нуляется и в нег.о может быть записан вновь поступивший запрос.

Если в регистры 14 поступают запросы, имеющие одинаковые задержки, то их обслуживание производится по . порядку начиная с регистра 14-1, затем обрабатывается запрос, записанный в регистр 14-2 и т.д.

Если во всех буферных накопителях 3 одинаковые очереди, то запись запросов из входных регистров произво- дится в порядке 3-1, 3-2, ..., З-т.

Одновременно с приемом запросов из входных регистров в буферные накопители по мере освобождения выходных регистров 1 осуществляется перезапись запросов из буферных накопителей в выходные регистры через блок приоритетных запросов.

При обслуживании Неоднородного потока запросов во входных регистрах 14

имеют-ся приоритетные сообщения (в триггерах приоритетных приказов - единица).

Б этом случае на вьрсоде элемента ИЛИ 12 - единица и после запуска устройства, установки схем сравнения в сходное состояние по импульсу на ши- Не 24 разряды приоритета через блок 13 коммутаторов поступают на схему 11 равнения. В схеме сравнения опредеяется, в каком из входных регистров 14 находится приоритетньй запрос. При этом на соответствующем выходе блока сравнения появляется единичный сигнал, который разрешает по импуль5

ный запрос через соответствующую группу элементов И 9 и группу элементов ИШ 7 в свободный выходной регистр 1 или буферный накопитель блока 2 приоритетных запросов. Если приоритетных запросов несколько, то схема 11 сравнения обеспечивает последовательную вьщачу запросов из регистров 14-1, 14-2, ..., 14-N 0 и т.д. Блок 2 приоритетных запросов предназначен для према, хранения и вьщачи в выходные регистры 1 приоритетных запросов.

Блок приоритетных запросов (фиг.2) 5 работает следующим образом.

В устройстве имеются приоритетные запросы (на шине 26 - единица). В этом случае по сигналу.на шине 17 Записать приоритетньй запрос прио- 0 ритетный запрос через группу элементов И 45, группу элементов ИЛИ 40 поступает на группу элементов И 33-1 и 34-1. Если выходной регистр 1-1 свободен,- то на шине 33-1 единица 5 и приоритетный запрос через группу элементов И 33-1 и группу элементов ИЛИ 32-1 по шине 29-1 поступает в регистр 1-1. Опрос состояния выходных регистров 1 осуществляется по Такто5134

ому импульсу на шине 18 (фиг. 7). сли регистр 1-1 занят (на шине 31-1 нуль), то приоритетный запрос через группу элементов И 34-1 поступает на группу элементов И 33-2 и 34-2 и в зависимости от состояния регистра 1-2 записывается в него или переда- ется далее на группы элементов И 33-3 и 34-3 и т.д. Когда все регистры 1 заняты, приоритетный запрос записывается в буферный накопитель 36.

На устройство не поступают приоритетные запросы, но в буферном накопителе 36 есть запросы (на шине 36-3 нуль, а на шине 36-4 единица). Если хотя бы один из выходных регистров 1 свободен, то на соответствующей шине 31 единица, которая через элемент ИЛИ 39 разрешает прохождение тактового импульса (шина 18) через элемент И 42 на группу элементов И 41.

По данному тактовому импульсу приоритетный запрос из буферного накопителя 36 через группу элементов И 41 и группу элементов ИЛИ 40 переписывается в первый свободный регистр 1 по соответствующей шине 29. Тактовый импульс с выхода элемента И 42 поступает также на сдвиговый вход 36-5 буферного накопителя 36.

Нет приоритетных запросов (на шине 26 нуль) и нет запросов в буферном накопителе 36 (на шине 36-4 нуль, а на шине 36-3 единица)„ В этом режиме при появлении сигнала на одной из шин 36-i Выходной регистр 1-i свободен тактовый импульс (шина 18), задержанный на время опроса регистра 1 (элемент задержки 38), поступает через соответствующей элемент И 43-i на шину 30-i и происходит перезапись запроса из буферного накопителя 3-i по шине 28-i через группу элементов ИЛИ 32-i и по шине 29-i в регистр 1-i.

Схема 6 сравнения работает следующим образом.

При подаче на вход 22 схемы сравнения установочного импульса триггеры младших разрядов сдвигающего регистра 47, регистра 48 результата и триггер 64 управления устанавливаются в единичное состояние. Счетчик 55 и накапливающий сумматор 58 с триггером 57 знака устанавливаются в нулевое состояние.

Первый тактовый импульс через элемент И 63, открытый единичным потен

9

циалом с триггера 64 управления, и элемент И 50-1, который открыт единичным потенциалом с триггера младшего разряда регистра 48-1 результата, подается на входы группы элементов И 51-1. Первое число в прямом коде из регистра 46-1 записывается в накапливаюшкй сумматор 58. Этот же импульс, задержанный элементом 62 задержки, подается на элементы И 54-1, 54-2, ..., 54-(in-1).

Единичным потенциалом с триггера мпадшего разряда сдвигающего регист- ра 47 элемент И 54-1 открывается, сигнал с его выхода поступает на входы группы элементов И 52-1, и второе число из регистра 46-2 записывается в накапливающий сумматор 58 в обратном коде.

Если второе двоичное число окажется меньше первого числа, то триггер знака 57 находится в нулевом состоянии, поэтому тактовый импульс, задер- жанный элементами 62 и 61 на время выполнения суммирования, поступает через элементы И 56 и 53-1 на триггер регистра -48-2 результата и единичное значение из сдвигающего регистра 47 перезаписывается в соответствующий триггер регистра 48 результата.

Если второе двоичное число окажется больше или равно первому, то единица из сдвигающего регистра 47 в регистр 48 результата не перезапишется.

Тактовый импульс после окончания сравнения поступает также через элемент задержки 60 на шину сдвига сдвигающего регистра 47, обеспечивая сдвиг единицы на один разряд, и через элемент ИЛИ 59 на вход сброса накапливающего сумматора 58, который устанавливается в нулевое состояние.

Во втором и последующих тактах сравнения первым в накапливающий сумматор 58 записывается наименьшее число в прямом коде, выбранное в предыдущих тактах. Номер этого числа определяется положением единицы в регистре 48. Вторым числом в обратном коре в каждом такте сравнения записываются в накагшиваюп1ий сумматор 58 очередные сравниваемые числа. После каждого такта сравнения единица в сдвигающем регистре 47 сдвигается на один разряд в сторону старших разрядов. Переписывается эта единица в соответствуюш ий триггер регистра 48

результата, если в очередном такте второе число оказывается меньше первого. При этом все другие триггеры регистра 48 результата устанавливаются в нулевое состояние сигналом, поступающим через элементы ИЛИ 49 на нулевые входы этих триггеров.

После подачи всех тактовых импульсов цикл сравнения чисел заканчи- Q задержки 77 на выходную шину 25. Этим

вается. В результате один из триггеров регистра 48 результата находится в единичном состоянии, номер этого триггера соответствует номеру регистра, в котором записано минимальное число. После поступления последнего тактового импульса на выходе счетчика 55 появляется импульс, который переводит триггер 64 управления в нулевое состояние, запрещая прохождение тактовых импульсов через элемент И 63.. На шине 20 находится единичный потенциал.

Блок-схема и алгоритм работы схемы 11 сравнения определения максимального двоичного числа аналогичны указанным вьш1е. Однако в этом случае управляющий вход элемента И 56 подключается к единичному выходу триггера 57 знака.

Распределитель 8 импульсов обеспечивает вьщачу последовательности управляющих сигналов в различных режимах работы устройства.

Исходное состояние триггера 73 t нулевое, а в кольцевом регистре 66 сдвига в мпадшем разряде записана единица. Данньш регистр трехраз- . рядный.

Если в устройстве обслуживания запросов нет приоритетных запросов (на шине 26 нуль), то после запуска генератора 69 тактовых импульсов . , ; первый импульс через элемент И 72 поступает на выходную шину 22 и че-. рез элемент 68 задержки и элемент И 67 - на сдвигающий вход регистра 66, перемещая единицу в следующий разряд. Второй импульс через элемент И 71 появляется на выходных шинах 19 и 24 и через элемент 68 задержки и элемент И 67 сдвигает единицу в регистре сдвига в следующий.разряд. Этот же импульс, задержанный на вреже тактовым импульсом единица в к цевом регистре 66 сдвига перемеща ся в младший разряд, и цикл выраб ки управляющих сигналов повторяет

15 Если в устройстве есть приорит ные запросы (на шине 26 единица), то распределитель 8 импульсов раб ет аналогичным обр азом, только си нал для ввода двоичных чисел в сх

20 6 сравнения не вырабатывается (ши 19), выдача тактовых импульсов в мы сравнения прекращается после з вершения сравнения в схеме 11 (ед ничный сигнал на шине 23). Для пе

25 записи приоритетных запросов из в ных регистров 14. в блок приоритет запросов очередной тактовый импул после завершения сравнения в схем сравнения поступает через элемент

30 81 на шину 17.

Блок 13 коммутаторов состоит и коммутаторов и предназначен для вы 1 Дачи на выходные шины или задержек или приоритетных признаков в .завис мости от сигнала на шине 26. Двоич числа выдаются на выходные шины по импульсу на шине 24..

Буферньгй накопитель 36 блока 2 приоритетных запросов работает сле дующим образом. В исходном состоян

регистры 87 и реверсивный регистр сдвига обнулены. Импульс, по котор му происходит запись приоритетного сообщения в буферный накопитель, п ступает на шину 36-1. При наличии

35

40

45

50

сигнала Все выходные регистры 1 з няты на шине 36-2 данный импульс, задержанный на время прохождения п оритетного запроса через элементы схемы блока приоритетньпс запросов, через элементы И-94, И 91-1, ИЛИ 88-1 разрешает запись запроса в ре гистр 87-1. Этот же импульс через элемент задержки 90-1 и элементы 9

мя сдвига единицы в регистре 66, пе- ggи ИЛИ 88-2 обеспечивает перезапись реводит триггер 73 в единичное состо- запроса из регистра 87-1 в регистр яние. Следующие тактовые импульсы поступают через элемент И 70 на выход-.

87-2 и т.д. до записи запроса в регистр 87-k. Пройдя через элементы задержки 90, импульс поступает такж

ную шину 21 до тех пор, пока не закончится сравнение чисел в схемах.6 и 11 сравнения. При завершении сравнения на шинах 20 и 23 появляются единичные сигналы и очередной тактовый импульс через элемент И 74 устанавливает триггер И 73 в нулевое состояние и поступает через элемент И 80 на выходную шину 27 и через элемент

же тактовым импульсом единица в кольцевом регистре 66 сдвига перемещается в младший разряд, и цикл выработки управляющих сигналов повторяется.

5 Если в устройстве есть приоритетные запросы (на шине 26 единица), то распределитель 8 импульсов работает аналогичным обр азом, только сигнал для ввода двоичных чисел в схему

0 6 сравнения не вырабатывается (шина 19), выдача тактовых импульсов в схемы сравнения прекращается после завершения сравнения в схеме 11 (единичный сигнал на шине 23). Для пере5 записи приоритетных запросов из входных регистров 14. в блок приоритетных запросов очередной тактовый импульс после завершения сравнения в схеме 11 сравнения поступает через элемент И

0 81 на шину 17.

Блок 13 коммутаторов состоит из N коммутаторов и предназначен для вы- 1 Дачи на выходные шины или задержек, или приоритетных признаков в .зависимости от сигнала на шине 26. Двоичные числа выдаются на выходные шины по импульсу на шине 24..

Буферньгй накопитель 36 блока 2 приоритетных запросов работает следующим образом. В исходном состоянии

регистры 87 и реверсивный регистр 93 сдвига обнулены. Импульс, по которому происходит запись приоритетного сообщения в буферный накопитель, поступает на шину 36-1. При наличии

5

0

5

0

сигнала Все выходные регистры 1 заняты на шине 36-2 данный импульс, задержанный на время прохождения приоритетного запроса через элементы схемы блока приоритетньпс запросов, через элементы И-94, И 91-1, ИЛИ 88-1 разрешает запись запроса в регистр 87-1. Этот же импульс через элемент задержки 90-1 и элементы 91-2

и ИЛИ 88-2 обеспечивает перезапись запроса из регистра 87-1 в регистр

87-2 и т.д. до записи запроса в регистр 87-k. Пройдя через элементы задержки 90, импульс поступает также

913

на сдвиговый вход регистра 93 и через элемент задержки 96 на установочный вход триггера 93-k. Информация в регистре 93 сдвигается на один разряд в сторону младших разрядов и записывается единица в разряд 91-k.

По следующему импульсу на 1пине 36-1 очередной запрос записывается в регистр 87-(k-1), так как триггер 93-k регистра 93 в единичном состоянии и импульс, разрешающий запись запроса в регистр 87-k, через элемент И 91-k не пройдет. В регистре 93 записаны единицы в два старших разряда. Аналогичным образом заполняются и остальные регистры 87, а их состояние (Свободный или Есть запрос) фиксируется в регистре 93. Если в регистре 93 записана хотя бы одна единица, то на шине 36-4 высокий потенциал, т.е. Есть запросы в буферном регистре, а на шине 36-3 низкий потенциал.

Дпя считывания запроса из буферного регистра поступает импульс на шину; 36-5 и, проходя через элементы задержки 89-k, 89-(k-1), ..., 89-2, 89-1, обеспечивает перезапись запроса из регистра 87-(k-1) в.регистр 87-k, из регистра 87-(k-2) в регистр 87-(k-1) и т.д. Пройдя через все элементы задержки 89, импульс поступает на сдвиговый вход регистра 93 и информация в регистре 93 сдвигается на один разряд в сторону старших разрядов. Величина задержек.элементов задержки 89-i и 90-i равна времени записи запроса в регистр 87-i перезаписи. Величина задержки элемента 89-k равна времени запроса из буферного регистра в выходной регистр 1--т.

Выходные регистры предназначены для временного хранения запросов. Пр наличии информации в регистре 98 на выходе элемента ИЛИ 99 единица. Тактовый импульс, поступающий по шине 18, сбрасывает триггер 102 и через элемент задержки 101 поступает на элемент И 100. Если регистр 98 свободен, то триггер 102 остается в нулевом состоянии, в противном случае триггер 102 переводится тактовым импульсом в единичное состояние ,

Формула изобретения

1, Устройство для обслуживания запросов, содержащее первую и вторую

1639

10

схемы сравнения, блок буферных накопителей, распределитель импульсов, первую, вторую и третью группы блоков элементов И, группу элементов И, блок элементов ИЛИ, две группы регистров, информационные входы регистров первой группы являются группой запросных входов устройства, а их

первые выходы соединены с первыми входами блоков элементов И первой группы, вторые входы которых соединены с группой выходов первой схемы сравнения, выходы блоков элементов И

первой группы соединены с группой

входов блока элементов ИЛИ, вькод которого соединен с первыми входами блоков элементов И второй группы, вторые входы которых соединены с первым выходом распределителя импульсов, третьи входы блоков элементов И второй группы соединены с группой выхо- дов второй схемы сравнения, выходы блоков элементов И второй группы соединены с группой информационных входов блока буферных накопителей, первая группа выходов которого соединена с первыми входами блоков элементов И третьей группы, выходы которых

соединены с группой входов второй схемы сравнения, первые стробирующие входы первой и второй схем сравнения соединены с вторым выходом распределителя импульсов, первый и второй

входы управления режимом которого со„

единены с сигнальными выходами первой

и второй схем сравнения соответственно, третий выход распределителя импульсов соединен с первыми входами

элементов И группы, выходы которых соединены с установочными входами регистров первой группы, вторые входы элементов И группы соединены с группой выходов первой схемы сравне|НИя, вторые управляющие входы первой и второй схем сравнения соединены с четвертым выходом распределителя импульсов, выходы регистров второй группы являются группой выходов устройства, отличающееся

тем, что, с целью расширения области применения за счет внеочередного обслуживания запросов максимального приоритета, устройство содержит блок приоритетных запросов, блок коммутаторов, элемент ИЛИ, группу триггеров, информационные входы которых являются группой входов максимального приоритета устройства, установочные

входы триггеров группы соединены с выходами группы элементов И, прямые выходы триггеров группы соединеий с первой группой информационных входов блока коммутаторов и входами элемента ИЛИ, выход которого соединен с первым управляющим входом блока коммутаторов , входами пуска блока приоритетных запросов и распределителя импульсов, вторая группа информационных входов блока коммутаторов соединена с инверсными выходами триггеров группы, второй управляющий вход блока коммутаторов соединен с пятым выходом распределителя импульсов, шестой и седьмой вькоды которого соединены соответственно с первым и вторым входами выбора режима блока приори- тетных запросов, стробирующий вход : которого соединен с выходом блока элементов ИЖ, первая группа выходов блока приоритетных запросов соедине- на с группой входов сброса блока буход которого соединен с первым входом буферного накопителя и первыми входами элементов И третьей группы выходы которых соединены с группой входов второго элемента ИЛИ, выходы элементов НЕ группы соединены с пер выми входами элементов И четвертой группы, выход второго элемента ШШ Q соединен с вторыми входами первых

элементов И первой и четвертой груп выход i-ro элемента И первой группы

(,

(М число запросных вхо

15

20

дов устройства) соединен с первым входо,м i-ro элемента ИЛИ группы, вы ход j-ro элемента И четвертой групп ((M-1) соединен с вторыми входа ми (j-fl)-x элементов И первой и чет вертой групп, выход М-го элемента И четвертой группы соединен с вторым входом буферного накопитедя, информ ционный выход которого соединен с вторыми входами элементов И третьей группы, вход пуска блока приоритетн

30

ферных накопителей, вторая группа вы- 25 запросов соединен с входом элемен- ходов блока приоритетных запросов соединена с информационными входами регистров второй группы, вторые выходы которых соединены с группой ответных входов блока приоритетных запросов, входы сброса регистров второй группы соединены с седьмым выходом распределителя импульсов, а их вторые выходы являются группой выходов устройства, вторые входы блоков элементов И третьей группы соединены с восьмым выходом распределителя импульсов, вторая группа выходов блока буферных накопителей соединена с группой запросных входов блока прио35

40

та НЕ, выход которого соединен с вт рым входом первого элемента И и вто рыми входами элементов И второй гру пы, выходы которых являются первой группой выходов блока приоритетных запросов, первый вход выбора режима блока приоритетных запросов соедине с первым входом третьего элемента И выход которого соединен с вторым вх дом второго элемента ИЛИ, второй вх -выбора режима блока приоритетных за просов соединен с входом элемента з держки, выход которого соединен с третьими входами элементов И.второй группы и третьим входом первого эле мента И, четвертый вход которого со единен с вторым сигнальным выходом буферного накопителя, группа выходо которого соединен с четвертьми вход ми элементов И второй группы, групп запросных входов блока приоритетных запросов соединена с вторыми входами элементов РШИ группы, выходы которых соединены с второй группой выходов блока приоритетных запросов, выход первого элемента НЕ соединен с треть им входом буферного накопителя, стро бирующий вход блока приоритетных запросов соединен с первым входом трет его элемента И, второй вход которого является четвертым входом блока прио ритетных запросов.

ритетных запросов. I

2, Устройство по п. 1, о т л и- чающееся тем, что блок прио- ритетных запросов содержит четыре группы элементов И, группу элементов ШШ, буферный накопитель, три элемента И, два элемента ИЛИ, группу элементов НЕ, Два элемента НЕ и элемент задержки, причем группа ответных входов блока приоритетных запросов соединена с входами элементов НЕ группы, первыми входами элементов И первой и второй групп и группой входов первого элемента ИЛИ, выход которого соединен с-входом первого элемента НЕ и первым входом первого элемента И.

41639 2

ход которого соединен с первым входом буферного накопителя и первыми входами элементов И третьей группы, выходы которых соединены с группой входов второго элемента ИЛИ, выходы элементов НЕ группы соединены с первыми входами элементов И четвертой группы, выход второго элемента ШШ Q соединен с вторыми входами первых

элементов И первой и четвертой групп, выход i-ro элемента И первой группы

(,

(М число запросных вхо

дов устройства) соединен с первым входо,м i-ro элемента ИЛИ группы, вы- ход j-ro элемента И четвертой группы ((M-1) соединен с вторыми входами (j-fl)-x элементов И первой и четвертой групп, выход М-го элемента И четвертой группы соединен с вторым входом буферного накопитедя, информационный выход которого соединен с вторыми входами элементов И третьей группы, вход пуска блока приоритетных

запросов соединен с входом элемен-

та НЕ, выход которого соединен с вторым входом первого элемента И и вторыми входами элементов И второй группы, выходы которых являются первой группой выходов блока приоритетных запросов, первый вход выбора режима блока приоритетных запросов соединен с первым входом третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, второй вход выбора режима блока приоритетных запросов соединен с входом элемента задержки, выход которого соединен с третьими входами элементов И.второй группы и третьим входом первого элемента И, четвертый вход которого соединен с вторым сигнальным выходом буферного накопителя, группа выходов которого соединен с четвертьми входами элементов И второй группы, группа запросных входов блока приоритетных запросов соединена с вторыми входами элементов РШИ группы, выходы которых соединены с второй группой выходов блока приоритетных запросов, выход первого элемента НЕ соединен с третьим входом буферного накопителя, стробирующий вход блока приоритетных запросов соединен с первым входом треть его элемента И, второй вход которого является четвертым входом блока приоритетных запросов.

rfTQ y-/i / -r ia r -lib

UrrnCEED

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для моделирования гибких автоматизированных производственных систем | 1987 |

|

SU1439615A2 |

| Устройство для моделирования вычислительных систем | 1985 |

|

SU1272339A1 |

| Устройство для сопряжения абонентского пункта с цифровой вычислительной машиной | 1980 |

|

SU941981A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1416978A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для обучения | 1980 |

|

SU985814A1 |

Изобретение относится к вычислительной технике, в частности к приоритетным устройствам, и может быть использовано в вычислительных системах коллективного пользования, в узлах коммутации сетей ЭВМ для обслуживания запросов с минимизацией задержек. Цель изобретения - расширение области применения устройства за счет внеочередного обслуживания запросов максимального приоритета. Устройство для обслуживания запросов содержит две схемы сравнения, блок бу- ферньпс накопителей, распределитель импульсов, три группы блоков элементов И, группу элементов И, блок элементов ИЖ, две группы регистров, блок приоритетных запросов, блок коммутаторов, элемент ИЛИ и группу триггеров. Устройство обеспечивает обслуживание как однородного,.так и неоднородного потока запросов. При обслуживании однородного потока запросов минимизируются временные задержки путем анализа времени пребывания запросов в системе и передача их на обслуживание на один из регистров с учетом длин очередей к каналам обслуживания. При обслуживании неоднородного потока запросов приоритетные запросы независимо от времени их пребывания в системе обслуживаются вне очереди с постановкой их на обслуживание в начало очереди. 1 з.п. ф-лы, 7 ил. (Л СО 4 tEOlL, Ob К

21 2 /5 Г7 25

Фиг Л

cput.S

фиъ. 7

| Устройство для обслуживания запросов в порядке поступления | 1980 |

|

SU922744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обслуживания запросов | 1984 |

|

SU1203529A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-30—Публикация

1986-04-11—Подача