133

Изобретение относится к вычисли- ; тельной технике, в частности к уст- ройствам ттравления обменом с внешней памятью, и может быть использовано для реализации интерфейса с внешней памятью в вычиспительных комплексах.

Целью изобретения является сокращение среднего времени обмена с внешней памятью,.

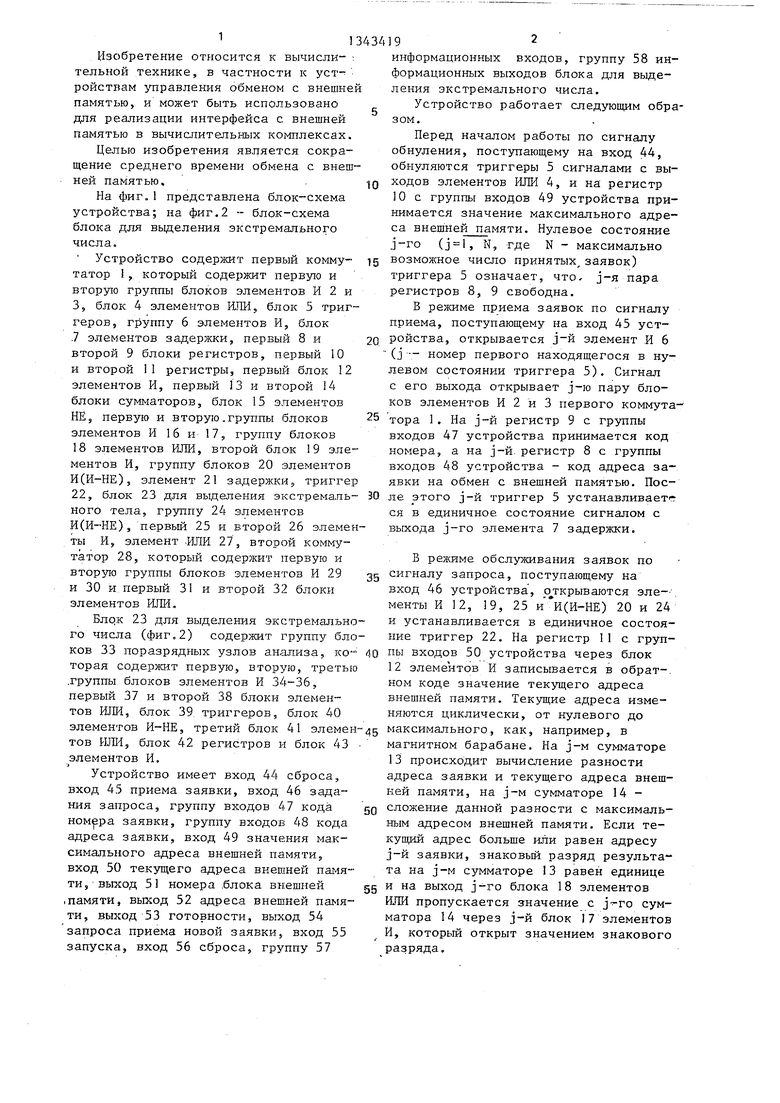

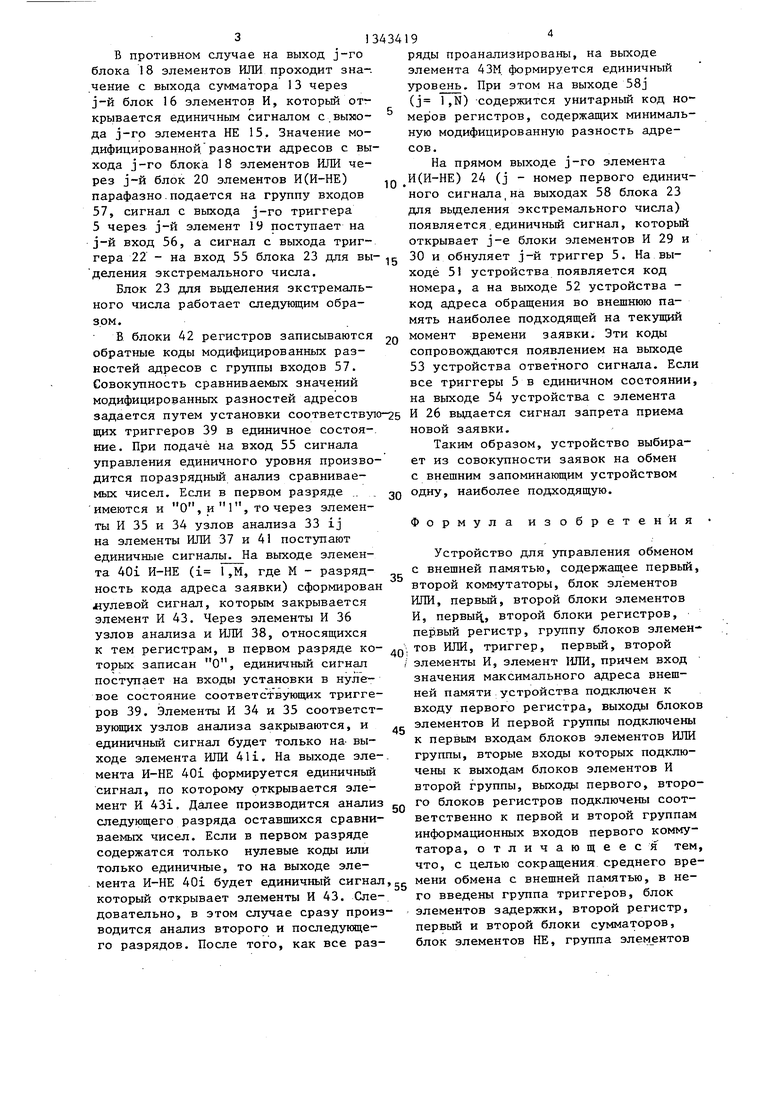

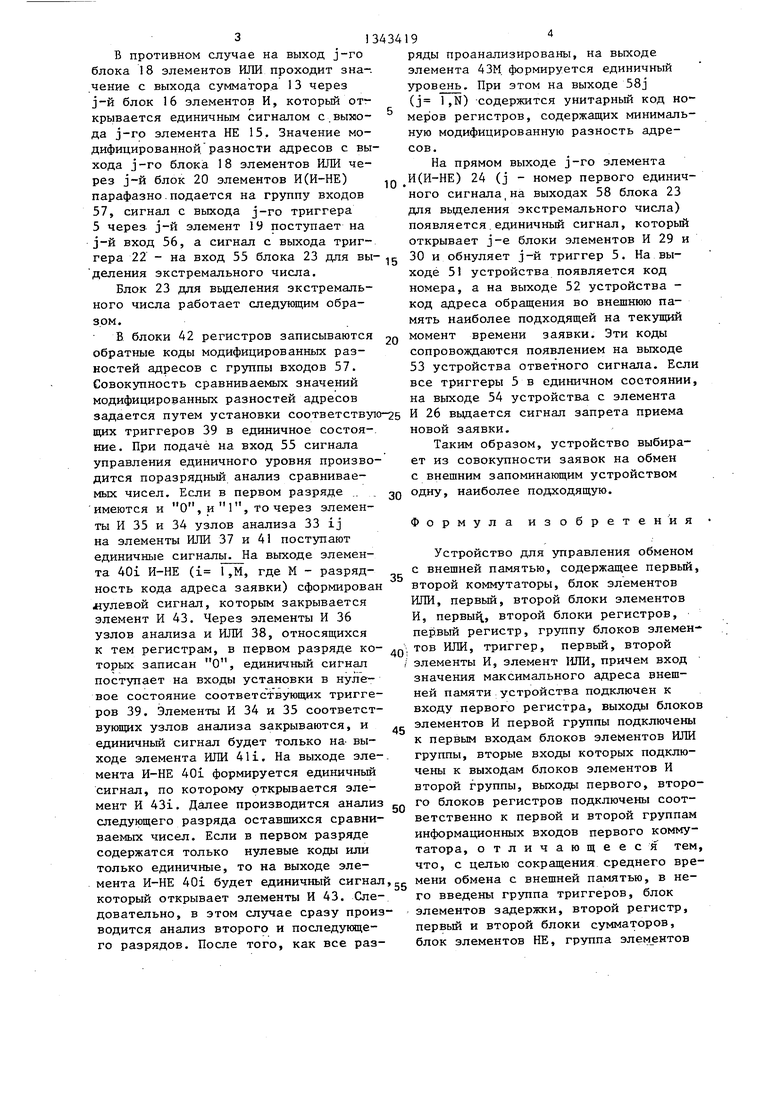

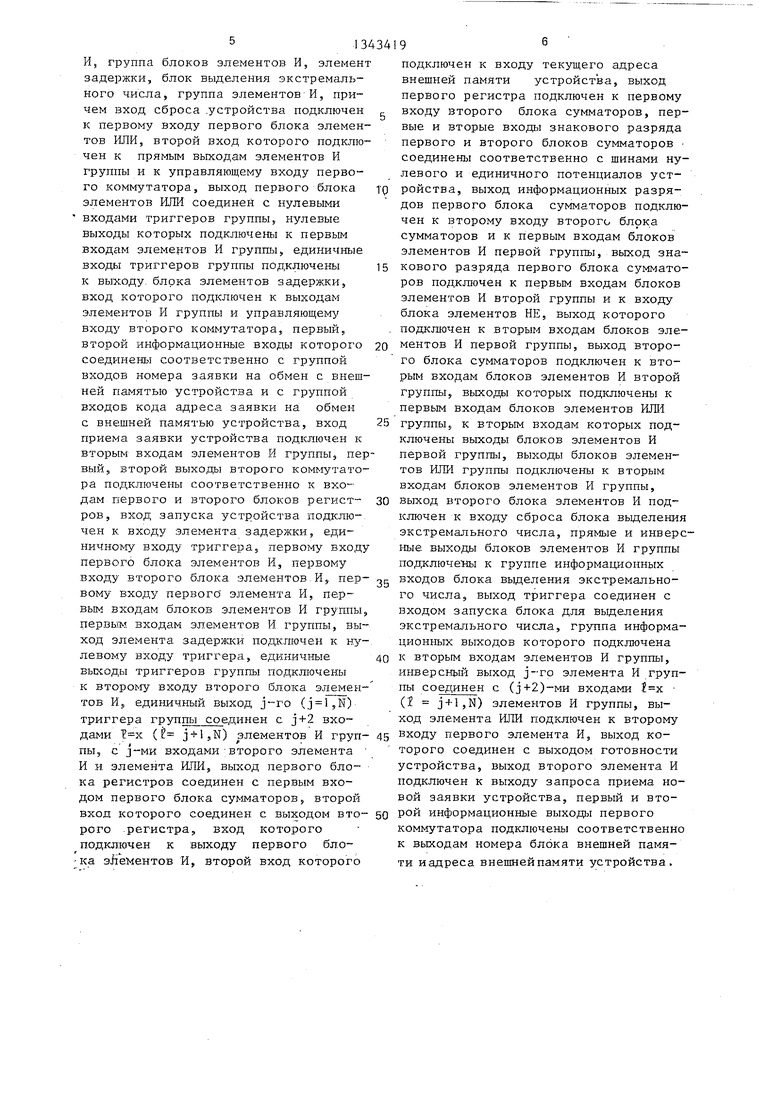

На фиг,1 представлена блок-схема устройства; на фиг.2 - блок-схема блока для выделения экстремального числа.

Устройство содержит первый комму- татор 1, который содержит первую и вторую группы блоков элементов И 2 и 3, блок 4 элементов ИЛИ, блок 5 триггеров, группу 6 элементов И, блок .7 элементов задержки, первый 8 и второй 9 блоки регистров, первый 10 и второй 11 регистры, первый блок 12 элементов И, первый 13 и второй 14 блоки сумматоров, блок 15 элементов НЕ, первую и вторую.группы блоков элементов И 16 и 17, группу блоков 18 элементов ИЛИ, второй блок 9 элементов И, группу блоков 20 элементов И(И-НЕ), элемент 2 задержки, триггер 22, блок 23 для выделения экстремаль- кого тела, группу 24 элементов И(), первый 25 и второй 26 элементы И, элемент -ИЛИ 27, второй коммутатор 28, который содержит первую и BTopjra группы блоков элементов И 29 и 30 и первый 31 и второй 32 блоки элементов ИЛИ.

Блок 23 для выделения экстремального числа (фиг.2) содержит группу блоков 33 поразрядных узлов анализа, ко торая содержит первую, вторую, третью .группы блоков элементов И 34-36, первый 37 и второй 38 блоки элементов ИЛИ, блок 39. триггеров, блок 40 элементов И-НЕ, третий блок 41 элемен тов ИЛИ, блок 42 регистров и блок 43 элементов И.

Устройство имеет вход 44 сброса, вход 45 приема заявки, вход 46 задания запроса, группу входов 47 кода номера заявки, группу входов 48 кода адреса заявки, вход 49 значения максимального адреса внешней памяти, вход 50 текущего адреса внешней па1-1Я ти,-выход 5 номера .блока внешней .памяти, выход 52 адреса внешней памяти, выход 53 готовности, выход 54 запроса приема новой заявки, вход 55 запуска, вход 56 сброса, группу 57

192

информационных входов, группу 58 информационных выходов блока для выделения экстремального числа.

Устройство работает следующим образом.

Перед началом работы по сигналу обнуления, поступающему на вход 44, обнуляются триггеры 5 сигналами с выходов элементов РШИ 4, и на регистр 10 с группы входов 49 устройства принимается значение максимального адреса внешней памяти. Нулевое состояние j-ro (, N, где N - максимально возможное число принятых заявок) триггера 5 означает, что, j-я пара регистров 8, 9 свободна.

В режиме приема заявок по сигналу приема, поступающему на вход 45 устройства, открывается j-й элемент ,И 6 (j -- номер первого находящегося в нулевом состоянии триггера 5). Сигнал с его выхода открывает j-ю пару блоков элементов И 2 и 3 первого коммутатора 1. На j-й регистр 9 с группы входов 47 устройства принимается код номера, а на j-й регистр 8 с группы входов 48 устройства - код адреса заявки на обмен с внешней памятью. После этого j-й триггер 5 устанавливаете ся в единичное состояние сигналом с выхода j-ro элемента 7 задержки,

В режиме обслуживания заявок по сигргалу запроса, поступающему на вход 46 устройства, сггкрываются эле-менты И 12, 19, 25 и иСИ-НЕ) 20 и 24 и устанавливается в единичное состояние триггер 22, На регистр 11 с группы входов 50 устройства через блок

12элементов И записывается в обрат-. ном коде значение текущего адреса внешней памяти. Текущие адреса изменяются циклически, от нулевого до максимального, как, например, в магнитном барабане. На j-м сумматоре

13происходит вычисление разности адреса заявки и текущего адреса внешней памяти, на j-M сумматоре 14 - сложение данной разности с максималь- адресом внешней памяти. Если текущий адрес больше i-ши равен адресу j-й заявки, знаковый разряд результата на j-M сумматоре 13 равен единице и на выход j-ro блока 18 элементов ИЛИ пропускается значение с сумматора 14 через j-й блок 17 элементов И, который открыт значением знакового разряда.

31

В противном случае на выход j-ro блока 18 элементов ИЛИ проходит значение с выхода сумматора 13 через j-й блок 16 элементов И, которьй отг- крывается единичным сигналом с.выхо- да j-rp элемента НЕ 15. Значение модифицированной, разности адресов с выхода j-ro блока 18 элементов ИЖ через j-й блок 20 элементов И(И-НЕ) парафазно.подается на группу входов 57, сигнал с выхода j-ro триггера 5 через j-й элемент 19 поступает на j-й вход 56, а сигнал с выхода триггера 22 - на вход 55 блока 23 для вы деления экстремального числа.

Блок 23 для вьщеления экстремального числа работает следующим образом.

В блоки 42 регистров записываются обратные коды модифицированных разностей адресов с группы входов 57. Совокупность сравниваемых значений модифицированных разностей адресов задается путем установки соответству1 щих триггеров 39 в единичное состоя-, ние. При подаче на вход 55 сигнала управления единичного уровня производится поразрядный анализ сравниваемых чисел. Если в первом разряде .. имеются и О,, то через элементы И 35 и 34 узлов анализа 33 ij на элементы ИЛИ 37 и 41 поступают единичные сигналы.На выходе элемента 401 И-НЕ (1 1,М, где М - разрядность кода адреса заявки) сформирован лулевой сигнал, которым закрывается элемент И 43. Через элементы И 36 узлов анализа и ИЛИ 38, относящихся к тем регистрам, в первом разряде ко- торых записан О, единичный сигнал поступает на входы установки в нулевое состояние соответствующих триггеров 39. Элементы И 34 и 35 соответствующих узлов анализа закрываются, и единичный сигнал будет только на- выходе элемента ИЛИ 411. На выходе элемента И-НЕ 401 формируется единичный сигнал, по которому открывается элемент И 431. Далее производится анализ следующего разряда оставшихся сравниваемых чисел. Если в первом разряде содержатся только нулевые коды или только единичные, то на выходе элемента И-НЕ 401 будет единичный сигнал который открывает элементы И 43. Следовательно, в этом случае сразу производится анализ второго и последующего разрядов. После того, как все раз

Q g

n 5 Q Q, / . gg

5

19

ряды проанализированы, на выходе элемента 43М формируется единичный уровень. При этом на выходе 58j (j 1,N) содержится унитарный код номеров регистров, содержащих минимальную модифицированную разность адресов.

На прямом выходе j-ro элемента И(И-НЕ) 24 (J - номер первого единичного сигнала,на выходах 58 блока 23 для выделения экстремального числа) появляется.единичный сигнал, который открывает j-e блоки элементов И 29 и 30 и обнуляет j-й триггер 5. На выходе 51 устройства появляется код номера, а на выходе 52 устройства - код адреса обращения во внешнюю память наиболее подходящей на текущий момент времени заявки. Эти коды сопровождаются появлением на выходе 53 устройства ответного сигнала. Если все триггеры 5 в единичном состоянии, на выходе 54 устройства с элемента И 26 вьщается сигнал запрета приема новой заявки.

Таким образом, устройство выбирает из совокупности заявок на обмен с внешним запоминающим устройством одну, наиболее подходящую.

Формула изобретения

Устройство для управления обменом с внешней памятью, содержащее первый, второй коммутаторы, блок элементов ИЛИ, первый, второй блоки элементов И, первы, второй блоки регистров, первый регистр, группу блоков элементов ИЛИ, триггер, первый, второй элементы И, элемент lUIIi, причем вход значения максимального адреса внешней памяти устройства подключен к входу первого регистра, выходы блоков элементов И первой группы подключены к первым входам блоков элементов ИЛИ группы, вторые входы которых подключены к выходам блоков элементов И второй группы, выходы первого, второго блоков регистров подключены соответственно к первой и второй группам информационных входов первого коммутатора, отличающееся тем, что, с целью сокращения среднего времени обмена с внешней памятью, в него введены группа триггеров, блок элементов задержки, второй регистр, первый и второй блоки сумматоров, блок элементов НЕ, группа элементов

513

И, группа блоков элементов И, элемент задержки, блок выделения экстремального числа, группа элементов И, причем вход сброса .устройства подключен к первому входу первого блока элементов РШИ, второй вход которого подключен к прямым выходам элементов И группы и к управляющему входу первого коммутатора, выход первого блока элементов ИЛИ соединен с нулевыми входами триггеров группы, нулевые выходы которых подключены к первым входам элементов И группы, единичные входы триггеров группы подключены к выходу, блока элементов задержки, вход которого подключен к выходам элементов И группы и управляющему входу второго коммутатора, первый, второй информационные входы которого соединень соответственно с группой входов номера заявки на обмен с внешней памятью устройства и с группой входов кода адреса заявки на обмен с внешней памятью устройства, вход приема заявки устройства подключен к вторым входам элементов И группы, первый, второй выходы второго коммутатора подключены соответственно к входам первого и второго блоков регист- ров, вход запуска устройства подключен к. входу элемента задержки, единичному входу триггера, первому входу первого блока элементов И, первому входу второго блока элементов-И, пер- вому входу первого элемента И, первым входам блоков элементов И группы первым входам элементов И группы, выход элемента задержки подключен к ку- левому входу триггера, единичные вьпсоды триггеров группы подключены к второму входу второго блока элементов Id s единичный выход j-ro (j l5N) триггера rpynniii соединен с j+2 входами (N j-J-,N) элементов И груп- пы, с j-MH входами ; второго элемента И и элемента ИЛИ, выход первого блока регистров соединен с первым входом первого блока сумматоров, второй вход которого соединен с выходом вто- рого регистра, вход которого подключен к выходу первого бло- -ка элементов И, второй вход которого

подключен к входу текущего адреса внешней памяти устройства, выход первого регистра подключен к первому входу второго блока сумматоров, первые и вторые входы знакового разряда первого и второго блоков сумматоров соединены соответственно с шинами нулевого и единичного потенциалов устройства, выход информационных разрядов первого блока сумматоров подключен к второму входу второго блока сумматоров и к первым входам блоков элементов И первой группы, выход знакового разряда первого блока сумматоров подключен к первым входам блоков элементов И второй группы и к входу блока элементов НЕ, выход которого подключен к вторым входам блоков элементов И первой группы, выход второго блока сумматоров подключен к вторым входам блоков элементов И второй группы, выходы которых подключены к первым входам блоков элементов ИЛИ группы, к вторым входам которых подключены выходы блоков элементов И первой групп1з, выходы блоков элементов ИЛИ группы подключены к вторым входам блоков элементов И группы, выход второго блока элементов И подключен к входу сброса блока выделения экстремального числа, прямые и инверсные выходы блоков элементов И группы подключены к группе информационных входов блока вьщеления экстремального числа, выход триггера соединен с входом запуска блока для вьщеления экстремального числа, группа информационных выходов которого подключена к вторым входам элементов И группы, инверсньш выход j-ro элемента И группы соединен с (з+2)-ми входами х (I j+i,N) элементов И группы, выход элемента ИЛИ подключен к второму входу первого элемента И, выход которого соединен с выходом готовности устройства, выход второго элемента И подключен к выходу запроса приема новой заявки устройства, первый и второй информационные выходы первого коммутатора подключены соответственно к выходам номера блока внешней памяти иадреса внешнейпамяти устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешней памятью | 1986 |

|

SU1401467A1 |

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Устройство для экстремальной фильтрации | 1988 |

|

SU1536371A1 |

| Устройство для параллельного формирования адресов | 1987 |

|

SU1418711A1 |

| Модель узла графа | 1985 |

|

SU1297070A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для поиска данных | 1990 |

|

SU1795447A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

Изобретение относится к области цифровой вычислительной техники, в частности к устройствам для управления обменом с внешней памятью, и может быть использовано для реализа- ции интерфейса с внешней памятью в вычислительных комплексах. Целью изобретения является сокращение среднего времени обмена с внешней памятью. Устройство содержит первый, второй коммутаторы,блок элементов ИЛИ, блок триггеров, группу элементов И, блок элементов задержки, первый, второй блоки регистров, первый, второй региг стры, первый, второй блоки элементов И, первый, второй блоки сумматоров, блок элементов НЕ, первую, вторую группы блоков элементов И, группу блоков элементов ИЛИ, группу блоков элементов И (И-НЕ), элемент задержки, триггер, блок для вьщеления экстремального числа, группу элементов И(И-НЕ), первый, второй элементы И, : Элемент ИЛИ. Устройство сокращает рреднее время обслуживания заявок на обмен с внешней памятью вычислитдль- ного комплекса за счет аппаратной реализации выбора наиболее подходящей по адресации в данный момент заяв- ки. 2 ил. i (Л

Составитель С.Бурухин Редактор И.Николайчук Техред М.Дидык .Корректор С.Черни

Заказ 4825/50Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Авторское свидетельство СССР № 811722, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке № 3851544/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-07—Публикация

1985-04-11—Подача