S

(Л

4i

00

lpUi.1

ства. за счет обеспечения произвольного начального адреса и обеспече- возможности маскирования выдачи адресов. С этой целью устройство содержит регистры адреса 1, шага 2 и максимального 4 индекса, блок 3 запоминания индексов, сумматоры 5, схемы 6 сравнения, два элемента ИЛИ 7, 19, триггер 8 границы, группы-9 выходных элементов И, буферные 10 регистры, С5 матор 11 границы, коммута TJop 12, группы элементов И 13, 25 и ИЛИ 26, счетчики 14 и 15, дешифра- фр 16, регистр 17 маски, триггер 1|8, два элемента И 20 и 21, элемент

НЕ 22, два элемента 23 и 24 задержки и элементы И-НЕ 27. Значение шага индекса с регистра,2 шага подается на адресные входы блоков памяти, входящих в состав блока 3 запоминания индексов. Считанные значения индексов суммируются сумматорами 5 с начальным адресом, заданным на регистре 1 адреса, или с адресом продолжения, поступающим с выхода коммутатора 12. Выборочное маскирование формируемых адресов осуществляется кодом, хранящимся на регистре 17 маски, с помощью групп элементов И 25 и ИЛИ 26. 1 з.п. ф-лы, 2 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного формирования адресов | 1985 |

|

SU1337898A1 |

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

| Устройство для получения информации от дефектоотметчика | 1990 |

|

SU1764068A1 |

| Устройство для параллельного формирования адресов | 1988 |

|

SU1575181A2 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1652982A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

Изобретение относится к вычислительной технике и может быть использовано в параллельных вычислительных системах с общим управлением и с основной памятью, состоящей из нескольких независимоадресуемых блоков. Цель изобретения - расширение функциональных возможностей устрой

.-

I 1 .

Изобретение относится к вычисли- :гельной технике и может.быть использовано в параллельных вычислительных системах с общим управлением и с основной памятью, состоящей из несколь ких независимо адресуемых блоков.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения форми- |5ования произвольного начального адреса и обеспечения возможности маскирования вьщачи адресов.

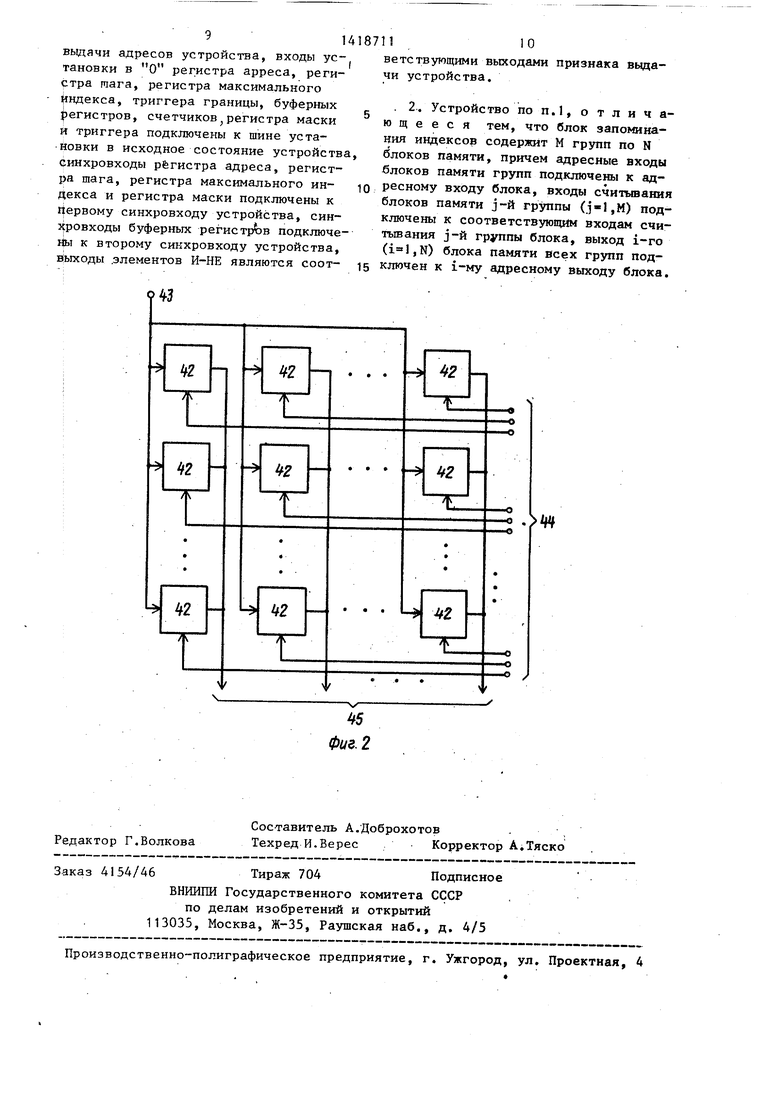

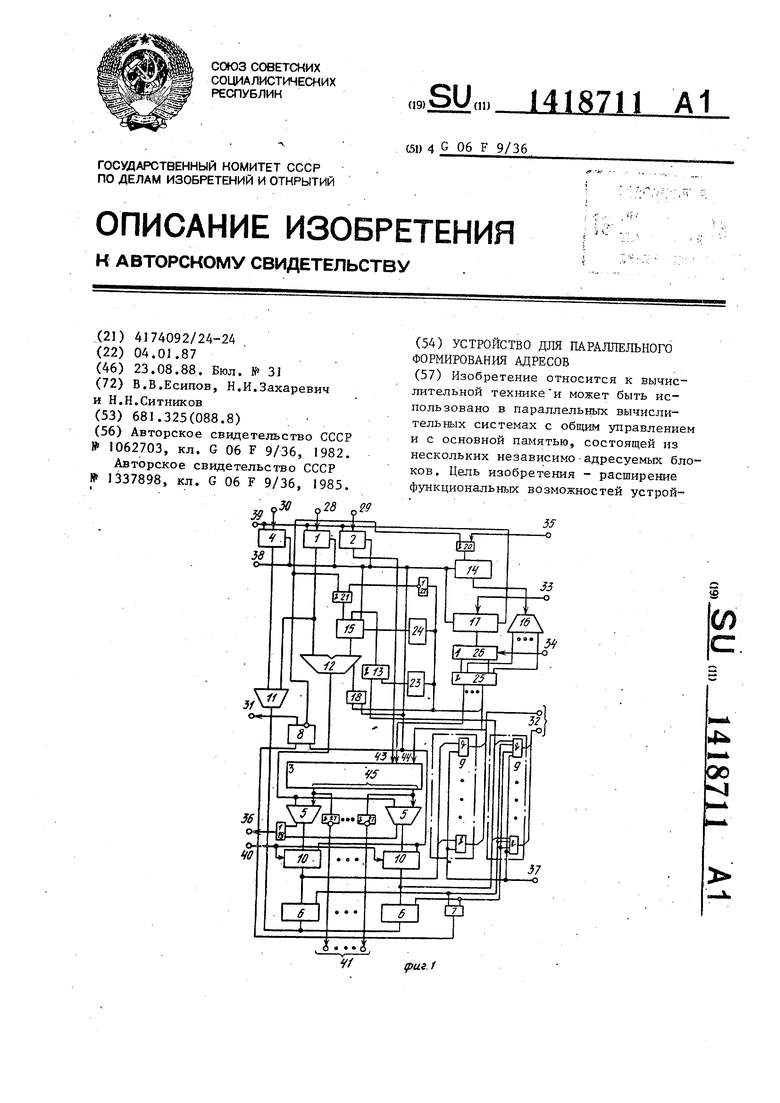

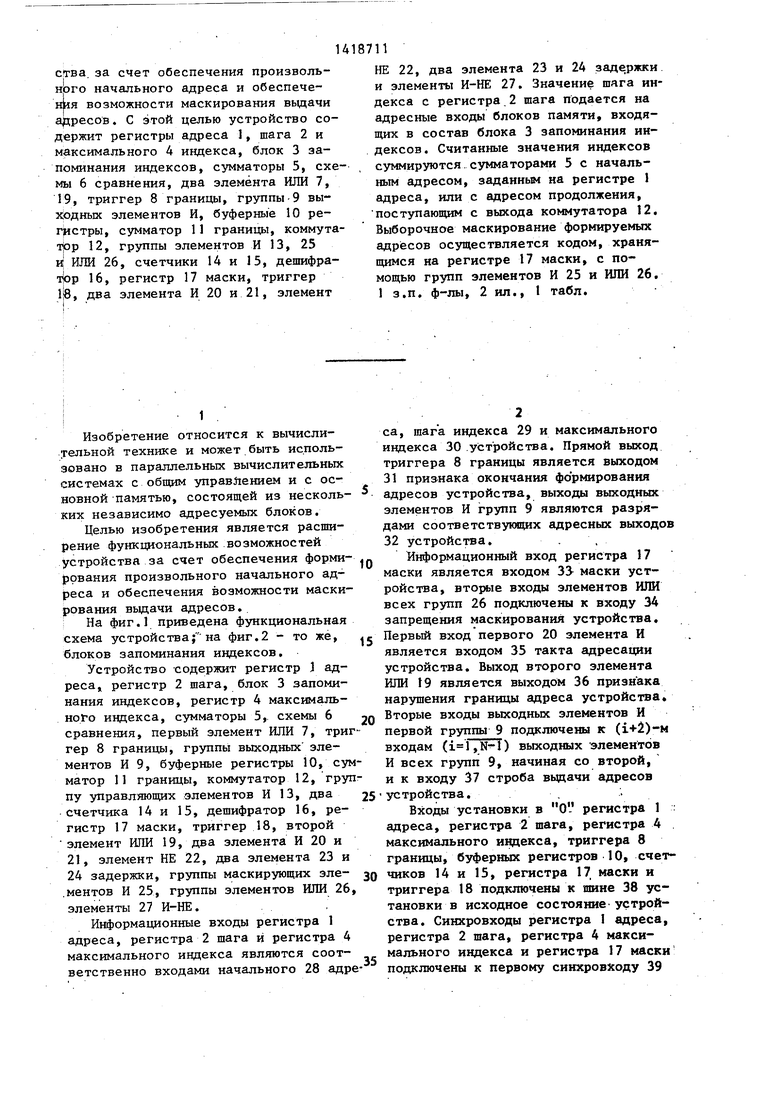

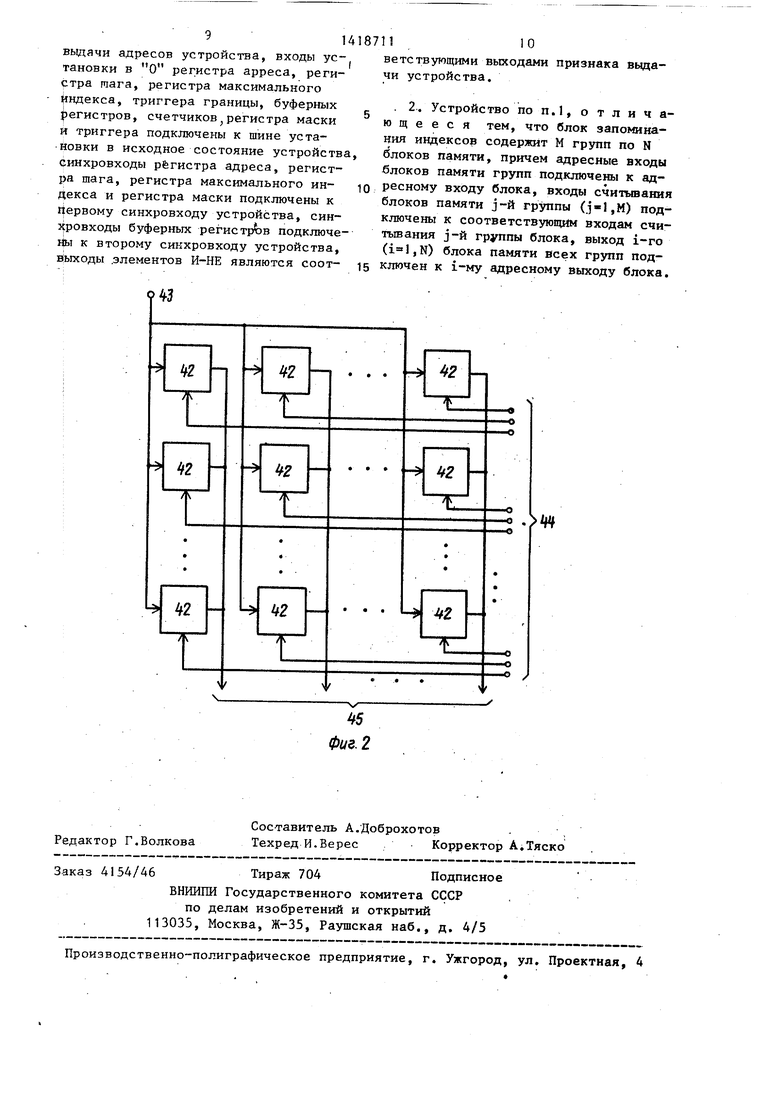

На фиг.1 приведена функциональная схема устройства; на фиг.2 - то же, блоков запоминания индексов.

Устройство содержит регистр 1 адреса, регистр 2 шага, блок 3 запоминания индексов, регистр 4 максимального индекса, сумматоры 5, схемы 6 сравнения, первый элемент ИЛИ 7, триггер 8 границы, группы выходных элементов И 9, буферные регистры 10, сумматор 11 границы, коммутатор 12, группу управляющих элементов И 13, два счетчика 14 и 15, дешифратор 16, регистр 17 маски, триггер 18, второй элемент ИЛИ 19, два элемента И 20 и 21, элемент НЕ 22, два элемента 23 и 24 задержки, группы маскирующих эле- .ментов И 25, группы элементов ИЛИ 26 элементы 27 И-НЕ.

Информационные входы регистра 1 адреса, регистра 2 шага и регистра 4 максимального индекса являются соот

ветственно входами начального 28 адре

с

0 5 о

5

са, шага индекса 29 и максимального индекса 30 устройства. Прямой выход триггера 8 границы является выходом

31признака окончания формирования адресов устройства, выходы выходных элементов И групп 9 являются разрядами соответствующих адресных выходов

32устройства. , , Информационный вход регистра 17

маски является входом 3S маски устройства, вторые входы элементов ИЛИ всех групп 26 подключены к входу 34 запрещения маскирования устройства. Первый вход первого 20 элемента И является входом 35 такта адресации устройства. Выход второго элемента ИЛИ 19 является выходом 36 признака нарушения границы адреса устройства. Вторые входы выходных элементов И первой группы 9 подключены к (1+2)-м входам ( ,) выходных элементов И всех групп 9, начиная со второй, и к входу 37 строба вьщачи адресов устройства.

Входы установки в OV регистра 1 : адреса, регистра 2 шага, регистра 4 максимального индекса, триггера 8 границы, буферных регистров 10, счетчиков 14 и 15, регистра 17 маски и триггера 18 подключены к шине 38 установки в исходное состояние устройства. Синхровходы регистра 1 адреса, регистра 2 шага, регистра 4 максимального индекса и регистра 17 маски подключены к первому синхровходу 39

3141871

устройства. Синхровходы буферных регистров 10 подключены к второму син- хровходу 40 устройства. Выходы эле- i

ментов И-НЕ 27 являются соответству. .5

ющими выходами 41 признака вьщачи

устройства.

Блок 3 запоминания индексов содержит группы 42 блоков памяти, причем адресные входы блоков памяти групп 42 подключены к адресному входу 43 блока 3, входы считьшания блог ков памяти каждой группы 42 подключены к соответствующим входам считьшания одноименной группы 44 блока 3. Выход i-ro (,N) блока памяти всех групп 42 подключен к i-му адресному выходу 45 блока 3.

: Устройство работает следующим образом.

Предполагается хранение адресуемых данных в основной памяти вычислительной системы в виде одномерного массива (вектора), причем соседние элементы вектора имеют отличающиеся на единицу значения адреса. Основная память вычислительной системы состоит из Р (Р - .целое число) блоков (Р М N), имеющих независимые адресные цепи одинаковой разрядки. Адреса элементов массива чередуются по .блокам основной памяти, т.е. номер блока основной памяти задается Jlog Р младшими разрядами адреса. Адреса ячеек основной памяти образуются путем суммирования начального адреса с последовательными значениями индекса отличающимися на заданный шаг. Граница индекса (размер век тора) задается программно. Единственным ограничением является условие кратности границы шагу индекса. Устройство обеспечивает парал лельную выдачу значений индекса с заданным шагом.

После установки устройства по шине 38 в исходное состояние происходит загрузка начального адреса на. регистр 1 адреса, шага индекса, на регистр 2 шага и границы (максимального значения) индекса - на регистр 4 максимального индекса, В этом же такте выполняется запись кода маски на регистр 17 маски, разрядность которого равна М N.

Значение шага индекса с регистра 2 шага пбдается в качестве адреса на адресные входы всех Р М N блоков

1

42 памяти, входящих в состав блока 3

запоминания индексов.

В блоках. 42 записаны заранее вычисленные значения индексов, для всех возможных значений шага (для наглядности фактически хранимые двоичные коды преобразованы в десятичргые и принято М I, N Р), представленные в таблице.

15

20

25

о

30

о

о

5

5

0

5

При подаче сигнала считьшания на входы считывания всех блоков 42 памяти, блока запоминания индексов, на адресных выходах 45 блока 3 будут параллельно считаны Р значений индексов с заданньм шагом.

Рассмотренная Ситуация соответст- вуе т крайнеъгу случаю, когда блок 3 содержит единственную группу блоков :42 памяти (М 1, N Р). Следует учитывать, что количество сумматоров 5, схем 6 сравнения, буферных регистров 10, а также групп 9 ВЕ ГХОДНЫХ элементов И равны количеству одновременно считьшаемых индексов, т.е. количеству блоков 42 памяти, на которые подается сигнал считывания в одном такте.

Структура предлагаемого устройства позволяет варьировать значения М и N, оставляя Р М -s N постоянным, т.е. оптимизировать устройство по критерию быстродействие/затраты аппаратуры. При увеличении М и соот- ветствзтощем уменьшении N количество блоков 5, 6, 9 и 10 y Ieньшaeтcя, однако количество тактов считывания, которое по требуется для выработки

5,1

всех Р индексов, растет, т.е-, быстро- Д€ йствие устройства уменьшается, достигая в пределе, (при М Р, N « 1) бь стродействия последовательного формирователя адресов-.

Считанные в одном такте N значений индексов подаются на входы соответствующих сумматоров 5, которые осуществляют их сложение с начальным адресом, считанным с регистра 1 адреса через коммутатор 12, С выходов сумматоров 5 сформированные адреса пфстзшают на соответствующие буферные регистры 10 и сравниваются схемами 6 сравнения со значением максимального адреса, полученным путем суммирования на сумматоре 11 границы содержимого регистра 4 максимального индекса с начальным адресом, записанным на ре- .гйстре 1 адреса.

Если равенство не зафиксировано Н|(1 одной из схем 6 сравнения, то сфор м рованнь:е адреса параллельно вьщают- с группами 9 выходных элементов И nk соответствующие адресные 32 выходы устройства и выполняется следующий такт формирования адрес ов.

В случае если вьтолнены все М тактов цикла формирования адресов, а сравнения (достижения граничного адреса) не произощло, то значение максимального адреса, сформированного в данном цикле и записанного в N-й буферный регистр 10,, загружается через грзтпу 13 управляющих элементов И по информационному входу во второй счетчик 15.Одновременно устанавливается в единицу триггер 18, обеспечивая в дальнейиих циклах формирования адре-i сов подключение информационного выхода второго счетчика 15 к входам первого слагаемого сумматоров 5, замещая, таким образом, на этих входах начальный адрес.

При достижении граничного адреса на каком-либо из буферных регистров 10 соответствующая схема 6 сравнения вырабатьтает нулевой сигнал, блоки- рующий выдачу группами 9 выходных элементов И всех адресов, сформиро- «анных в данном такте и превосходящих граничный. Сам граничный адрес вьщается. Одновременно, сигнал срав- нения, пройдя через первый элемент lilTTi 7, устанавливает триггер 8 гра- ишды в единицу, блокируя тем самым прохождение через первый 20 элемент

116

И дальнейщих сигналов считывания на

счетный вход первого 14 счетчика.

Маскирование сформированных адресов реализуется следующим образом. Нулевое значение i-ro разряда j-й группы ( ,M) регистра 17 маски задает маскирование i-ro адреса в J-M такте цикла формирования адресов. При этом сигнал считьшания не поступает на i-й блок 42 памяти j-й группы. На все входы i-ro элемента И-НЕ 27 поступают единичные значения, а на сосггветствующем выходе 41 признака вьщачи устройства устанавливается соответственно нулевое значение. Это значение является признаком, того, что информация на i-м адресном выходе устройства не должка восприниматься как сформированный адрес и игно1)ируется. Если в последнем М-м такте цикла формирования адресов последний адрес замаскирован, т.е. N-й разряд М-й группы регистра 17 маски равен нулю, и граничный адрес не достигнут, то по отсутствию сигнала считьшания- на N-M входе М-и группы блока 3 запоминания индексов, содержимое второго счетчика 15 автоматически получает приращеиие на Р.

Запрет маскирования осуществляет ся подачей единичного сигнала на вторые входы элементов ИЛИ 26 всех групп.

Таким образом, предлагаемое устройство обеспечивает параллельное формирование адресов, отличающихся на заданный шаг индексации и начинающихся с произвольного значения, т.е. с адреса операида в произвольном блоке основной памяти.

Кроме того, предлагаемо.е устройство обеспечивает возможность блокировки любого из формируемых адресов. В целом предлагаемое устройство обладает более широкими функциональными возможностями, чем известное устройство.

Формула изобретения

71

групп выходных элементов И, причем - информационные входы регистра адреса регистра шага и регистра максимально- го индекса подключены соответственно к входам начального адреса, шага индекса и максимального индекса устройства, выход i-й схемы сравнения (i 1,N) подключен к i-м входам элементов И всех групп, начиная с (1+1)-й, и к i-му входу первого элемента ИЛИ, выход которого подключен к входу установки в 1 триггера границы, прямой выход которого является выходом признака окончания формирования адре- сов устройства, выходы выходных элементов И i-й группы являются соответствующими разрядами i-ro адресного выхода устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения произвольного начального адреса и обеспечения возможности маскирования вьщачи адресов в него введены N буферных регистров, сумматор границы, коммутатор, группа управляющих элементов И, два счетчика, дешифратор, регистр маски триг гер, второй элемент ШШ, два элемента задержки, М групш маскирующих элементов И (где М - количество тактов в одном цикле формирования адресов), М групп по N элементов ИЛИ и N . элементов И-НЕ, причем выход регистра адреса подключен к первому информационному входу коммутатора и к входу первого слагаемого сумматора границь вход второго слагаемого которого подключен к выходу регистра максимального индекса, выход суммы - сумматора границы подключен к первым входам схем сравнения, второй вход

.i-й схемы сравнения подключен к выходу i-ro бз ерного регистра, информационный вход которого подключен к выходу сзгммы i-ro сумматора, вход первого слагаемого которого подключен к i-му адресному выходу блока запоминания индексов, разряды i-ro адресного выхода блока запоминания ин-

-дексов ; подключены к соответствующим входам., i-ro элемента И-НЕ, входы второго слагаемого сумматоров подключены к выходу коммутатора, адресный вход которого подключен к пря- мому выходу триггера, вход установки в 1 которого подключен к входам элементов задержки, элемента НЕ и к вькоду N-ro маскирующего элемента И

И8

М-й группы, адресный вход блока запоминания индексов подключен к выходу регистра шага, входы считывания j-й группы (,M) блока запоминания индексов подключены к выходам соответствующих маскирующих элементов И . группы, первые входы которых подключены к j-му выходу дешифратора, а вторые - к выходам соответствующих элементов ИЛИ j-й группы, первые входы которых .подключены к соответствующим разрядам j-й группы выхода регистра маски, информационный вход которого является входом маски уст- ройства, вторые входы элементов ИЛИ всех групп подключены к входу запрещения маскирования устройства, вход дешифратора подключен к. выходу первого счетчика, счетный вход которого подключен к выходу первого элемента И, первый вход которого является входом такта адресации устройства, а второй подключен к инверсному выходу триггера границы и к первому входу второго элемента И, второй вход которого подкхпочен к выходу элемента НЕ, выход второго элемента И подключен к входу увеличения на Р второго счетчика, разряды информационного входа которого подключены к выходам соо.т- ветствующих управляющих элементов И группы, первые входы которых подключены к соответствуюшд1М разрядам выт хода N-ro буферного регистра, вторые входы управляющих элементов И группы подключены-к выходу первого элемента задержки, выход второго элемента задержки подключен к входу разрешения приема по информационному входу второго сч-етчика, выход которого подключен к второму.информационному входу коммутатора, выходы переполнения сумматоров подключены к .соответствующим входам второго элемента ИЛИ, выход которого является выходом признака нарушения границы адреса устройства, (1+1)-е входы выходных элементов И (1+1)-й группы (,N-1) подключены к соответствук1щим разрядам выхода (i+l)-ro буферного регистра, первые входы выходных элементов И первой группы подключены к соответствующим разрядам выхода первого буферного регистра, вторые входы выходных элементов И первой группы подключены к (i+2)-M входам (i «n, N-1).выходных элементов И всех групп, начиная с второй, и к входу строба

вьщачн адресов устройства, входы установки в О регистра арреса, регистра тага, регистра максимального индекса, триггера границы, буферных регистров, счетчиков регистра маски и триггера подключены к шине установки в исходное состояние устройства синхровходы регистра адреса, регистра шага, регистра максимального индекса и регистра маски подключены к Цервому синхровходу устройства, синхровходы буферных регистров подключены к второму синхровходу устройства, въгходы .элементов И-НЕ являются соот 5Фиг. 2

ветствующими выходами признака выдачи устройства,

. 2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что блок запоминания индексов содержит М групп по N блоков памяти, причем адресные входы блоков памяти групп подключены к адресному входу блока, входы считывания блоков памяти j-й группы (j-l,M) подключены к соответствующим входам счи- тьшания j-й группы блока, выход i-ro (,N) блока памяти всех групп подключен к i-му адресному выходу блока.

| Формирователь адреса | 1982 |

|

SU1062703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для параллельного формирования адресов | 1985 |

|

SU1337898A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-04—Подача