4;:ь

О5

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных комплексах для управления обменом с внешней памятью.

Целью изобретения является сокращение среднего времени обмена с внешней памятью.

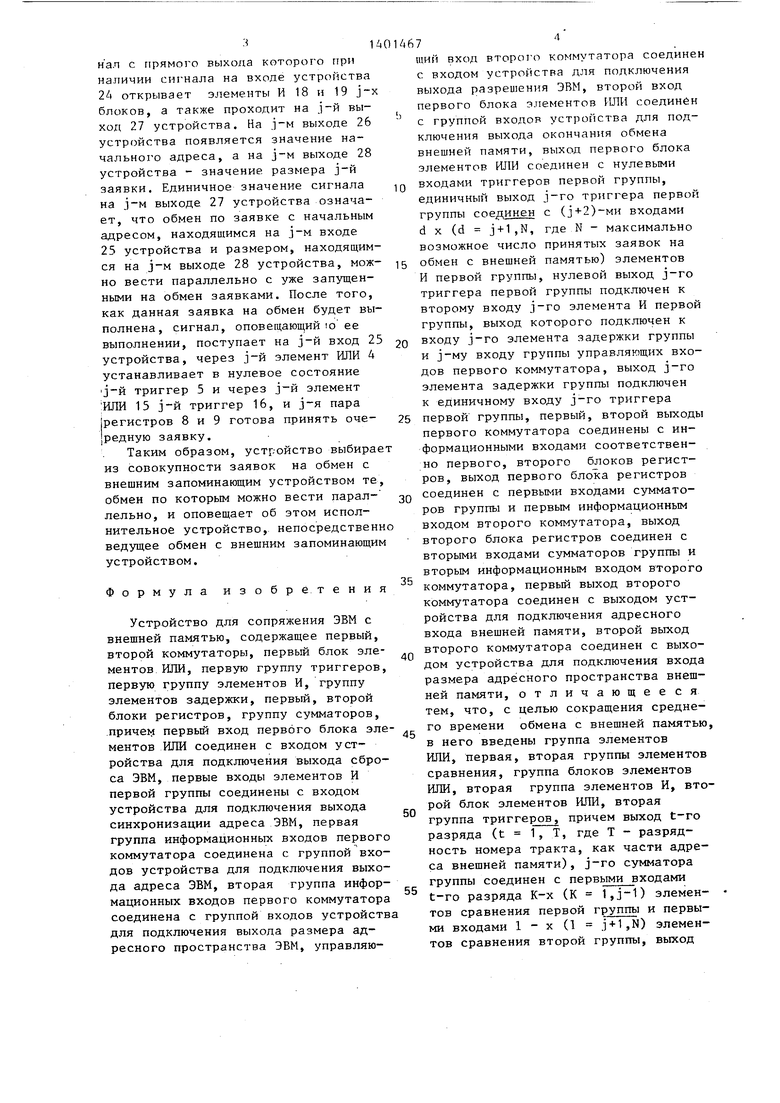

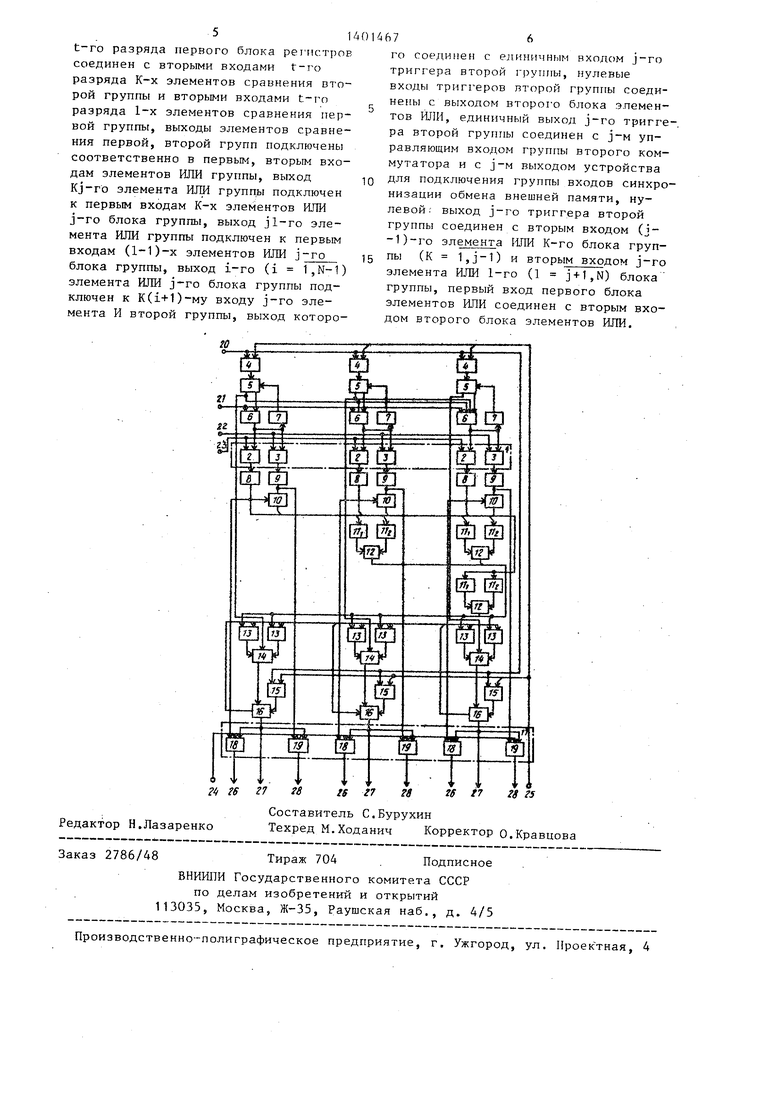

На чертеже приведена блок-схема устройства.

Устройство содержит первый коммутатор, который содержит первую 2, вторую 3 группы блоков элементов И, первый блок 4 элементов ИЛИ, первую группу 5 триггеров, первую группу 6 элементов И, группу 7 элементов задержки, первый 8 и второй 9 блоки регистров, группу 10 сумматоров, первую 11,, вторую 11 группы элементов сравнения, матрицу 12 элементов ИЛИ, группу 13 блоков элементов ИЛИ, вторую группу 14 элементов И, второй блок 15 элементов ИЛИ, вторую группу 16 триггеров, второй коммутатор 17, который содержит первую 18, вторую 1 группы блоков элементов И,вход 20 для подключения выхода сброса ЭВМ, вход 21 для подключения выхода синхронизации адреса ЭВМ, группы 22 и 23 вхо- дов для подключения соответственно выходов адреса ЭВМ и выхода размера адресного пространства ЭВМ, вход 24 для подключения выхода разрешения ЭВМ, вход 25 для подключения выхода окончания обмена внешней памяти, выход 26 для подключения входа адреса внешней памяти, группа 27 выходов для подключения входа синхронизации обмена внешней памяти, выход 28 для подключения входа размера адресного пространства внешней памяти.

Устройство работает следующим образом.

По сигналу обнуления, поступающе- му на вход 20 устройства, обнуляются триггеры 5 сигналами с выходов элементов ИЛИ 4, а также триггеры 16 сигналами с выходов элемента ИЛИ 15. Нулевое состояние j-ro (j 1,N, где N максимально возможное число принятых заявок) триггера 5 означает что j-H пара регистров 8 и 9 свободна. По сигналу, поступающему на вход 21 устройства, открывается j-й элемент И 6 (J - номер первого находяще гося в нулевом состоянии триггера 5) Сигнал с его выхода открывает j-ю пару блоков элементов И 2 и 3 первого

Q

0 о ,.

5

коммутатора 1 . На .i-й регистр 8 с группы 23 входов устройства принима- ется код адреса, а на j-й регистр 9 с группы 22 входов устройства - код размера заявки на обмен с внешней па- мят ью. После этого j-й триггер 5 устанавливается в единичное состояние сигналом с выхода j-ro элемента 7 задержки. На j-M сумматоре 10 вычисляется значение суммы адреса и размера заявки, хранящейся на j-й паре регистров 8 и 9. На К1-й (К 1,N-1, 1 K+1,N) элемент 11 сравнения поступают коды конечного тракта 1-й заявки и начального тракта К-й заявки соответственно из старших Т разрядов (т - разрядность номера тракта как части адреса внешней памяти) 1-го сумматора 10 и К-го регистра 8, а на К1--Й элемент сравнения 11 поступают коды конечного тракта К-й заявки и начального тракта 1-й заявки соответственно из старших Т разрядов К-го сумматора 10 и 1-го регистра 8.

Логическая сумма сигналов с выходов К1-Х элементов сравнения 11 и 11 формируется на выходе К1-го элемента ИЛИ 12. Ее единичное значение говорит о том, что обмен с внешней памятью можно вести параллельно по К-й и 1-й заявкам, поскольку их адреса обращения располагаются в пределах различных трактов. Сигнал bj на выходе j-ro элемента И 14 означает, что обмен с внешней памятью по j-й заявке можно вести параллельно с обменами по всем остальным заявкам, и реализуется по формуле

- N

Ь,- т. л (a,:V.T,, ) Л (a.jVT,, ),

)

J k:1

1

.t

0

где Т 5J сигнал на прямом выходе

j-ro триггера Т 5;

kj j,( сигналы на выходах соответственно Kj-ro и jl-ro

элементов ИШ 12;

T,j,, - сигналы на инверсных выходах триггеров 16| и 16f соответственно. Из данной формулы видно, что, если К-я или (и) 1-я заявки имеют с j-й общие тракты, но не запущены на обслуживание в связи с задержкой их обслуживания другими заявками, заявку разрешено запустить в обслуживание.

Сигнал bj устанавливает в единичное состояние j-й триггер 16, сигнал с прямого выхода которого при наличии сигнала на входе устройства 2А открывает элементы И 18 и 19 j-x блоков, а также проходит на .|-й выход 27 устройства. На j-м выходе 26 устройства появляется значение начального адреса, а на j-м выходе 28 устройства - значение размера j-й заявки. Единичное значение сигнала на j-м выходе 27 устройства означает, что обмен по заявке с начальным адресом, находящимся на j-м входе 25 устройства и размером, находящимся на j-м выходе 28 устройства, мож- но вести параллельно с уже запущенными на обмен заявками. После того, как данная заявка на обмен будет выполнена, сигнал, оповещающий ю ее выполнении, поступает на j-й вход 25 устройства, через j-й элемент ИЛИ 4 устанавливает в нулевое состояние j-й триггер 5 и через j-й элемент ИЛИ 15 j-й триггер 16, и j-я пара регистров 8 и 9 готова принять оче- редную заявку.

Таким образом, устройство выбирае из совокупности заявок на обмен с внешним запоминающим устройством те, обмен по которым можно вести парал- лельно, и оповещает об этом исполнительное устройство, непосредственн ведущее обмен с внешним запоминающим устройством.

Формула изобретения

Устройство для сопряжения ЭВМ с внешней памятью, содержащее первый, второй коммутаторы, первый блок элементов ИЛИ, первую группу триггеров, первую группу элементов И, группу элементов задержки, первый, второй блоки регистров, группу сумматоров, приче : первый вход первого блока элементов ИЛИ соединен с входом устройства для подключения выхода сброса ЭВМ, первые входы элементов И первой группы соединены с входом устройства для подключения выхода синхронизации адреса ЭВМ, первая группа информационных входов первого коммутатора соединена с группой входов устройства для подключения выхода адреса ЭВМ, вторая группа информационных входов первого коммутатора соединена с группой входов устройств для подключения выхода размера адресного пространства ЭВМ, управляю

Q 5 о 5

о

5

5

0

5

ший вход BTopoi o коммутатора соединен с входом устройства для подключения выхода разрешения ЭВМ, второй вход первого блока элементов 1ШИ соединен с группой входов устройства для подключения выхода окончания обмена внешней памяти, выход первого блока элементов ИЛИ соединен с нулевыми входами триггеров первой группы, единичный выход j-ro триггера первой группы соединен с (j+2)-MH входами d X (d j+1,N, где N - максимально возможное число принятых заявок на обмен с внешней памятью) элементов И первой группы, нулевой выход j-ro триггера первой группы подключен к второму входу элемента И первой группы, выход которого подключен к входу j-ro элемента задержки группы и j-му входу группы управляющих входов первого коммутатора, выход j-ro элемента задержки группы подключен к единичному входу j-ro триггера первой группы, первый, второй выходы первого коммутатора соединены с информационными входами соответственно первого, второго блоков регистров, выход первого блока регистров соединен с первыми входами сумматоров группы и первым информационным входом второго коммутатора, выход второго блока регистров соединен с вторыми входами сумматоров группы и вторым информационным входом второго коммутатора, первый выход второго коммутатора соединен с выходом устройства для подключения адресного входа внешней памяти, второй выход второго коммутатора соединен с выходом устройства для подключения входа размера адресного пространства внешней памяти, отличающееся тем, что, с целью сокращения среднего времени обмена с внешней памятью, в него введены группа элементов ИЛИ, первая, вторая группы элементов сравнения, группа блоков элементов ИЛИ, вторая группа элементов И, второй блок элементов ИЛИ, вторая группа триггеров, причем выход t-ro разряда (t 1, Т, где Т - разрядность номера тракта, как части адреса внешней памяти), j-ro сумматора группы соединен с первыми входами t-ro разряда К-х (К 1,j-1) элементов сравнения первой группы и первыми входами 1 - X (1 j+1,N) элементов сравнения второй группы, выход

W П

iS t

28 гз

Редактор Н.Лазаренко

г ts г fs

Составитель С.Бурухин

Техред М.Ходанич Корректор О.Кравцова

iS t

28 гз

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обменом с внешней памятью | 1985 |

|

SU1343419A1 |

| Система коммутации | 1985 |

|

SU1317447A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

| Устройство для распределения ресурсов памяти в вычислительном комплексе | 1985 |

|

SU1288705A1 |

| Устройство для сопряжения вычислительных групп, состоящих из основной и вспомогательных ЭВМ | 1991 |

|

SU1783532A1 |

| Устройство обмена данными распределенной управляющей системы | 1990 |

|

SU1718226A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных комплексах для управления обменом с внешней памятью. Целью изобретения является сокращение среднего времени обмена с внешней памятью. Устройство содержит первый коммутатор, первый блок элементов ИЛИ, первую группу триггеров, первую группу элементов И, группу элементов задержки, первый, второй блоки регистров, группу сумматоров, первую, вторую группы элементов сравнения, матрицу элементов ИЛИ, группу блоков элементов ИЛИ, вторую группу элементов И, второй блок элементов ИЛИ, вторую группу триггеров, второй коммутатор. Устройство выбирает из совокупности заявок на обмен с внешней памятью те заявки, обмен по которым можно вести параллельно. 1 ил. (Л с §

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления обменом с внешней памятью | 1985 |

|

SU1343419A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-04-15—Подача