тьи входы первого и третьего элементов И подключены к выходу знака ариф метико-логического блока, третьи входы второго и четвертого элементов И соединены с выходом элемента НЕ, вход установки, вход сброса, пря мой и инверсный выходы первого триггера подключены соответственно к выходам первого и второго элементов И и первь м входам пятого и шестого элементов И, вход установки, вход сброса, прямой и инверсный выходы второго триггера соединены соответственно с выходами третьего и четвёр того элементов И и первыми входами седьмого и восьмого элементов И, 21 первый вход девятого элемента И подключен к выходу десятого элемента И, первый и второй входы которого соединены с прямыми выходами соответственно первого и второго триггеров, вторые входы пятого, шестого, седьмого, восьмого и девятого элементов И подключены соответственно к третьему, четвертому, пятому, шестому и седьмому выходам дешифратора, а с первого по шестой входы элемента ИЛИ соединены соответственно с выходами пятого, шестого, седьмого, восьмого и девятого .элементов Ни входом управления запретом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1246108A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1200288A1 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

| Устройство для обработки данных | 1984 |

|

SU1352498A1 |

УСТРОЙСТВО УПРАВЛЕНИЯ ПОСЛЕДОВАТЕЛЬНОСТЬЮ ОПЕРА1ЩЙ 1ЩФРОВОГО ВЫЧИСЛИТЕЛЯ, содержащее блок памяти программ, счетчик команд, регистр команд, шифратор команд, генератор синхросигналов, счетчик циклов, коммутатор синхросигналов, коммутатор циклов, блок ключей, арифметико-логический блок и блок оперативной памяти, адресный вход и информационньй вход-вь1ход которого соединены соответственно с выходом блока ключей и информационным входом-вькодом арифметико-логического блока, адресный вход и информационный выход блока памяти программ подключены соответственно к выходу счетчика команд и входу регистра команд, информационный выход которого соединен с входом шифратора команд, выходы .поля адресов, поля коротких команд и поля длинных команд которого подключены соответственно к информационным входам блока ключей и коммутатора синхросигналов и первому информационному входу коммутатора циклов, выход генератора синхросигналов соединен с управляющими входами коммутатора синхросигналов и коммутатора циклов, первые выходы которых объединены и подключены к управляющему входу блока ключей и входу кода операции арифметико-логического блока, вторые выходы коммутатора синхросигналов и коммутатора циклов объединены и соединены со счетным входом счетчика команд а третий выход и второй информационный вход коммуi татора циклов подключены соответственно к счетному входу и выходу (Л счетчика циклов, отлич.ающее с я тем, что, с, целью упрощения, С оно содержит блок формирования сигнала запрета операции,- включающий дешифратор, элемент НЕ, два триггера, десять элементов И и элемент ИЛИ, выход которого соединен с входом запрета операции арифметикосо логического блока и управляющим 00 СП 1C входом блока оперативной памяти, первые входы первого, второго, третьего и четвертого элементов И подключены к старпмм разрядам первых выходов коммутаторов синхросигналов и циклов, первый, второй и третий входы дешифратора соединены соответственно с первым, вторым и третьим выходами дополнительных разрядов регистра команд,, вторые входы первого и второго элементов И подключены к первому выходу дешифратора, вторые входы третьего и четвертого элёментов И соединены с вторым выходом дешифратора, вход, элемента НЕ и тре

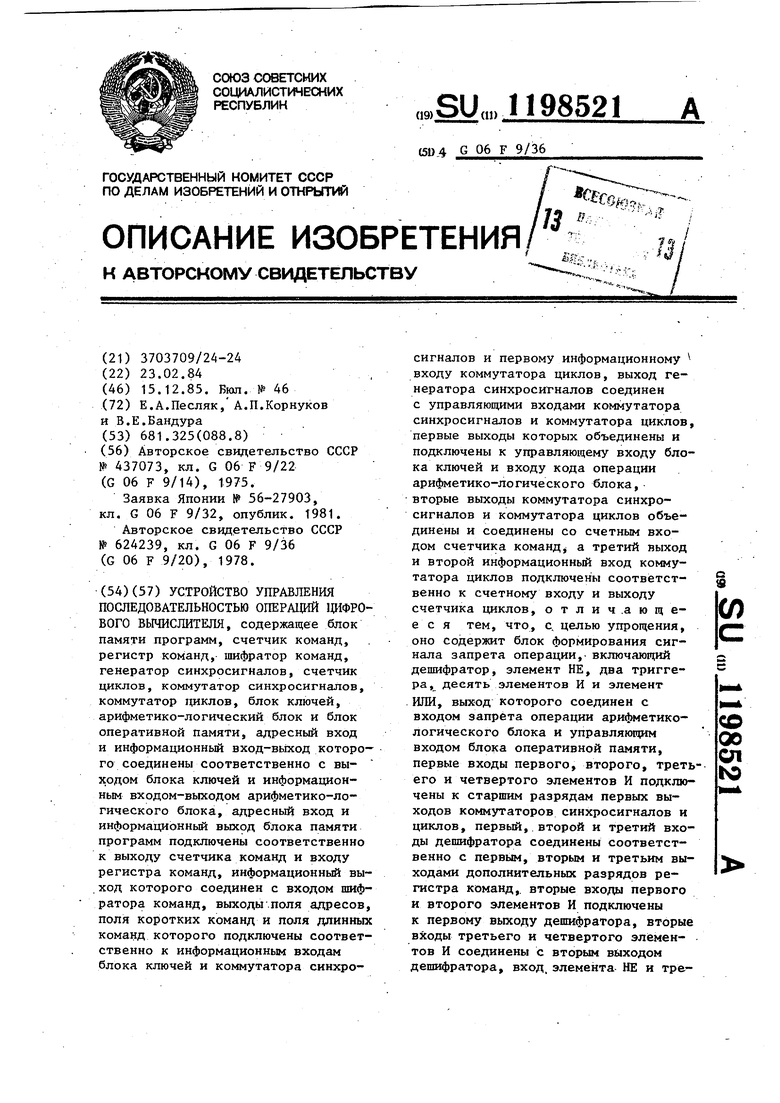

Изобретение Относится к вычислительным цифровым устройствам и предназначено для использования в сисуемах управления для решения вычислительных и логических задач в соответствии с записанной программой.

Цель изобретения - упрощение схемы, управления вычислителем за счет исключения из канала формирования команд таких блоков цифрового вычислителя, как арифметико-логический блок и блок оперативной памяти, исключения команд условный переход и применение только инкрементного метода изменения адресов команд с сохранением возможности управления последовательностью опера1и1й с учетом логического выбора при решении задач. .

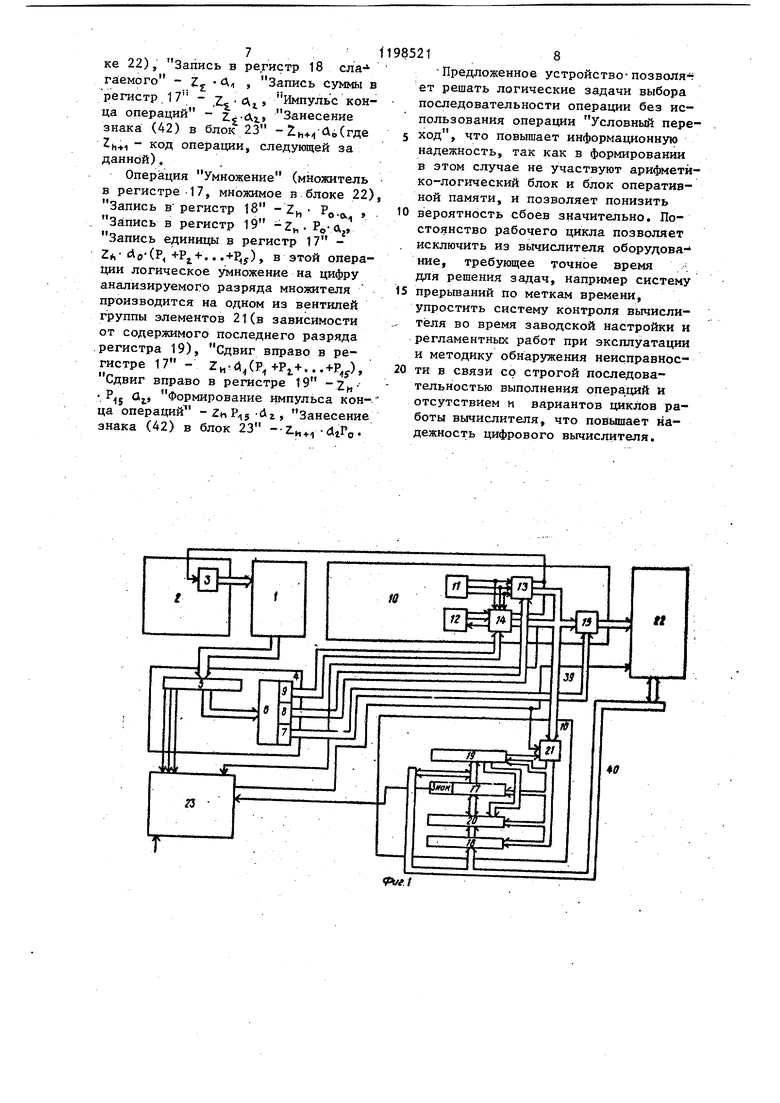

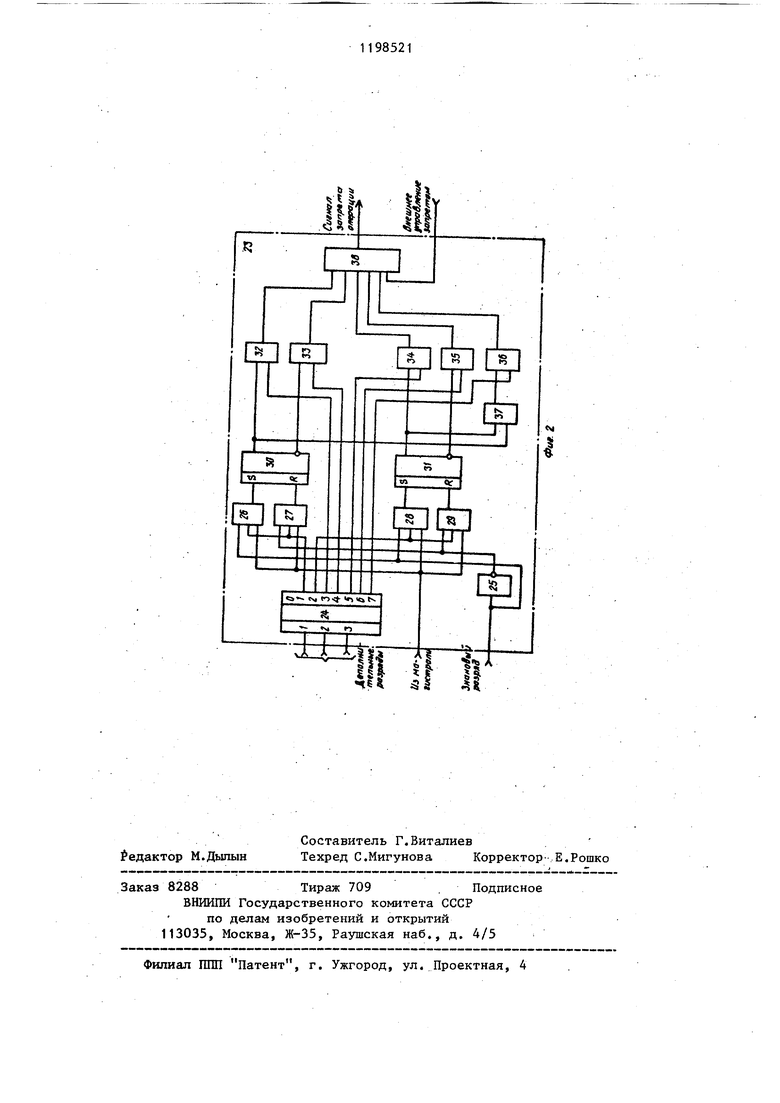

На фиг.1 приведена функциональная С5сема устройства; на фиг.2 схема блока формирования сигнала запрета операции.

Устройство управления последовательностью операций цифрового вычислителя () содержит блок 1 памяти программ, блок 2 переключения программ, включающий счетчик 3 команд, блок 4 формирования команд, состоящий из регистра 5 команд и . шифратора 6 команд, разделенного на три поля; поле 7 адресов, поле 8

коротких команд, поле 9 длинных команд, блок 10 выработки временных интервалов и сигналов микропрограммного управления, состоящий из генератора 11 синхросигналов, счетчика 12 циклов, коммутатора 13 синхросигналов, коммутатора 14 циклов и блока 15 ключей, арифметико-логи-.

| ческий блок 16, состояищй из трех регистров 17, 18 и 19, сумматора 20 и группы 21 элементов И, блок 22 оперативной памяти, блок 23 формирования сигнала запрета выполнения

5 операции, состоя1чий из дешифратора 24 (фиг.2), элемента НЕ 25, четьфех входных элементов И 26-29, двух триггеров 30 и 31, регистра признаков, шести выходных элементов И 320. 37 и элемента ИЛИ 38 на шесть входов, имеет магистраль 39 микрокоманд и информационную магистраль 40(фиг.1).Причем многоразрядный адресный вход блока 1 памяти программ

5 соединен с выходом счетчика 3 команд. Группа информационных входов регистра 5 команд в блоке 4 формирования команд соединена с группой информационных выходов блока 1 па0, мяти программ. Группа информационных выходов регистра 5 команд соединена с информационными входами шифратора 6 команд, имеющего три поля 7,8 и 9. При этом первая группа информационных выходов блока 4 соединяет поле 7 адресов с блоком 15 ключей, вторая группа информационных выходов соединяет поле 8 коротких команд с коммутатором 13 синхросигналов, третья группа информационных выходов соединяет поле 9 длинных команд с коммутатором 14 циклов, четвертая группа из трех информационных вьЕсодов соединяет первый, второй и третий дополнительные разряды регистра 5 команд в блоке 4 формирования команд с первым, вторым и третьим входами дешифратора 24 соответственно в блоке 23 формировач ния сигнала запрета операции.

Коммутатор 13 синхросигналов в блоке 10 имеет группу управляющих выходов для связи с магистралью 39 микрокоманд, управляющие входы (от генератора 11 синхросигналов), один одноразрядный выход, объединенный с одноразрядным выходом коммутатора 14 циклов и соединенньй со счетным входом счетчика 3. Коммутатор 14 циклов в блоке 10 имеет два многоразрядных входа (от шифратора 6 и счетчика 12), группу управляющих вьрсодов для связи с магистралью 39 микрокоманд, управляющий вход (от генератора синхросигналов 11) и один одноразрядный выход, соединенный со счетным входом счетчика 12. Многоразрядная магистраль 39 микрокоманд присоединена к управляющим входам блока 15 ключей и группы элементов 21 в блоке 16, кроме того, одноразрядная управляющая связь из магистрали 39 соединена с первыми входами элементов26 - 29 в блоке 23 Блок 15 ключей имеет адресный выход, соединенньй с входом блока 22 оперативной памяти. Блок 22 оперативной памяти с помощью информационной магистрали 40 соединен с арифметикологическим блоком 16.

Группа элементов 21 в блоке 16 имеет многоразрядньй управляющий выход, соединенньй с управляющими входами регистров 17, 18 и 19 и сумматора 20, два одноразрядных входа, соединенных с элементом 38 в блоке 23 и младшим разрядом регистра 19 множителя. Сумматор имеет три многоразрядных информационных входа, соединенных с регистрами 17, 18 и 19 многоразрядный информационный выход, соединенньй с регистром 17 результата. Регистр 18 имеет многоразрядный

информационньй выход, соединенньй с информационной магистралью 40. Сдвиговьй регистр 19 множителя имеет два многоразрядных информационных входа, соединенных с регистром 17 и информационной магистралью 40, одноразрядньй выход, соединяющий младший разряд регистра 19 с группой элементов 21. Регистр 17 результата имеет три многоразрядных информационных выхода, соединенных с сумматором 20, регистром 19 и информационной магистралью 40. Знаковый разряд регистра 17 результата соединен с входом элемента 25 и третьими входами элементов 26 и 28 блока 23. Третьи входы элементов 27 и 29 соединены с выходом элемента 25. Вторые входы элементов 26 и 27 соединены с первым выходом дешифратора 24. Вторые входы элементов 28 и 29 соединены с вторым выходом дешифратора 24. Выход элемента 26 соединен с входом установки триггера 30, а выход элемента 27 соединен с входом сброса триггера 30. Выход элемента 28 соединен с входом установки триггера 31, а выход элемента 29 соединен с выходом сброса триггера 31. Прямой выход триггера 30 соединен с первым входом элемента 32, а также с вторым входом элемента 37. Инверсньй выход триггера 30 соединен с первым входом элемента 33. Прямой выход триггера 31 соединен с первым

входом элемента 34 и первым входом элемента 37. Инверсньй выход триггера 31 соединен с первым входом элемента 35. Выход элемента 37 соединен с первым входом элемента 36.

Вторые входы элементов 32-36 соединены с третьим, четвертым, пятым, шестым и седьмым выходами дешифрато-. ра 24 соответственно. Выходы элементов 32 - 36 соединены с первым, вторым, третьим, четвертым и пятым входами элемента 38. Шестой вход элемента ИЛИ 38 соединен с входом управления запретом устройства. Выход элемента 38 соединен с соответствующими входами арифметико-логического блока 16 и блока 22 оперативной памяти.

Синхронизацию работы устройства . определяет импульс Конец операции

41, формируемый блоком 10, который исходя из поступившей на его вход команды, отсчитывает временной интервал, необходимой для выполнения

операций. Времязадающими элементами при этом являются генератор 11, счетчик 12 и коммутаторы 13 и 14, Импульс Конец операции 41 переключает в следующее положение счетчик 3.

Устройство работает следующим образом.

После окончания запроса по увеличенному на единицу адресу, сформированному счетчиком 3, в регистр 5 блока 4 из блока 1 записывается очередная команда, три дополнительных разряда которой содержат информацию об обращении к блоку 23. Остальные разряды команды группируются в шифраторе 6 в три поля 7,8 и 9, каждое из которых управляет определенными элементами блока 10. Так, поле 8 коротких команд управляет коммутатором 13, задавая последовательность управлякнцих микрокоманд. Поле 9 длинных команд управляет коммутатором 14.

Генератор 11 связан тремя связями (UQ й, Okj) с коммутаторами 13 и 14, которые переключают в нужной последовательности импульсы генератора 11 в линии микрокомандных импульсов в соответствии с кодом команды с выхода шифратора команд. При многоцикловых операциях прохождения операции (Po.-.Pjj) задаются счетчиком 12. Блок 15 управляетс микрокомандой выборки операнда и адресом, получаемым из поля 7 адресов блока 4. Микрокоманды управления блоком 16 поступают в этот блок по магистрали 39 через группу элементов 21 и далее на входы регистров 17, 18 и 19 и сумматоры 20. Последний выполняет функции, описываемые следую1цими формулами:

5н-(хн icHH- XnVh )-с;г:

), где SH- сумма вн -м разряде; Си - перенос в и -и разряд; , перенос в.(и+1)-й разряд; Х),,УЦ - складываемые числа.

Ланные вводятся и выводятся из блока 16 по информационной магистрали 40, которая связывает последний с блоком 22..

Микрокоманда 42, формируемая в следующий такт после импульса Конец операции у непосредственно после окончания предь)дущей операции.

т.е. во время, пока результат предьщущей операции еще находится в регистре 17, осуществляет стробиро- . вание элементов 26-29 для занесения 5 признака в регистр признаков. При этом если в данной команде обращение к блоку 23 отсутствует, то в трех дополнительных разрядах содержатся нули и в дешифраторе 24 возбужден неиспользуемый нулевой выход. Первый и второй вькоды дешифратора 24 управляют согласно программе занесения результата предыдущей операции из знакового разряда блока 16 через

5 элементы 26-29 в регистр признаков по микрокоманде 42 (триггеры 30 и 31), причем запись осуществляется парафазно, для чего при помощи элемента 25 формируется инверсное зна0.чение сигнала из знакового разряда. Выходы дешифратора 24 с третьего по седьмой управляют пятью элементами 32-36, через которые опрашиваются при наличии сигнала Запрет триггеры 30 и 31 регистра признаков. При этом в зависимости от содержания информации в трех дополнительных разрядах изменение последовательности операций или Запрет осуществляется

0 по единице или по нулю в триггерах 31 и 30, а также по совпадению единиц в этих триггерах. Последнее осуществляется с помощью элемента 37. Выходы элементов 32-36 через элемент ИЛИ 38 управляют запретом операции в блоке 16 и блоке 22. Кроме того, сигнал 43 запрета может быть подан через шестой вход элемента 38 с входа устройства. Ниже приведены

0 логические формулы, описьтающие работу коммутаторов 13 и 14 для слу- , чая выполнения короткой команды (сложения) и длинной команды (умножения), где приняты следующие

5 обозначения:

Управляющие сигналы: 2, - код операции Сложение 2q код операции Умножение. 0 Входные переменные:

Рд ,..., - циклы счетчика 12;

0 д 0 - синхросигналы с выхода генератора 11.

5 Выходные сигналы в магистрали 39 микрокоманд:

Операция Сложение (первое слагаемое в регистре 17, второе в блоке 22), Запись в регистр 18 сла , Запись суммы в гаемого - Zj регистр 17 - 2- AI Импульс конца операций - 2,ё-Ац Занесение знака (42) в блок 23 -Zh+i bCrfle 2(,+, - код операции, следующей за данной). Операция Умножение (множитель в регистре 17, множимое в блоке 22 Запись в регистр 18 - Z РО-О, Запись в регистр 19 -Z,- Запись единицы в регистр 17 (PI+Р + . ..+Piy), в этой операции логическое умножение на цифру анализируемого разряда множителя производится на одном из вентилей группы элементов 21(в зависимости от содержимого последнего разряда .регистра 19), Сдвиг вправо в регистре .+ ..., Сдвиг вправо в регистре 19 7.ц Oj., Формирование импульса конца операций - ZH Занесение знака (42) в блок 23 -diPo 18 Предложенное устройство-позволяв ет решать логические задачи выбора последовательности операции без использования операции Условный переход, что повышает информационную надежность, так как в формировании в этом случае не участвуют арифметико-логический блок и блок оперативной памяти, и позволяет понизить вероятность сбоев значительно. Постоянство рабочего цикла позволяет исключить из вычислителя оборудова- Ние, требующее точное время , для решения задач, например систему прерьгааний по меткам времени, упростить систему контроля вычислителя во время заводской настройки и регламентных работ при эксплуатации и методику обнаружения неисправности в связи со строгой последовательностью выполнения операций и отсутствием и вариантов циклов работы вычислителя, что повышает надежность цифрового вычислителя.

| Микропрограммное устройство управления | 1972 |

|

SU437073A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для избирательного управления с одного конца однопроводной линии несколькими реле | 1918 |

|

SU981A1 |

| Логарифмический усилитель | 1976 |

|

SU624239A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1984-02-23—Подача