Изобретение относится к импульсной технике и может применяться как элемент для вьшолнения логической функции И,И-НЕ и формирования выходного импульса по фронту нарастания входного сигнала.

Цель изобретения - расширение функциональных возможностей и повышение надежности работы элемента путем устранения зависимости уровня выходного короткого импульса и ослабление зависимости длительности этого импульса от длительности фронта входного сигнала.

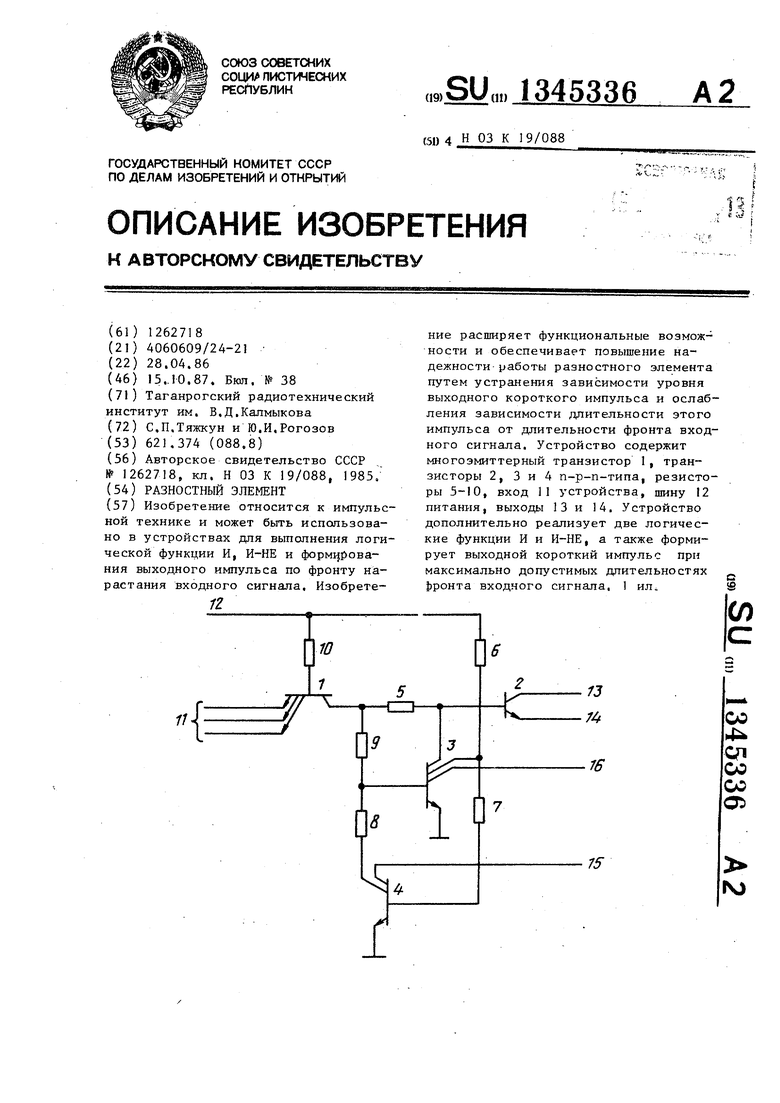

На чертеже приведена принципиальная схема разностного элемента.

.Разностный элемент содержит много- эмиттерный транзистор 1, первый, второй и третий п-р-п-транзисторы 2,3 и 4, резисторы 5-10, причем эмиттеры многоэмиттерного транзистора 1.подключены к входам 11 устройства, база п-р-п-транзистора 2 соединена с коллектором транзистора 3 и через вто-/ рой резистор 5 соединена с коллектором многоэмиттерного транзистора 1,. первый дополнительный коллектор п-р-п-транзистора 3 через шестой резистор 6 соединен с шиной 12 питания, ЗО связь первого дополнительного коллека через пятый резистор 7 - с базой п-р-п-транзистора 4, первый коллектор которого через четвертый резистор 8, соединен с базой п-р-п-транзистора 3, которая через третий резистор 9 соединена с коллектором многоэмиттерного транзистора 1, база которого через первый резистор 10 связана с шиной 12 питания, эмиттеры п-р-п- транзисторов 3 и 4 соединены с общей шиной, первый и второй выходы 13 и 14 подключены к коллектору и эмиттеру транзистора 2, второй коллектор транзистора 4 и второй дополнительный коллектор транзистора 3 соединены с первым и вторым дополнительными выходами 15и16..

Разностный элемент работает следующим образом.

В статическом режиме транзистор 2 закрыт, и на выходах 13 и 14 высокий или низкий уровень напряжения в зависимости от подключения транзистора 2 эмиттером к общей шине или коллектором к шине питания.

Если хотя бы на одном из входов 11 элеме.нта низкий уровень напряжения, то транзистор 3 закрыт, а транзистор 4 открыт и на выходах 16 и 15

формируется соответственно высокий И низкий уровень напряжения. Когда на всех входах 11 элемента высокий уровень напряжейия, транзистор 3 открыт, а транзистор 4 закрыт. На выходах 16 и 15 формируются низкий , и высокий уровни напряжения. Таким o6pa3OMj на втором дополнительном

коллекторе транзистора 3 реализуется сигнал, соответсвующий логической функции , а на втором коллекторе транзистора 4 - сигнал, соответствующий логической функции И.

На выходах 13 и 14 (коллектор или эмиттер транзистора 2) происходит формирование короткого импульса по фронту нарастания входного напряжения. При этом сначала протекает ток по цепи: шина 12 питания - переход база - коллектор транзистора 1 - резистор 5 - база транзистора 2. Через время задержки, определяемое лами резисторов 9 и 8, входной ем5 костью и напряжением U транзистора 3, начнется открывание транзистора 3. Процесс отпирания транзистора 3 протекает быстрее, поскольку суш:ествует положительная обратная

5

0

5

0

тора транзистора 3 через резистор 7, транзистор 4 и резистор 8 на базу транзистора 3.

Наличием этой обратной связи обусловлено ускоренное отпирание транзистора 3 и ускоренное запирание транзистора 2, так как в процессе переключения ток в базу транэистбра

3непрерывно возрастает до полного запирания транзистора- 4.

Гистерезисная входная хараткерис- тика схемы на транзисторах 3 и 4 (входом является резистор 9) ослабляет зависимость задержки этой схемы сзт длительности фронта входного сигнала устройства, Следовательно, ослабляется и зависимость длительности короткого выходного импульса устройства от названных факторов, что повьшгает надежность работы элемента.

Поскольку для срабатывания гисте- резисной схемы на транзисторах 3 и

4необходима большая амплитуда напря- д жения на Коллекторе транзистора 1,

то при любой длительности (особенно увеличенной) фронта входного сигнала отпирание транзистора 3 произойдет всегда после отпирания транзистора

5

0

2. В зависимости от включения транзистора 2 с выходом-коллектором или эмитте|)ом это произойдет после формиг рования на выходе уровня логического нуля или уровня логической единицы. Таким образом, элемент дополнительно реализует .две логические функции И, И-НЕ, а также формирует выходной короткий импульс при максимально допустимых длительностях фронта входного сигнала за счет устранения зависимости амплитуды и ослабления зависимости длительности короткого импульса от длительности фронта

вхолного сигнала.

Формула изобретения

Разностный элемент по авт. св. 1262718, отличающийся

тем, что, с целью расширения функциональных возможностей и повьшения надежности работы элемента, введены два резистора и третий п-р-п-тран- зистор, переход эмиттер - первый коллектор которого включен между четвертым резистором и общей шиной, первый дополнительный коллектор второго

п-р-п-транзистора соответственно через пятый и шестой резисторы соеди- , нен с шиной питания и базой четвертого п-ргП-транзистора, второй коллектор которого соединен с первым дополнительньм выходом устройства, а второй дополнительный коллектор второго п-р-п-Т анзистора соединен с вторым дополнительньм выходом устройст-, ва.

| название | год | авторы | номер документа |

|---|---|---|---|

| Разностный элемент | 1986 |

|

SU1345337A2 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Разностный элемент управления | 1974 |

|

SU500590A1 |

| Разностный элемент | 1988 |

|

SU1538247A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Формирователь импульсов | 1981 |

|

SU1026312A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах для выполнения логической функции И, И-НЕ и форм1|рова- ния выходного импульса по фронту нарастания входного сигнала. ИзобретеfZ /7 кие расширяет функциональные возможности и обеспечивает повышение надежности работы разностного элемента путем устранения зависимости уровня выходного короткого импульса и ослабления зависимости длительности этого импульса от длительности фронта входного сигнала. Устройство содержит многоэмиттерный транзистор 1, транзисторы 2, 3 и 4 п-р-п-типа, резисторы 5-10, вход 11 устройства, шину 12 питания, выходы 13 и 14. Устройство дополнительно реализует две логические функции И и И-НЕ, а также формирует выходной короткий импульс при максимально допустимых длительностях JjpoHTa входного сигнала. 1 ил. с (С (Л со 4; СП СО со О5 75 ГЧ)

| Авторское свидетельство СССР , № 1262718, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-15—Публикация

1986-04-28—Подача