1

Изобретение относится к импульсной технике и пред:;азначено для использования в системах цифровой автоматики .

Известно устройство - логическая схема с повышенным быстродействием, содержащее входной многоэмиттерный транзистор, база которого через первый резистор соединена с первой шиной питания, коллектор - с базой фазорасщепительного транзистора, эмиттер которого соединен с первым входом выходного каскада, диод с коллектором многоэмиттерного транзистора, коллектор - со вторым входом выходного каскада l .

Недостаток устройства- низкая помехоустойчивость.

Известно устройство, содержащее входной многоэмиттерный транзистор, эмиттеры которого соединены со входами устройства, коллектор через первый резистор с базой ключевого транзистора, коллектор которого соединен с базой многоэмиттерного выходного транзистора, коллектор которого через второй резистор соединен с шиной питания, первый эмиттер через диод - с выходом устройства и коллектором второго выходного

транзистора, база которого сое.цинена с эмиттером ключевого транзистора и через третий резистор с общей ши,ной, второй эмиттер многоэмиттерного

5 выходного транзистора через резистор соединен с базой транзистора обратной связи, коллектор которого через резистор соединен с базой ключевого транзистора, а эмиттер - с общей

10 ШИНОЙ 2.

Недостаток устройства - невысокое быстродействие и недостаточная помехоустойчивость.

Цель изобретения - повышение по( 5 мехоустойчивости и быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее входной многеэмиттерный транзистор, эмиттеры которого соединены со входами устройства, коллектор - со входом диодной сборки и через первый резистор с первой шиной питания, выход диодной сборки соединен с базой ключевого транзистора, коллектор которого соединен со входом выходного каскада, эмиттер - со второй шиной питания, дополнительно введены первый, второй и третий транзисторы, .и второй резистор, база первого транзистора соединена с коллектором и

базой ключевого транзистора, эмиттер - со второй шиной питания, коллектор - с эмиттером второго и базо третьего транзисторов, база второго транзистора соединена с коллектором третьего транзистора и базой входного многоэмиттерного транзистора, коллектор - с Эмиттером третьего транзистора и через второй резистор - с первой шиной .питания.

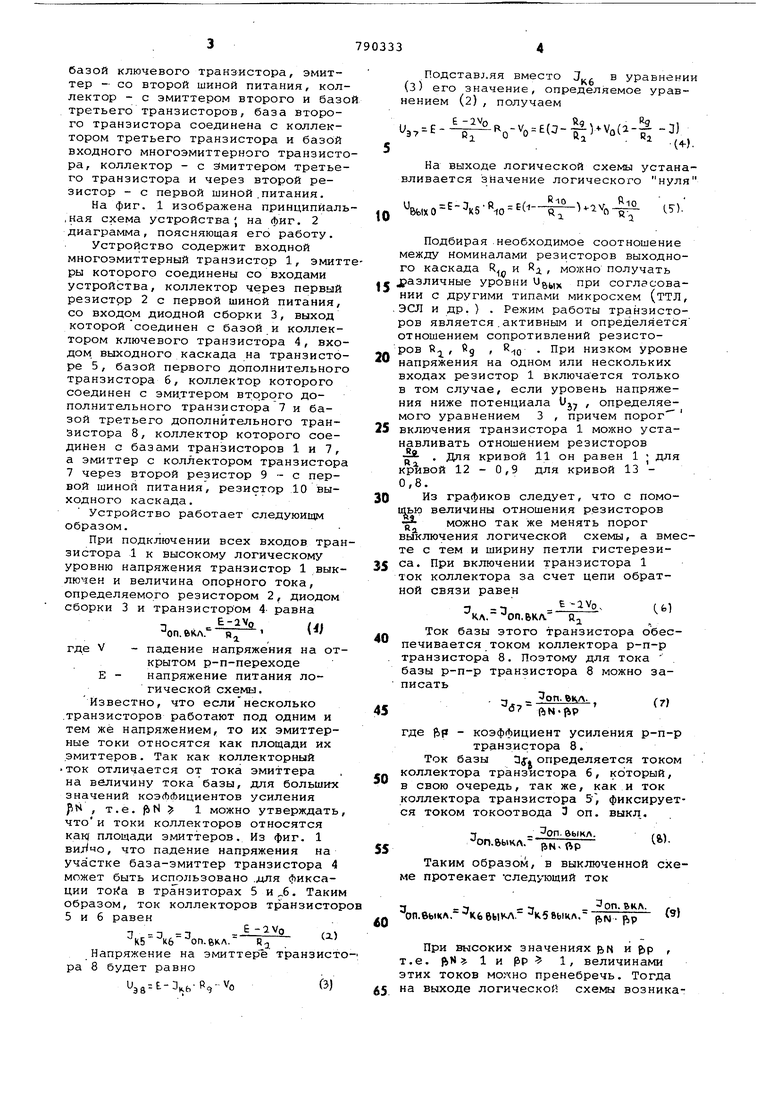

На фиг. 1 изображена принципйаль,ная схема устройства; на фиг. 2 диаграмма, поясняющая его работу.

Устройство содержит входной многоэмиттерный транзистор 1, эмиттры которого соединены со входами устройства, коллектор через первый резистор 2 с первой шиной питания, со входом диодной сборки 3, выход которой соединен с базой и коллектором ключевого транзистора 4, входом, выходного каскада на транзисторе 5, базой первого дополнительного транзистора б, коллектор которого соединен с эми.ттером вт.ррого дополнительного транзистора 7 и базой третьего дополнительного транзистора 8, коллектор которого соединен с базами транзисторов 1 и 7, а эмиттер с коллектором транзистора 7 через второй резистор 9 - с первой шиной питания, резистор 10 выходного каскада.

Устройство работает следуюищм образом.

При подключении всех входов транзистора 1 к высокому логическому уровню напряжения транзистор 1 выключен и величина опорного тока, определяемого резистором 2, диодом сборки 3 и транзистором 4- равна

E-aVo

(4/

on. 6КЛ.

где V

падение напряжения на открытом р-п-переходе

р напряжение питания логической схемы.

Известно, что если несколько .транзисторов работают под одним и тем же напряжением, то их эмиттерные токи относятся как площади их эмиттеров. Так как коллекторный ток отличается от тока эмиттера на величину тока базы, для больших значений коэЛфициентов усиления , т.е. N 1 можно утверждать, что и токи коллекторов относятся как} площади эмиттеров. Из фиг. 1 , что падение напряжения на участке база-эмиттер транзистора 4 может быть использовано .для фиксации в транзиторах 5 и „б. Таким образом, ток коллекторов транзистор 5 и б равен

Ё - 2 Vg

(i)

К5 кб оп.бкл.

«а

Напряжение на эмиттере транзистора 8 будет равно

СЗ)

эй-- - ьПодставд.яя вместо J в уравнении (З) его значение, определяемое уравнением (2) , получаем

(,()

Сь).

На выходе логической схемы устанавливается значение логического нуля

ВЬ,хО Е-Зк5-«.о-(-|7- Подбирая необходимое соотношение между номиналами резисторов выходного каскада R и йд. , можно получать

c J aзличныe уровни J6w Р согласовании с другими типами микросхем (ттл, ,ЭСЛ и др. ) . Режим работы транзисторов является . активнЕлм и определяется отношением сопротивлений резисторов R , fig , . при низком уровне

напряжения на одном или нескольких входах резистор 1 включается только в том случае, если уровень напряжения ниже потенциала Uj , определявмого уравнением 3 , причем порог

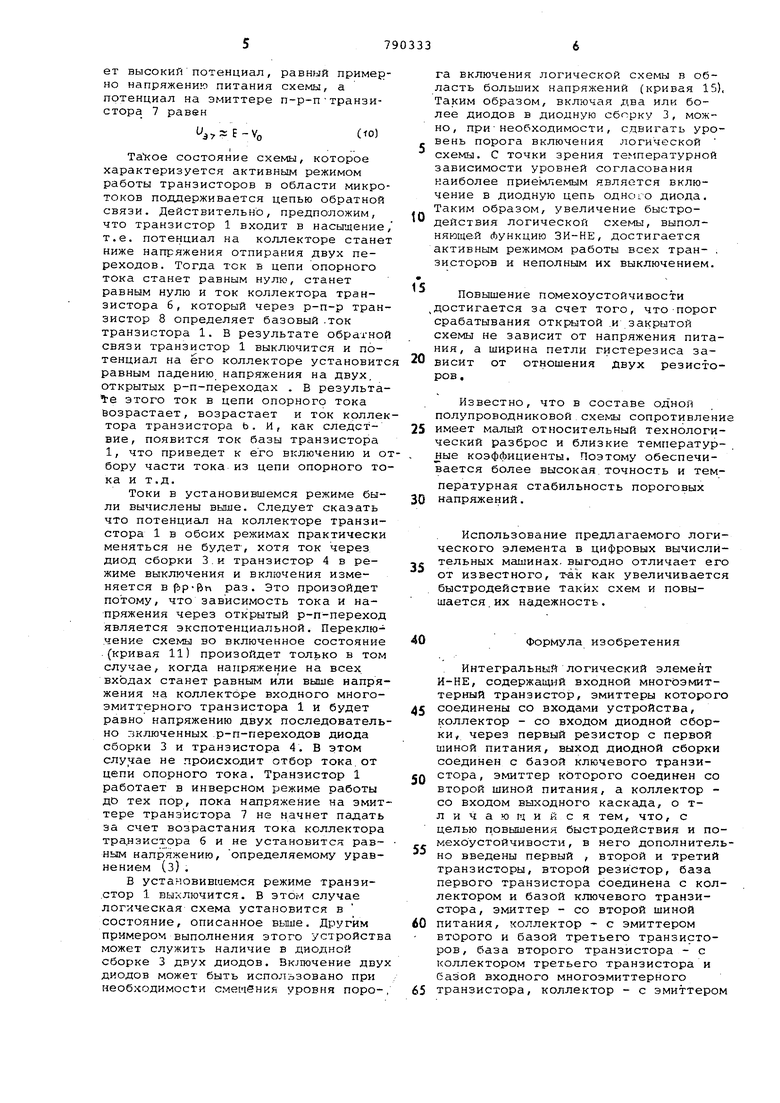

5 включения транзистора 1 можно устанавливать отношением резисторов . Для кривой 11 он равен 1 ; для кривой 12 - 0,9 для кривой 13 0,8.

0 Из графиков следует, что с помощью величины отношения резисторов можно так же менять порог выключения логической схемы, а вместе с тем и ширину петли гистерезиса. При включении транзистора 1 ток коллектора за счет цепи обратной связи равен

3 -т -:iVo. cfei

кл. оп.вкл Й-,

- 1

Ток базы этого транзистора обеспечивается током коллектора р-п-р . транзистора 8. Поэтому для тока базы р-п-р транзистора 8 можно записать

т оп. акл. /,) .JiP

где р)р - коэффициент усиления р-п-р

транзистора 8.

Ток базы , определяется током коллектора транзистора 6, который, в свою очередь, так же, как и ток коллектора транзистора 5, фиксируется током токоотвода 3 оп. выкл,.

. аыкл.

CW.

-оп.выкл.- pN.%P

Таким образом, в выключенной схепротекает следующий ток

Зол. вкл.

3.

(9)

-К.бвЫКЛЛ p,|v(. р,р

При высоких значениях BN и f)p , т.е. ftN 1и РР 1, величинами этих токов пренебречь. Тогда Й5 на выходе логической схемы возникает высокий потенциал, равный пример но напряжению питания схемы, а потенциал на эмиттере п-р-птранзистора 7 равен Е-У„ Такое состояние схемы, которое характеризуется активным режимом работы транзисторов в области микро токов поддерживается цепью обратной связи. Действительно, предположим, что транзистор 1 входит в насыщение т.е. потенциал на коллекторе станет ниже напряжения отпирания двух переходов. Тогда тек в цепи опорного тока станет равным нулю, станет равным нулю и ток коллектора транзистора 6, который через р-п-р транзистор 8 определяет базовый .ток транзистора 1. В результате обратной связи транзистор 1 выключится и потенциал на его коллекторе установитс равным падению напряжения на двух, открытых р-п-переходах . в результате этого ток в цепи опорного тока Возрастает, возрастает и ток коллек тора транзистора ь. и, как следствие, появится ток базы транзистора 1, что приведет к его включению и о бору части тока из цепи опорного то ка и т.д. Токи в установившемся режиме были вычислены выше. Следует сказать что потенциал на коллекторе транзистора 1 в обоих режимах практически меняться не будет-, хотя ток через диод сборки З.и транзистор 4 в режиме выключения и включения изменяется в (ip-fin раз. Это произойдет потому, что зависимость тока и напряжения через открытый р-п-переход является экспотенциальной. Переклю чение схемы во включенное состояние (кривая 11) произойдет только в том случае, когда напряжение на всех входах станет равным или выше напря жения на коллекторе входного многоэмиттерного транзистора 1 и будет равно напряжению двух последователь но гзключенных р-п-переходов диода сборки 3 и транзистора 4. В этом случае не происходит отбор тока.от цепи опорного тока. Транзистор 1 работает в инверсном режиме работы до тех пор, пока напряжение на эмит тере транзистора 7 не начнет падать за счет возрастания тока коллектора транзистора б и не установится равным напряжению, определяемому уравнением (з). В установившемся режиме транзи.стор 1 выключится. В этом случае логическая схема установится в состояние, описанное выше. Другим примером выполнения этого устройств может служить наличие в диодной сборке 3 двух диодов. Включение дву диодов может быть использовано при необходимости смеибния уровня порега включения логической схемы в область больших напряжений (кривая 15), Таким образом, включая два или более диодов в диодную сборку 3, можно , принеобходимости, сдвигать уровень порога включения логической схемы. С точки зрения температурной зависимости уровней согласования наиболее прием-пемым является включение в диодную цепь одного диода. Таким образом, увеличение быстродействия логической схемы, выполняющей Лункцию ЗИ-НЕ, достигается активным режимом работы всех тран- . зисторов и неполным их выключением. Повышение помехоустойчивости достигается за счет того, что-порог срабатывания открытой .и закрытой схемы не зависит от напряжения питания, а ширина петли гистерезиса зависит от отношения Двух резисторов. Известно, что в составе одной полупроводниковой схемы сопротивление имеет малый относительный технологический разброс и близкие температурные коэффициенты. Поэтому обеспечивается более высокая точность и температурная стабильность пороговых напряжений. Использование предлагаемого логического элемента в цифровых вычислительных машинах, выгодно отличает его от известного, т-ак как увеличивается быстродействие таких схем и повышается, их надежность. Формула изобретения Интегральный логический элемент И-НЕ, содержащий входной многоэмиттерный транзистор, эмиттеры которого соединены со входами устройства, коллектор - со входом диодной сборки, через первый резистор с первой шиной питания, выход диодной сборки соединен с базой ключевого транзистора, эмиттер которого соединен со второй шиной питания, а коллектор со входом выходного каскада, о тл и ч а ю m и PI с я тем, что, с целью цовышения быстродействия и помехоустойчивости, в него дополнительно введены первый , второй и третий транзисторы, второй резистор, база первого транзистора соединена с коллектором и базой ключевого транзистора, эмиттер - со второй шиной питания, коллектор - с эмиттером второго и базой третьего транзисторов, база второго транзистора - с коллектором третьего транзистора и базой входного многоэмиттерного транзистора, коллектор - с эмиттером

третьего транзистора и через второй резистор - с первс1й шиной питания .

Источники информации, принятые во внимание при экспертизе

1.Шагурин И.И. Транзисторнотранзисторные логические схемы.М., 1974, с. 93.

2.Наумов Ю. Е. и др. Помехоустойчивость устройств на интегральных логических схемах.,М. ,1975,с.68.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Входное устройство схемы сранения токов | 1985 |

|

SU1363452A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Ассоциативный запоминающий элемент | 1983 |

|

SU1130900A1 |

| Устройство согласования интегральных инжекционных схем с линиями передачи коллективного пользования | 1983 |

|

SU1092726A1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| Транзисторно-транзисторный инвертор | 1989 |

|

SU1651372A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Устройство для формирования разрядных токов записи | 1988 |

|

SU1550581A1 |

| Универсальный многозначный логический элемент | 1978 |

|

SU746904A1 |

s. т W 24

ф1А1.г

Авторы

Даты

1980-12-23—Публикация

1978-08-14—Подача