Изобретение относится к импульсной , технике и может быть использовано в составе БИС-систем сбора и обработки информации в качестве функционального элемента последовательностных устройств.

Цель изобретения - повышение помехоустойчивости триггера,

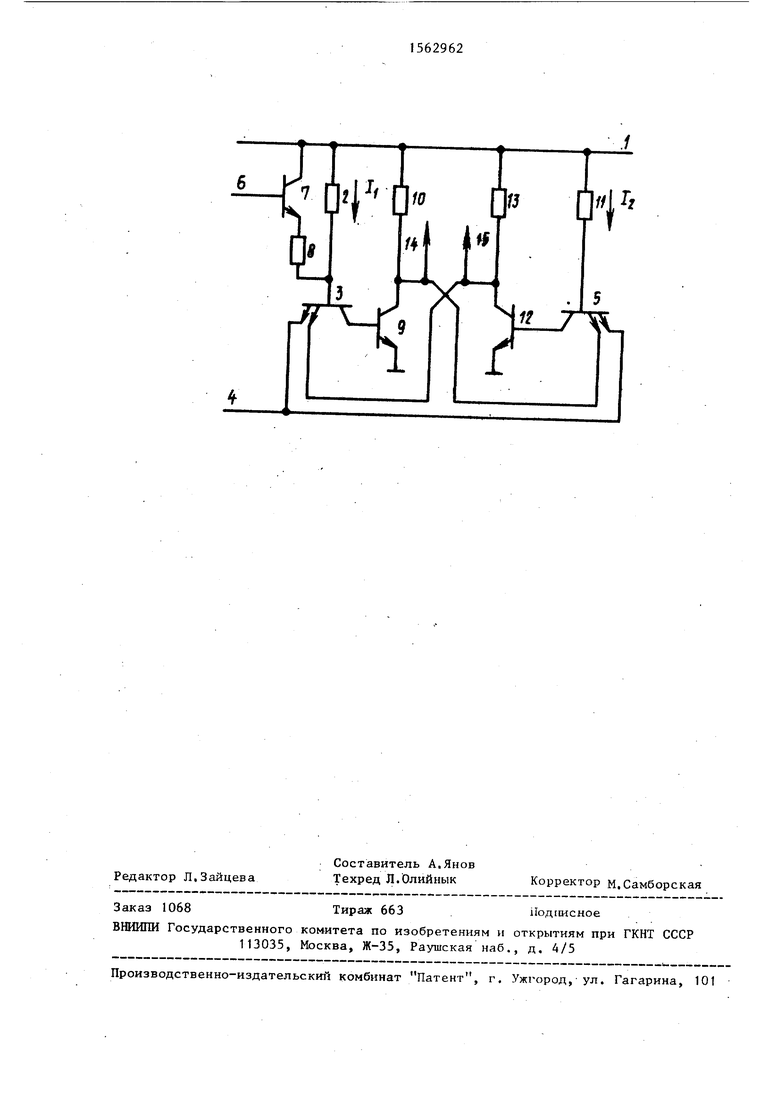

На чертеже приведена принципиальная, электрическая схема D-триггера ТТЛ-типа,

D-триггер содержит шину 1 питания., которая через второй резистор 2 соединена с базой первого многоэмиттерного транзистора 3, первый эмиттер которого соединен с тактовой шиной 4 и с первым эмиттером второго многоэмиттерного транзистора 5, D-вход 6 соединен с базой третьего транзистора 7, коллектор которого соединен с шиной I питания, а эмиттер через четвертый резистор 8 с базой транзистора 7,

коллектор которого соединен с базой первого транзистора 9, эмиттер которого соединен с шиной нулевого потен- циала, а коллектор - с первым выводом первого резистора 10 и вторым эмиттером транзистора 5, база которого через третий резистор 11 соединена с шиной питания 1, а коллектор - с базой второго транзистора j2, эмитхер которого соединен с нулевого потенциала, второй змиттер транзистора 3 соединен с коллектором транзистора 12 и первым выводом пятого резистора 13, второй вывод которого соединен с вторым выводом резистора 10 и шиной 1 питания, инверсный и прямой выходы 14 и 15 устройства собтветст- венно соединены с коллекторами транзисторов 9 и 12, .

D-триггер работает следующим образом.

31

Если на шине 4 логическая единица, то D-триггер находится в режиме хранения, причем изменение уровня сигнала

D-входе 6 будет изменять лишь вход

6 и не влияет иа

на

ной ток транзистора

состояние- триггера,

С приходом тактового импульса базовые токи транзисторов 9 и 12 будут отбираться тактовой шиной 4, при этом транзисторы 9 и 12 будут закрыты по заднему фронту тактового импульса (переход из состояния 0 в 1)| в базу . транзистора 12 будет втекать ток, рав ный 1г, а в базу транзистора 9 будет втекать ток Г.,. Если на входе 6 логический ноль, то в базу транзистора .9 будет втекать ток (так как транзистор 7 будет закрыт) . Быстрее от

кроется транзистор 12 и через свой откры-20 го двухэмиттерного транзистора, пертый коллектор отберет ток с входа транзистора 9, В этом случае на прямом выходе 15 триггера мы будем иметь сигнал низкого логического уровня. Если на входе 6 логическая единица (транзистор 7 открыт, через него протекает ток I3)i то в базу транзистора 9 будет втекать ток равный Ij+Ij I, поэтому по заднему фронту тактового импульса быстрее откроется транзистор 9 и через свой коллектор отберет входной ток транзистора 12, который закрое-тся. Следовательно, на выходе 15 сформируется сигнал высокого логического уровня. После установки триггера в одно из устойчивых состояний, он переходит в режим хранения до прихода следующего тактового импульса.

25

30

35

вый вывод третьегд резистора соединен с шиной питания, отлич а ю - пг и и с я тем, что, с целью повышения помехоустойчивости триггера, введены четвертый, пятый резисторы и третий n-p-n-транэистор, коллектор которого соединен с шиной питания, база - с D-входом D-триггера, а эмиттер через четвертый резистор соединен с базой первого двухэмиттерного транзистора, коллектор первого п р-п-транзистора соединен с вторым эмиттером второго двухэмиттерного транзистора, эмиттер второго п-р-п транзистора - с шиной нулевого потенциала, а коллектор -ч с прямым выходом D-триггера, вторым эмиттером первого двухэмиттерного транзистора и через пятый резистор подключен к шине питания, второй вывод третьего резистора соединен с базой второго двухэмиттерного транзистора.

Таким образом, предлагаемое устрой- ство реализует функции D-триггера, имеющего повышенную помехоустойчивость

и стандартные уровни,,

выходные логические

Формула изобретения

D-триггер, содержащий два двухэмит- терных и два n-p-n-транзистора, три резистора, причем первые эмиттеры

двухэмиттерных транзисторов соединены с тактовой шиной, а их коллекторы соответственно соединены с базами первого и второго п-р-п-транзисторов, эмиттер первого n-p-n-транэистора соединен с. шиной нулевого потенциала, а коллектор подключен к инверсному выходу и через первый резистор соединен с шиной питания, которая через второй резистор соединена с базой перво

5

0

5

вый вывод третьегд резистора соединен с шиной питания, отлич а ю - пг и и с я тем, что, с целью повышения помехоустойчивости триггера, введены четвертый, пятый резисторы и третий n-p-n-транэистор, коллектор которого соединен с шиной питания, база - с D-входом D-триггера, а эмиттер через четвертый резистор соединен с базой первого двухэмиттерного транзистора, коллектор первого п р-п-транзистора соединен с вторым эмиттером второго двухэмиттерного транзистора, эмиттер второго п-р-п транзистора - с шиной нулевого потенциала, а коллектор -ч с прямым выходом D-триггера, вторым эмиттером первого двухэмиттерного транзистора и через пятый резистор подключен к шине питания, второй вывод третьего резистора соединен с базой второго двухэмиттерного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Триггерный логический элемент И-НЕ | 2018 |

|

RU2694151C1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

| @ -Триггер (его варианты) | 1984 |

|

SU1188861A1 |

| Универсальная двоичная ячейка | 1988 |

|

SU1676068A1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Триггерный логический элемент И | 2022 |

|

RU2802370C1 |

Изобретение относится к импульсной технике и может быть использовано в составе БИС-систем сбора и обработки информации в качестве функционального элемента последовательностных устройств. Целью изобретения является повышение помехоустойчивости D-триггера. D-триггер содержит два двухэмиттерных и два N - P - N-транзистора, пять резисторов. Введение двух резисторов и новых связей позволяет повысить помехоустойчивость D-триггера путем обеспечения стандартных уровней напряжения на входах и выходах. 1 ил.

| Логическое устройство | 1985 |

|

SU1262693A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Алексенко А,Г,, Шагурин И.И, Микросхемотехника | |||

| -М,: Радио и связь, 1982, с | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-05-07—Публикация

1988-04-13—Подача