Изобретение относится к вычислительной технике и автоматике, может быть использовано в системах для отображения информации на экране электронно-лучевой трубки (ЭЛТ) и является усовершенствованием изобретения по авт.св. № 528589.

Цель изобретения - повьпяение быстродействия устройства.

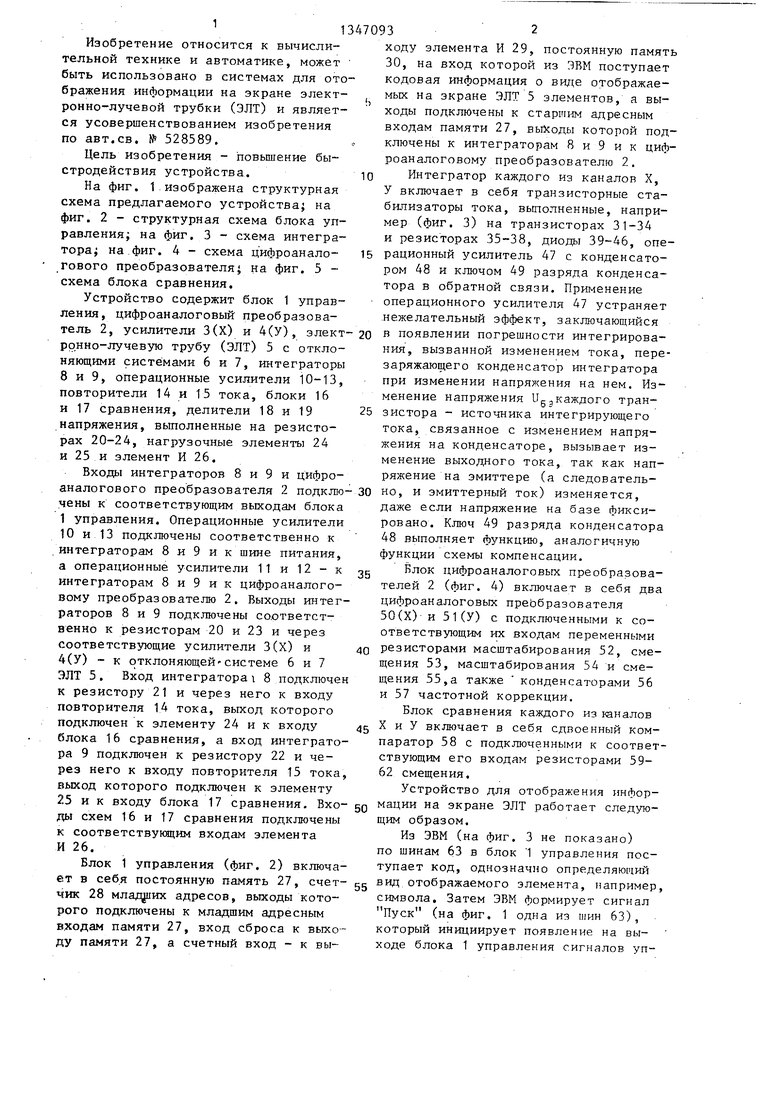

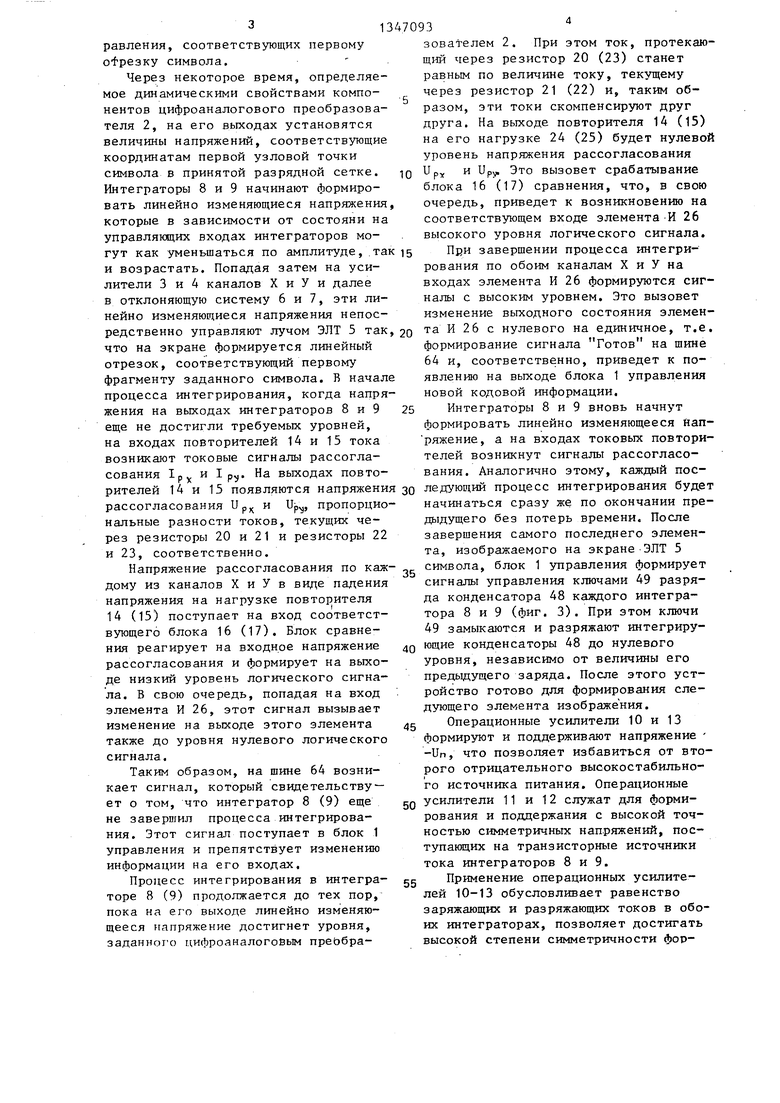

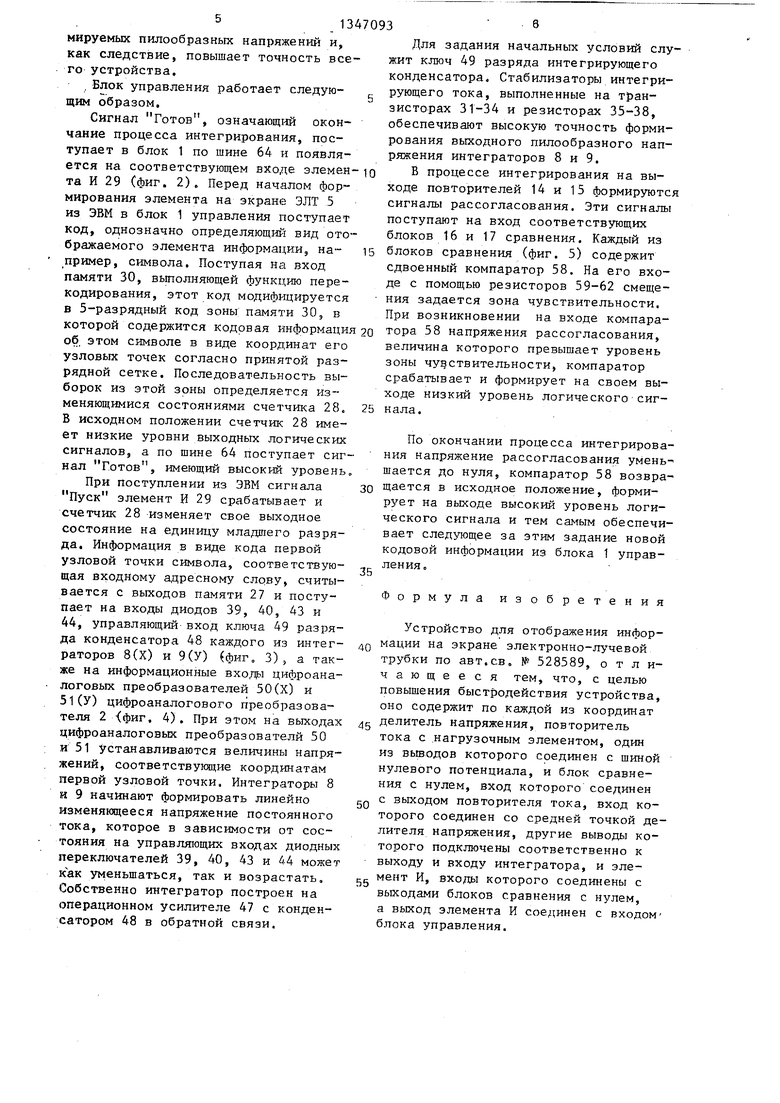

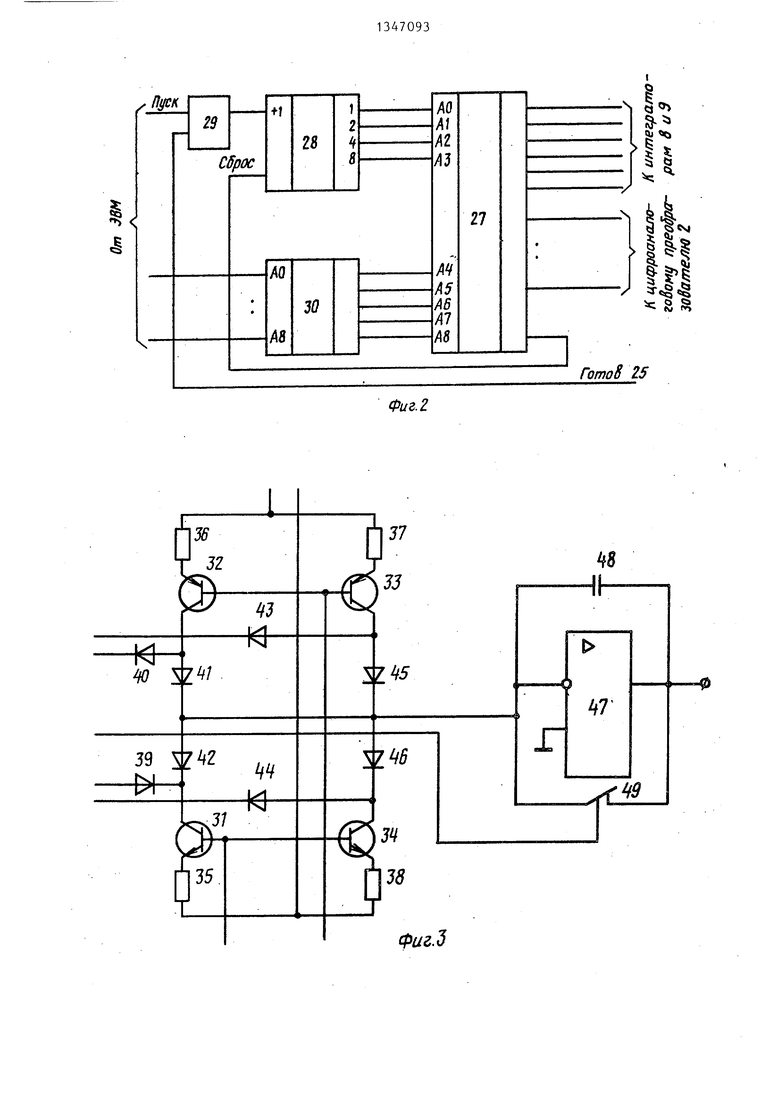

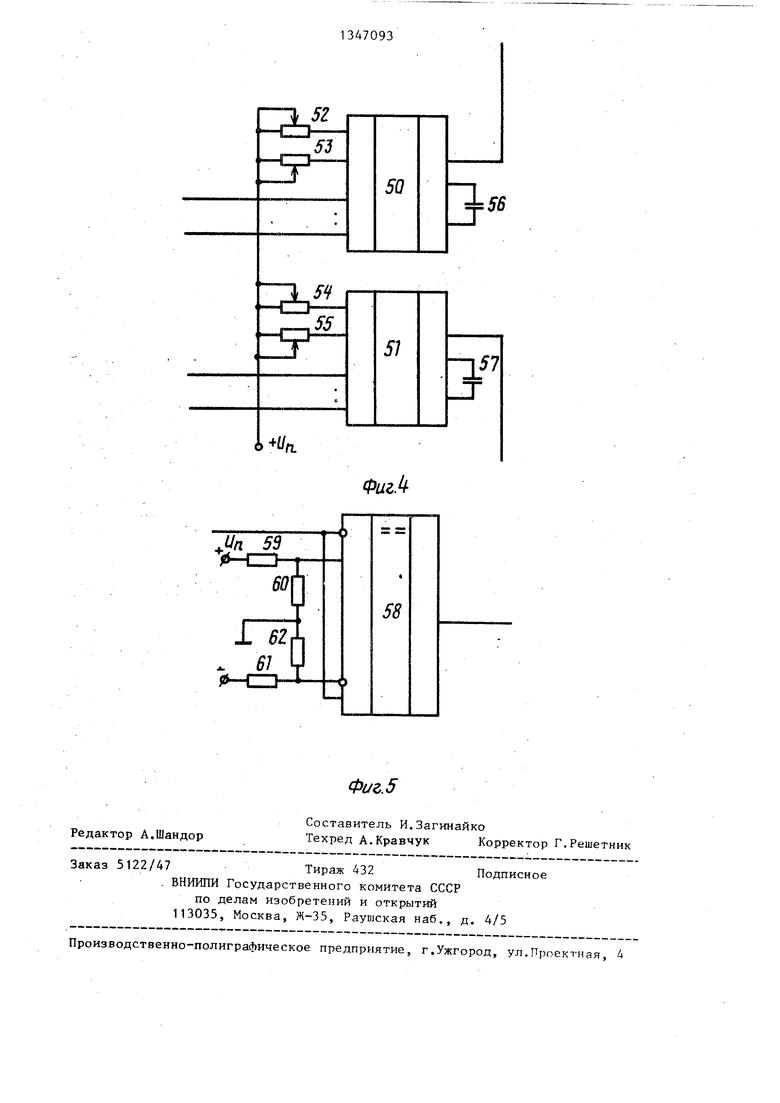

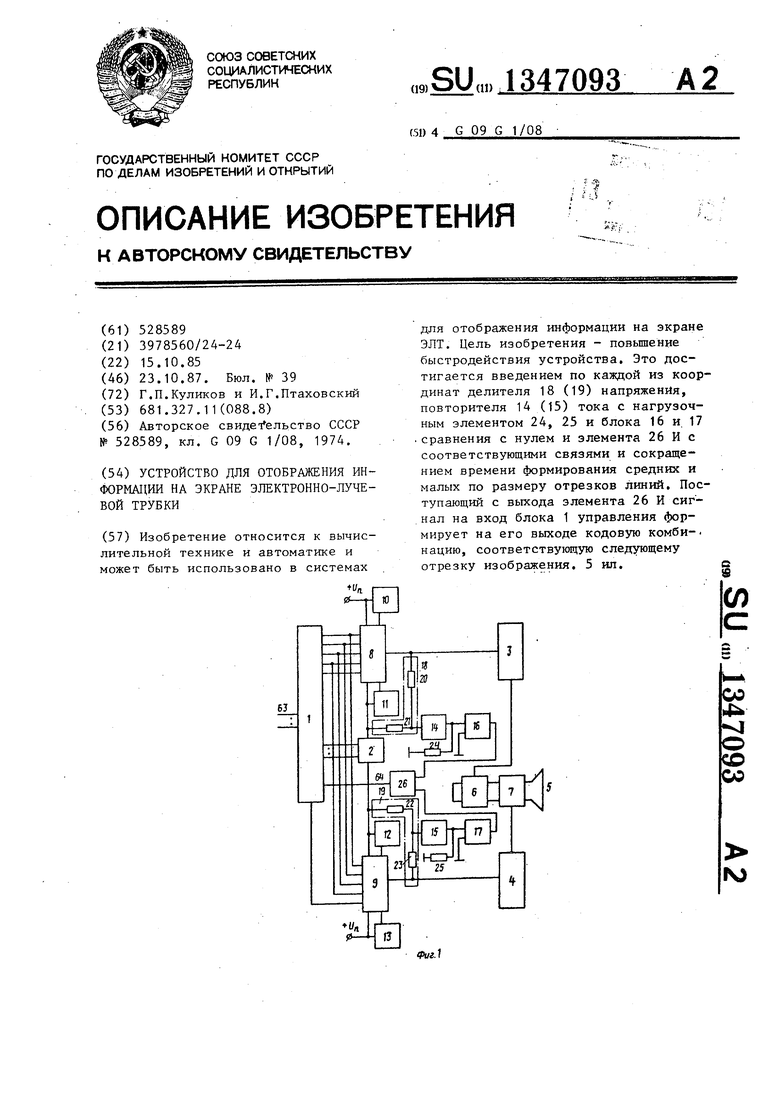

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока управления; на фиг. 3 - схема интегратора; на фиг. 4 - схема цифроанало- гового преобразователя; на фиг. 5 - схема блока сравнения.

Устройство содержит блок 1 управления, цифроаналоговый преобразоваходу элемента И 29, постоянную память 30, на вход которой из ЭВМ поступает кодовая информация о виде отображаеJ мьк на экране ЭЛТ 5 элементов, а выходы подключены к старшим адресным входам памяти 27, вьйсоды которой подключены к интеграторам 8 и 9 и к циф- роаналоговому преобразователю 2.

1Q Интегратор каждого из каналов X, У включает в себя транзисторные стабилизаторы тока, выполненные, например (фиг. 3) на транзисторах 31-34 и резисторах 35-38, диоды 39-46, опе15 рационный усилитель 47 с конденсатором 48 и ключом 49 разряда конденсатора в обратной связи. Применение - операционного усилителя 47 устраняет .нежелательный эффект, заключающийся

тель 2, усилители 3(Х) и 4(У), элект-20 появлении погрешности интегрирова- рр.нно-лучевую трубу (ЭЛТ) 5 с отклоняющими системами 6 и 7, интеграторы 8 и 9, операционные усилители 10-13, повторители 14 и 15 тока, блоки 16 и 17 сравнения, делители 18 и 19 25 напряжения, выполненные на резисторах 20-24, нагрузочные элементы 24 и 25 и элемент И 26.

Входы интеграторов 8 и 9 и цифрония, вызванной изменением тока, перезаряжающего конденсатор интегратора при изменении напряжения на нем. Изменение напряжения Uggкаждого транзистора - источника интегрирующего тока, связанное с изменением напряжения на конденсаторе, вызывает изменение выходного тока, так как напряжение на эмиттере (а следовательаналогового преобразователя 2 подклю- 30 но, и эмиттерпый ток) изменяется.

чены к соответствующим выходам блока 1 управления. Операционные усилители 10 и 13 подключены соответственно к интеграторам 8 и 9 и к шине питания, а операционные усилители 11 и 12 - к интеграторам 8 и 9 и к цифроаналого- вому преобразователю 2. Выходы интеграторов 8 и 9 подключены соответственно к резисторам 20 и 23 и через соответствующие усилители 3(Х) и 4(У) - к отклоняющей системе 6 и 7 ЗЛТ 5. Вход интегратора 8 подключен к резистору 21 и через него к входу повторителя 14 тока, выход которого подключен к элементу 24 и к входу блока 16 сравнения, а вход интегратора 9 подключен к резистору 22 и через него к входу повторителя 15 тока, выход которого подключен к элементу 25 и к входу блока 17 сравнения. Входы схем 16 и 17 сравнения подключены к соответствугацим входам элемента И 26.

Блок 1 управления (фиг. 2) включает в себя постоянную память 27, счет- gg вид отображаемого элемента, например, чик 28 младших адресов, выходы кото- символа. Затем ЭВМ формирует сигнал

Пуск (на фиг. 1 одна из шин 63), который инициирует появление на вырого подключены к младшим адресным входам памяти 27, вход сброса к выходу памяти 27, а счетный вход - к выходе блока 1 управления сигналов упходу элемента И 29, постоянную память 30, на вход которой из ЭВМ поступает кодовая информация о виде отображаемьк на экране ЭЛТ 5 элементов, а выходы подключены к старшим адресным входам памяти 27, вьйсоды которой подключены к интеграторам 8 и 9 и к циф- роаналоговому преобразователю 2.

Интегратор каждого из каналов X, У включает в себя транзисторные стабилизаторы тока, выполненные, например (фиг. 3) на транзисторах 31-34 и резисторах 35-38, диоды 39-46, операционный усилитель 47 с конденсатором 48 и ключом 49 разряда конденсатора в обратной связи. Применение операционного усилителя 47 устраняет .нежелательный эффект, заключающийся

появлении погрешности интегрирова-

ния, вызванной изменением тока, перезаряжающего конденсатор интегратора при изменении напряжения на нем. Изменение напряжения Uggкаждого транзистора - источника интегрирующего тока, связанное с изменением напряжения на конденсаторе, вызывает изменение выходного тока, так как напряжение на эмиттере (а следователь5

0

5

0

даже если напряжение на базе фиксировано. Ключ 49 разряда конденсатора 48 выполняет функцию, аналогичную функции схемы компенсации.

Блок цифроаналоговых преобразователей 2 (фиг. 4) включает в себя два цифроаналоговых преЬбразователя 50(X)- и 51(У) с подключенными к соответствующим их входам переменными резисторами масштабирования 52, смещения 53, масштабирования 54 и смещения 55,а также конденсаторами 56 и 57 частотной коррекции.

Блок сравнения каждого из ганалов X и У включает в себя сдвоенный компаратор 58 с подключенными к соответствующим его входам резисторами 59- 62 смещения.

Устройство для отображения информации на экране ЭЛТ работает следующим образом.

Из ЭВМ (на фиг. 3 не показано) по шинам 63 в блок 1 управления поступает код, однозначно определяющий

ходе блока 1 управления сигналов управления, соответствующих первому отрезку символа.

Через некоторое время, определяемое динамическими свойствами компонентов цифроаналогового преобразователя 2, на его выходах установятся величины напряжений, соответствующие координатам первой узловой точки символа в принятой разрядной сетке. Интеграторы 8 и 9 начинают формировать линейно изменяющиеся напряжения которые в зависимости от состояни на управляющих входах интеграторов могут как уменьшаться по амплитуде, та и возрастать. Попадая затем на усилители 3 и 4 каналов X и У и далее в отклоняющую систему 6 и 7, эти лиUp и Upy. Это вызовет срабатывание блока 16 (17) сравнения, что, в свою очередь, приведет к возникновению на соответствующем входе элемента-И 26 высокого уровня логического сигнала. При завершении процесса интегрирования по обоим каналам X и У на входах элемента И 26 формируются сигналы с высоким уровнем. Это вызовет изменение выходного состояния элеменнейно изменяющиеся напряжения непосредственно управляют лучом ЭЛТ 5 так, 20 та И 26 с нулевого на единичное, т.е. что на экране формируется линейный формирование сигнала Готов на шине отрезок, соответствующий первому фрагменту заданного символа. В начале процесса интегрирования, когда напряжения на выходах интеграторов 8 и 9 25

64 и, соответственно, приведет к появлению на выходе блока 1 управления новой кодовой информации.

Интеграторы 8 и 9 вновь начнут формировать линейно изменяющееся напряжение, а на входах токовых повторителей возникнут сигналы рассогласования. Аналогично этому, каждый посеще не достигли требуемых уровней, на входах повторителей 14 и 15 тока возникают токовые сигналы рассогла- I р,,. На выходах повтосования IPX

Интеграторы 8 и 9 вновь начнут формировать линейно изменяющееся напряжение, а на входах токовых повторителей возникнут сигналы рассогласования. Аналогично этому, каждый посрителей l4 и 15 появляются напряжения зо ледующий процесс интегрирования будет

рассогласования Up и Uj,, пропорциональные разности токов, текущих через резисторы 20 и 21 и резисторы 22 и 23, соответственно.

45

Напряжение рассогласования по каж- „ символа, блок 1 управления формирует сигналы управления ключами 49 разряда конденсатора 48 каждого интегратора 8 и 9 (фиг. 3). При этом ключи 49 замыкаются и разряжают интегриру- 40 ющие конденсаторы 48 до нулевого уровня, независимо от величины его предыдущего заряда. После этого устройство готово для формирования следующего элемента изображения.

Операционные усилители 10 и 13 формируют и поддерживают напряжение - -Un, что позволяет избавиться от второго отрицательного высокостабильного источника питания. Операционные gQ усилители 11 и 12 служат для формирования и поддержания с высокой точностью симметричных напряжений, поступающих на транзисторные источники тока интеграторов 8 и 9.

Применение операционных усилителей 10-13 обусловливает равенство заряжающих и разряжающих токов в обоих интеграторах, позволяет достигать высокой степени симметричности фордому из каналов X и У в виде падения напряжения на нагрузке повто1зителя 14 (15) поступает на вход соответствующего блока 16 (17). Блок сравнения реагирует на входное напряжение рассогласования и формирует на выходе низкий уровень логического сигнала. В свою очередь, попадая на вход элемента И 26, этот сигнал вызывает изменение на выходе этого элемента также до уровня нулевого логического сигнала.

Таким образом, на шине 64 возникает сигнал, который свидетельствует о том, что интегратор 8 (9) еще не завершил процесса интегрирования. Этот сигнал поступает в блок 1 управления и препятствует изменению информации на его входах.

Процесс интегрирования в интеграторе 8 (9) продолжается до тех пор, пока на его выходе линейно изменяющееся напряжение достигнет уровня, заданног о цифроаналогобым преобра55

д 15

7093

зователем 2. При этом ток, протекающий через резистор 20 (23) станет равным по величине току, текущему через резистор 21 (22) и, таким образом, эти токи скомпенсируют друг друга. На выходе повторителя 14 (15) на его нагрузке 24 (25) будет нулевой уровень напряжения рассогласования

Up и Upy. Это вызовет срабатывание блока 16 (17) сравнения, что, в свою очередь, приведет к возникновению на соответствующем входе элемента-И 26 высокого уровня логического сигнала. При завершении процесса интегрирования по обоим каналам X и У на входах элемента И 26 формируются сигналы с высоким уровнем. Это вызовет изменение выходного состояния элемента И 26 с нулевого на единичное, т.е. формирование сигнала Готов на шине

та И 26 с нулевого на единичное, т.е. формирование сигнала Готов на шине

64 и, соответственно, приведет к появлению на выходе блока 1 управления новой кодовой информации.

Интеграторы 8 и 9 вновь начнут формировать линейно изменяющееся напряжение, а на входах токовых повторителей возникнут сигналы рассогласования. Аналогично этому, каждый посначинаться сразу же по окончании предыдущего без потерь времени. После завершения самого последнего элемента, изображаемого на экране ЭЛТ 5

45

gQ

55

мируемых пилообразных напряжений и, как следствие, повышает точность всего устройства.

Блок управления работает следую-

щим образом.

Сигнал Готов, означающий окончание процесса интегрирования, поступает в блок 1 по шине 64 и появляется на соответствующем входе элемен та И 29 (фиг. 2)е Перед началом формирования элемента на экране ЭЛТ 5 из ЭВМ в блок 1 управления поступает код, однозначно определяющий вид отображаемого элемента информации, на- пример, символа. Поступая на вход памяти 30, вьтолняющей функцию перекодирования, этот код модифицируется в 5-разрядный код зоны памяти 30, в которой содержится кодовая информаци об, этом символе в виде координат его узловых точек согласно принятой разрядной сетке. Последовательность выборок из этой зоны определяется изменяющимися состояниями счетчика 28. В исходном положении счетчик 28 имеет низкие уровни выходных логических сигналов, а по шине 64 поступает сигнал Готов, имеющий высокий уровень

При поступлении из ЭВМ сигнала Пуск элемент И 29 срабатывает и счетчик 28 изменяет свое выходное состояние на единицу младпюго разряда. Информация в виде кода первой узловой точки символа, соответствующая входному адресному слрву, считывается с выходов памяти 27 и поступает на входы диодов 39, 40, 43 и 44, управляющий- вход ключа 49 разряда конденсатора 48 каждого из интег

раторов 8{Х) и 9(у) (фиг, 3), а также на информационные входы цифроана- логовых преобразователей 50(X) и 51(У) цифроаналогового преобразователя 2 -(фиг. 4). При этом на выходах цифроаналоговых преобразователи 50 и 51 Устанавливаются величины напряжений, соответствукяцие координатам первой узловой точки. Интеграторы 8 и 9 начинают формировать линейно изменяющееся напряжение постоянного тока, которое в зависимости от состояния на управляющих входах диодных переключателей 39, 40, 43 и 44 может к ак уменьшаться, так и возрастать, Собственно интегратор построен на операционном усилителе 47 с конденсатором 48 в обратной связи.

5

0

5

0

5

0

5

Для задания начальных условий служит ключ 49 разряда интегрирующего конденсатора. Стабилизаторы интегрирующего тока, выполненные на транзисторах 31-34 и резисторах 35-38, обеспечивают высокую точность формирования выходного пилообразного напряжения интеграторов 8 и 9.

В процессе интегрирования на выходе повторителей 14 и 15 формируются сигналы рассогласования. Эти сигналы поступают на вход соответствующих блоков 16 и 17 сравнения. Каждый из блоков сравнения (фиг. 5) содержит сдвоенный компаратор 58. На его входе с помощью резисторов 59-62 смещения задается зона чувствительности. При возникновении на входе компаратора 58 напряжения рассогласования, величина которого превышает уровень зоны чувствительности, компаратор срабатывает и формирует на своем выходе низкий уровень логического сигнала.

По окончании процесса интегрирования напряжение рассогласования умень- шается до нуля, компаратор 58 возвращается в исходное положение, формирует на вькоде высокий уровень логического сигнала и тем самым обеспечивает следующее за этим задание новой кодовой информации из блока 1 управления.

Формула изобретения

Устройство для отображения информации на экране электронно-лучевой трубки по авт.св. № 528589, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит по каждой из координат делитель напряжения, повторитель тока с нагрузочным элементом, один из выводов которого соединен с шиной нулевого потенциала, и блок сравнения с нулем, вход которого соединен с выходом повторителя тока, вход которого Соединен со средней точкой делителя напряжения, другие выводы которого подключены соответственно к выходу и входу интегратора, и элемент И, входы которого соединены с выходами блоков сравнения с нулем, а выход элемента И соединен с входом- блока управления.

х

I

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU920820A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1974 |

|

SU528589A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1654862A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1985 |

|

SU1304014A1 |

| Генератор векторов | 1984 |

|

SU1257698A1 |

| Интегратор с управляемым ограничением выходного сигнала | 1986 |

|

SU1305724A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в системах п. 0- 6J для отображения информации на экране ЭЛТ. Цель изобретения - повьшение быстродействия устройства. Это достигается введением по каждой из координат делителя 18 (19) напряжения, повторителя 14 (15) тока с нагрузочным элементом 24, 25 и блока 16 и 17 сравнения с нулем и элемента 26 И с соответствующими связями и сокращением времени формирования средних и малых по размеру отрезков линий. Поступающий с выхода элемента 26 И сигнал на вход блока 1 управления формирует на его выходе кодовую комби-- нацию, соответствующую следующему отрезку изображения. 5 ил. (Л а № С « СО 4ib О СО оо 23 ши 25 к

56

J

8

W 3Z

-й

3745

0

г

f

4

Фиг.З

SQ

4 55

51

T/7

Редактор А.Шандор

Ф1/г.5

Составитель И.Загинайко

Техред А.Кравчук Корректор Г.Решетник

Заказ 5122/47

Тираж 432Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фиг.

| Устройство для отображения информации на экране электронно-лучевой трубки | 1974 |

|

SU528589A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-10-23—Публикация

1985-10-15—Подача