Ичпбр 1тиие fiTiidciiTCH к гтк циялиЧИрОПЛН11,1М ||Иф15(Ч0.1М ИЫЧИСЛИТОЛЬТК.ГМ

(i)icTr, , п1) ЧИЯЧО11ИЫМ ;и1я nil- lie лслс иия с г,-)тис гич1м:ких харпкт срис- тик случаГшых npi iiC CccMi.

Цель из()Г)ретс Лия - iioni.пнемте бр.1С- т р()дей(1 ни ycT pniicTii,-,

Ллго))нтм усредиелия чи.ччели) X следукици :

WлI

п 1

+ 2

если : f Г1 ,; ,,.1 ;

где

если К С

+

- 1

КП.НИЧеСТВО )Of, ni)H КОто 1Ь Х имгкт. шястси условие

N :,.,, ;,. - п;

U - . J - i- интерплл иостояистна

г; „, i - 0,1,2,3...; К - номер ялмсра в интернале

иостояястна И,, (для первого замера К О) .

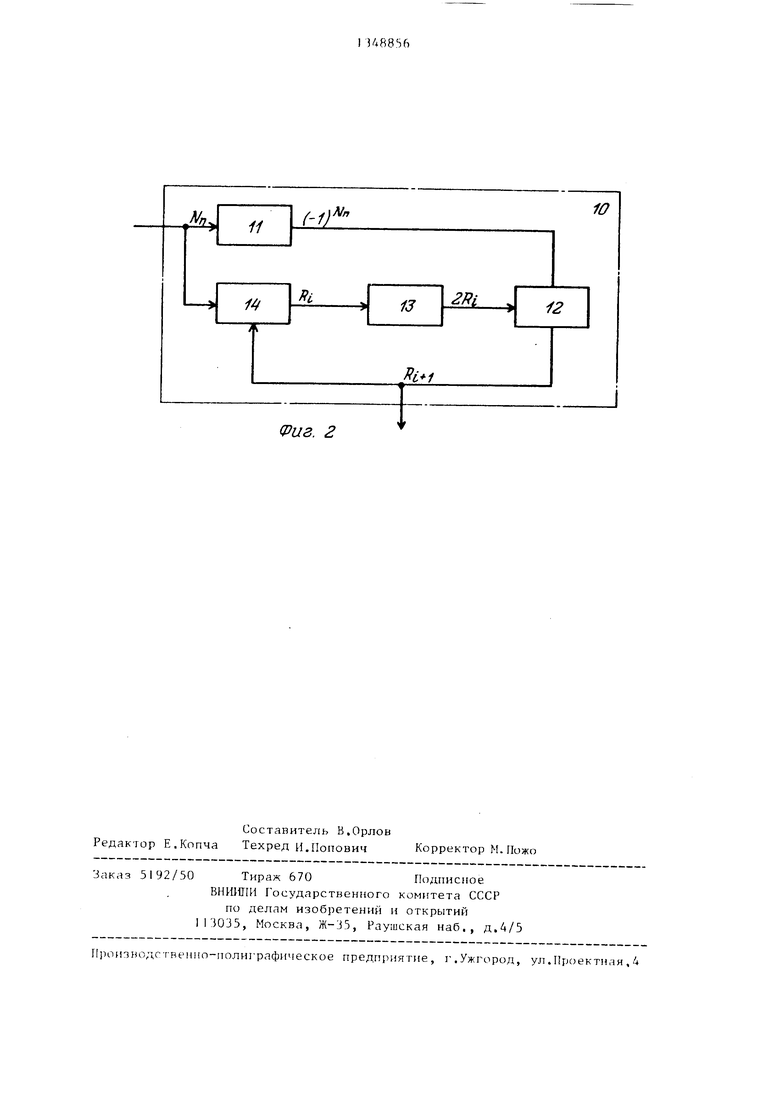

Значения переменных алгоритма дли первых ) замеров принеде ы в таблице.

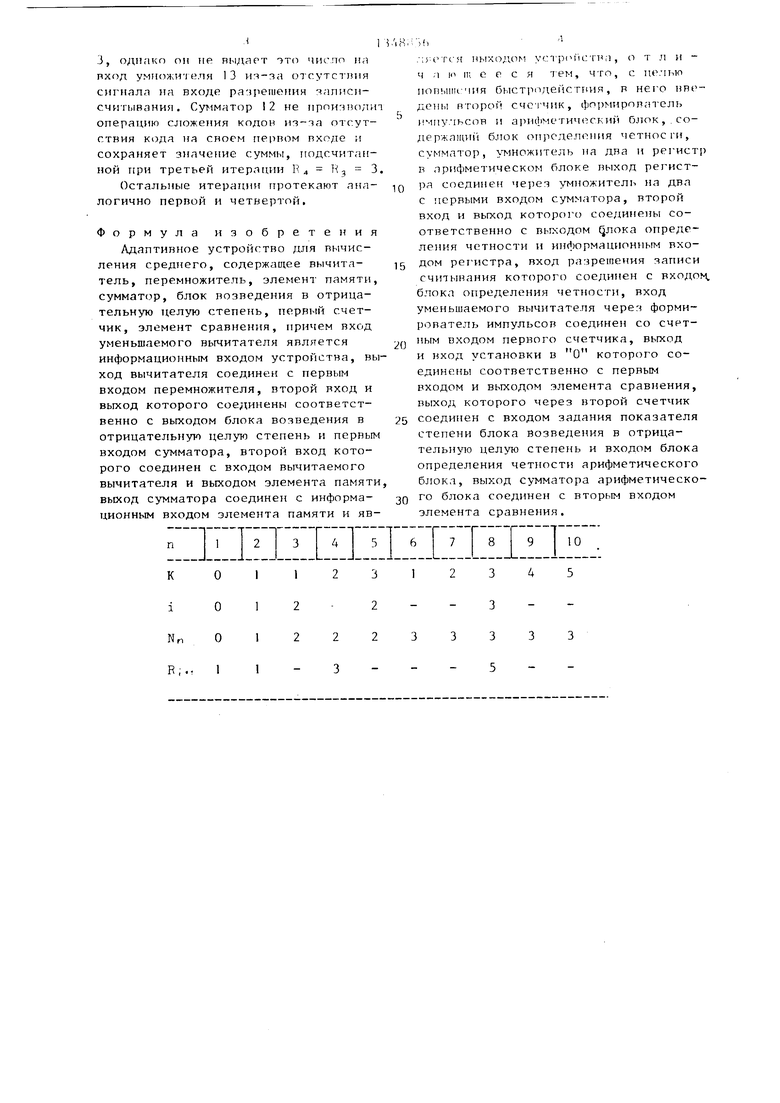

На фиг.1 )a;,ena структурная схема устройства; на ()иг .2 - структурная схема apиф ierичecкoгo блока.

Устройство соде1)хит В1.1чит,тгедь 1 , перемножитель 2, сумматор 3, г лемент 4 памнти, блок 5 втведе.ния в от})Ииа- Te.nbFiypi степень, счетчик 6, элемент 7 ср.шнепия, счетчик 8, фор- миронатс Л -. Ч nMiiy. iiicnB н а1)ифметичес- кяй Глок 10.

Лрифмеп ический блок (.одержит блок 11 определения чегности, cyf-iMiiTop 12 умножитель 13 на дна, регистр 14.

Устройство работает следующим образом.

В исходном состоянии в счетчиках 6 и 8 злписань Мг1К ;имальн,1е для их разрядной сетки числа, в -итементе 4 памяти и регистре 14 записаны нули, а на выходе блсжа 10 П1)исутствует неличина, раьр1ая нулю.

После подачи первого ; амера Х на В1 1ходе вычита 1 еля 1 появляется величина X., кого11ая в фо)мирователе 9 гтреобра в 1, сбрасываю1цую ft в О (У.) . Элемент 7 сравнения сраинивает величины, присутствующие на его вхс дах (К( и }..,. г), и н .|д/1ст 1:мг1ульс совпадери-1я а вх1 1Д СЧ1 тчика сЯ, которьи сбрасглва- ется в ( лсгояние 1, .. 1)Лок 10 ni-i4iu . u;e i-.oin Meci но та -1; г,:ц --i

нулевом иич ернгчле ностоннстнл ( ;-. i, а блок 5 вычисляет неличину 2 2 1. Пе1К мнолитель 2 (который реализует онерапию сдвига ио не,чичи1ге 2 ) с приходом на его вто,-,- N,

ро)1 вход значения 2 1 передает величину Х| без сдвига на первый вход сумматора 3, г де склядынается с нулем, лаиисан)гым в элементе 4 памяти. После этого на выходе сумматора 3 появляется значение X,, которое записывается в элемент 4 памяти. На этом зака}1чивается nejiBaH итерация.

При BTopoii итерации блок 10 производит Н1,(числение величины R - 1 по формуле (2). Па выходе сумматора 3 п()является среднее двух замеров

0,5(Х , - X,} - 0,5(Х,+Х ,р,

При третьей итерации п блоке 10 В1пчисляется ве:гичина К 3. Поэтому на В1 1ходе устроГ1ства будзт величина, онр(;;деляемая выражением

25

Л

81

i

0

5

0

5

0

5

Остальные итерации протекают аналогично оиисапиым.

Плок 10 работает следующим образом.

В исходном состоянии регистр 14 умножитель 13 и сумматор 12 и меют на выходе нули, а блок 11 определения четности имеет любое исходное (-1 или + 1 ) .

Блок 11 определения четности, реализующий операцию (-l), и регистр 14, являющийся элементом памяти, изменяет свое состояние при изменении кода числа N на вьгходе счетчика 8 (по фронту кода).

При первой итерации счетчик 8 сбрасывается в О (Г, о). В умножителе 13, производящем операцию умножения на два, нулевое значение результата поступает на вход сумматора 12. В это время блок 1I выдает значение w (-1) 1 на другой вход сумматора . 12, поэтому на выходе цоследнего будет зцачение К I, которое записывается в-регистр 14 и поступает на выход блока 10.

Вторая и третья итерации протекают аналогично первой.

При четвертой итерации счетчик 8 не изменяет кода числа N з поэтому блок 11 имеет предыдущее значение. В регистре 14 записано число

3, однако он не выдает это число на пход умножителя 13 ич-за отсутстпия сигналп на входе разрешения записи- считывания. Сумматор 12 не нронзно/ти онерацию сложения кодов из-за отсутствия кода на своем первом пходе и сохраняет значение суммы, подсчитанной при третьей итерации R R., 3 Остальные итерации протекают аналогично первой и четвертой,

Формула изобретения

Адаптивное устройство для вычисления среднего, содержащее вычита- тель, перемножитель, элемент памяти, сумматор, блок возведения в отрицательную целую степень, первый счетчик, элемент сравнения, причем вход уменьшаемого вьгчитателя является информационным входом устройства, выход вычитателя соединен с первым входом перемножителя, второй вход и выход которого соединены соответственно с выходом блока возведения в отрицательную целую степень и первым входом сумматора, второй вход которого соединен с входом вычитаемого вычитателя и выходом элемента памяти выход сумматора соединен с информационным входом элемента памяти и явi,S.

. пыходом устр1м и:тра, о т л и - ч а III е р с я тем, что, с пелыо попыпн чия быстридейстпия, в него вво- доны второй счс 1-чик, фо1)мчрователь импу.чьсов и а)1и11метический блок,, содержащий блок опроделпния четности, сумматор, умножитель на два и регистр в арифметическом блоке выход регистра соединен через умножитель на два с первыми входом сумматора, второй вход и выход которого соединены соответственно с вьгходом лока опреде- ления четности и информационным входом регистра, вход разрешения записи считывания которого соединен с входом, блока определения четности, вход уменьшаемого вычитателя через формирователь импульсов соединен со СЧРТ- ньгм входом первого счетчика, выход

nil

единены соответственно с первым входом и выходом элемента сравнения, выход которого через второй счетчик

соединен с входом задания показателя степени блока возведения в отрицательную целую степень и входом блока определения чет}1ости арифметического блока, выход сумматора арифметического блока соединен с вторым входом элемента сравнения.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для воспроизведения функций @ и @ | 1989 |

|

SU1658151A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU678488A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

Изобретение относится к специа- лизировлнньсм цифровым вычислительным устройствам и может быть использова1го для определения статистических характеристик сл чайных процессов. Цель изобретения - нов1 пиение быстродействия устройства. Устройство содержит вычитатель 1, перемножитель 2, элемент 4 памяти, сумматор 3, блок 5 возведения в отрицательную целую степень, формирователь 9 импульсов, счетчики 6,8,элемент 7 сравнения,арифметический блок 1 0. Устройс1 во позво- пяет у ростить вычисление усредняющего коэффициента в адаптивном алгоритме, которое осуществляет арифметический Г1лок, 2 ил„ , 1 табл. оо 4;: ОО 00 сл 05

| Дифференциальная схема управления ферридом | 1972 |

|

SU466572A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивное устройство для вычисления среднего | 1978 |

|

SU769551A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-03-04—Подача