, 1 .,.

Изобретение относится к области цифровой вычислительной техники и может найти применение дл,я аппаратной реализации операций вычисления обратного кругового косинуса или синуса и возведения в квадрат.

Указанные функции в настоящее время вычисляются в ЭВМ общего назначения по стандартным подпрограммам, что требует сложных арифметических устройств и больших затрат машинного времени.

Известен способ вычисления обратного косинуса посредством отыскания последовательных значений величин косинусов двойных углов в последовательном итерационном цикле Ц.Этот способ Удобен только для программно реализации,.

Известно арифметическое устройство для вычисления обратного синуса отнсяиения двух аргументов, содержащее сумматоры, вычитатели, сдвигающие регистры, коммутирующие блоки (для сдвига кодов) и блок управления 2. Это устройство обладает ограниченными функциональными возможностями .

Известны устройства для. вычисления обратных тригонометрических и

гиперболических функций, содержащие регистры, сумматоры-вычитатели и блоки управления 3. Эти устройства сложны и облгщают ограниченными функциональными возможностями.

Из известных устройств наиболее 5; изким по технической сущности и достигаемому результату к изобретеQ нйю является устройство для вычисления обратного кругового синуса. Это устройство содержит 2 сумматоравычитателя, блок памяти и блок управления, первый выход которого соес динен СО входом блока памяти, выход которого соединен с первым входом первого сумматора-вычитателя 4.

Это устройство не предназначено для вычисления обратного тригонометQ рического косинуса и возведения аргумента в квадрат..

Целью изобретения является расширение функциональных возможностей устройства, а именно вычисление об5 ратного тригонометрического косинуса или синуса и одновременно возведение в квадрат-аргумент а в единой структуре.

Поставленная цель достигается

Q .тем, что предложенное устройство содержит ло ический блок и блок

воэведения в квадрат, выход которого соединен с первым входом второго сумматора-вычитателя,. выход которого соединен с первым входом блока возведения в квадрат и входом логического блока, выходы которогосоединены со вторыми входами первого и второго сумматоров-вычитателей соответственно, второй, третий и четвертый выходы блока управления соответственно соединены с третьими входами.,-, первого и второго сумматоров-вычитателей и вторым входом блока возведения в квадрат. ;, .: . ..;

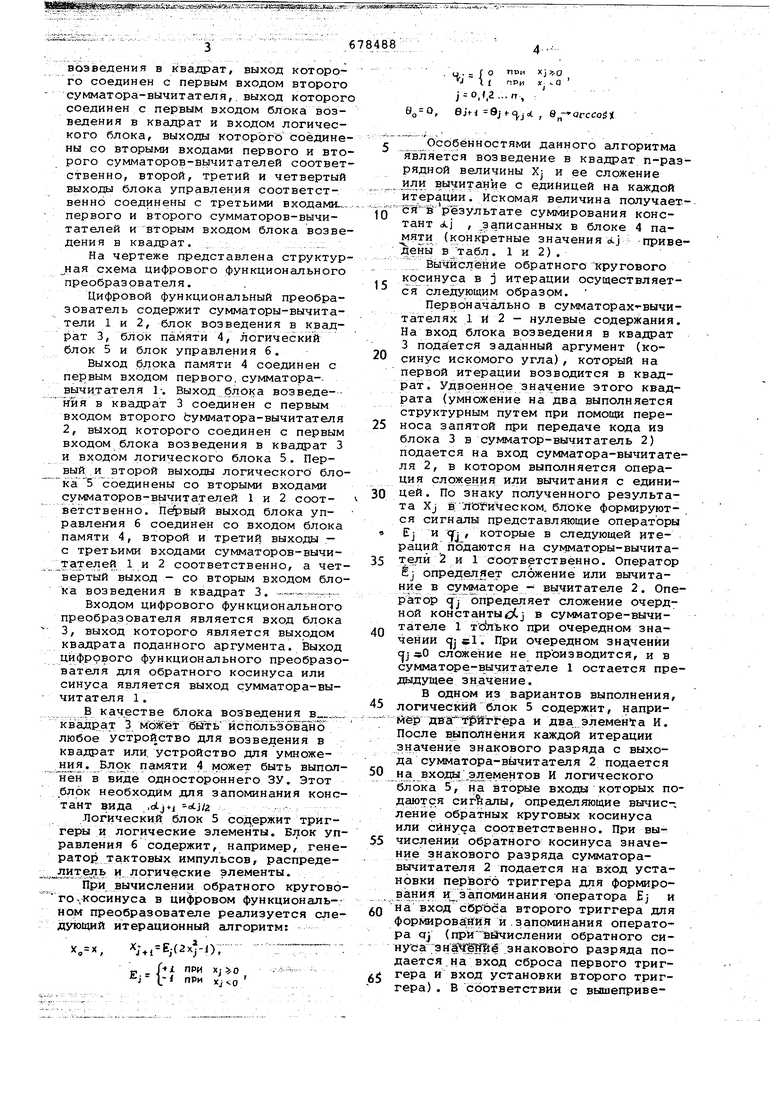

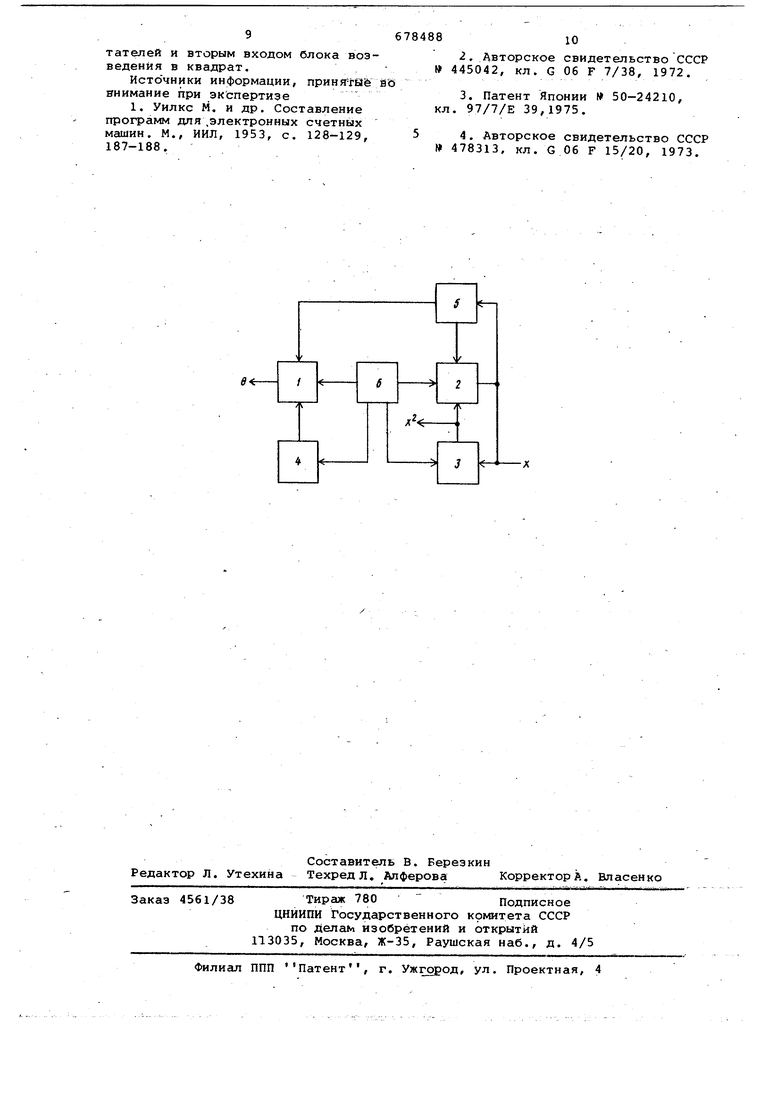

На чертеже представлена структур ная схема цифрового функционального преобразователя.

Цифровой функциональный преобразователь содержит сумматоры-вычитатели 1 и 2, блок возведения в квадрат 3, блок памяти 4, логический блок 5 и блок управления 6.

Выход блока памяти 4 соединен с первым входом первого, сумматоравычи тателя 1-. Выход блока воз веде- мйя в квадрат 3 соединен с первым входом второго Ьумматора-вычитателя

2,выход которого соединен с первым входом блока возведения в квадрат 3 и входом логического блока 5. Первый и второй выходы логического 5 соединены со вторыми входами сумматоров-вычитателей 1 и 2 соответственно. Пб4)вый выход блока управлентия 6 соединен со входом блока памяти 4, второй и третий выходы - с третьими входами сумматоров-вычи тателей 1 и 2 соответственно, а четвертый выход - со вторым входом блока возведения и квадрат 3. ,-,™.-.,«--;;

Входом цифрового функционального преобразователя является вход блока

3,выход которого является выходом квадрата поданного аргумента. :Выход цйфррвого функционального преобразователя для обратного косинуса или синуса является выход сумматора-вычитателя 1.

В качестве блока возведения в „...„ квадрат 3 мояГёт бить использбвано любое устройство для возведения в квадрат или. устройство для умножения. Блдк памяти 4 может быть выполнен в виде одностороннего ЗУ. Этот блок необходим для запоминания констант вида .oLj+j - ijlz-:

Логический блок 5 содержит триггеры и логические элементы. Блок управления б содержит, например, генератор тактовых импульсов, распреде дитель и. логические элементы.

При вычислении обратного кругового ..косинуса в цифровом функционапь-/ ном преобразователе реализуется следующий итерационный алгоритм:

х,х, %rE(2xj-o;

f-H ПРИ

г Ii ПРИ

678488

ПРИ

ПРИ

j o,,a...-,,

j o,,a...n.

Sjtl , в -огссой)

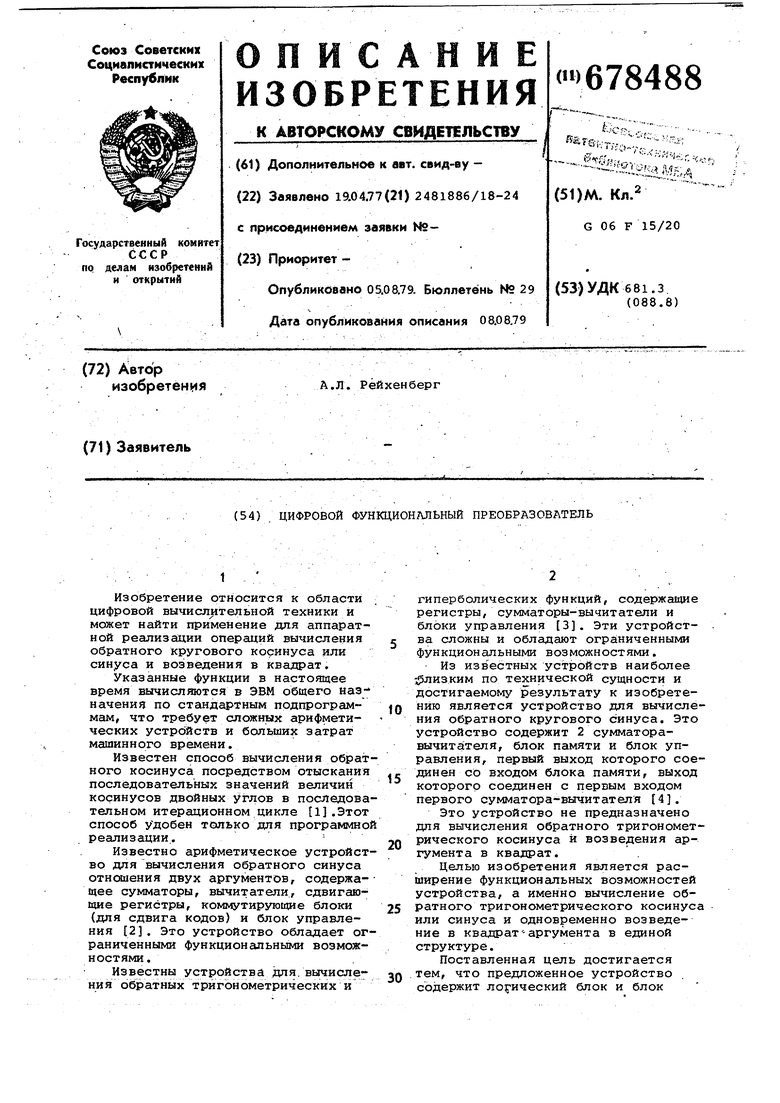

Особенностями данного алгоритма является возведение в квадрат п-разрядной величины Xj и ее сложение или вычитание с единицей на каждой итерации. Искомая величина получает51 & результате суммирования констант ,.j , записанных в блоке 4 (конкретные значения oLj приварены в табл. 1 и 2) .

Вычисление обратного кругового крсинуса в j итерации осуществляется следующим образом.

Первоначально в сумматорах-вычитателях 1 ri 2 - нулевые содержания. На вход блока возведения в квадрат 3 подерется заданный аргумент (косинус искомого угла), который на первой итерации возводится в квадрат. Удвоенное значение этого квадрата (умножение на два выполняется структурным путем при помощи переноса запятой при передаче кода из блока 3 в сумматор-вычитатель 2) подается на вход сумматора-вычитателя 2, в котором выполняется операция сложения или вычитания с единицей. По знаку полученного результата Xj в; ЛОТическом.. блоке формируются сигналы представляющие операторы EJ и «fj которые в следующей итераций подаются на сумматоры-вычитателй i2 и 1 соответственно. Оператор EJ определяет сложение или вычитание в сум1маторе - вычитателе 2. Оперйтор определяет сложение очердной константыctj в сумматоре-вычитателе 1 при очередном значении О «1. При очередном значении CTj jsO сложение не производится, и в сумматоре-вычитателе 1 остается предыдущее значение.

В одном из вариантов выполнения, логический блок 5 содержит, наприйёр Д6а ;т1 йтгера и два,, элемента И. После выполнения каждой итерации значение знакового разряда с выхода сумматора-вычитателя 2 подается на входа ,элементов И логического блока 5, на вторые входы которых подаютс.я сигналы, определяющие вычис-, ление обратных круговых косинуса или синуса соответственно. При вычислении обратного косинуса значение знакового разряда сумматоравычитателя 2 подается на вход установки первого триггера для формирования и запоминания -оператора Ej и На вход сбрбса второго триггера для формирования и.запоминания оператора q| (прй вйчислении обратного синуса зна ЕШйё знакового разряда подается на вход сброса первого триггера и вход установки второго триггера) . В соответствии с вышеприведенными логическими соотношенйяМи формируются значения операторов Е; и gj , причем единичные значения представляются наличием уровня напряжения, а нулевые и минус единичные значения - нулевым уровнем с выходов триггеров, которые являются выходами логического блока 5. Отрицательное значение знакового разряда сумматора-вычитателя 2 представляется логической единицей (т.е. в этом случае знаковый разряд является значащим) .

В следующей итерации полученное в сумматоре-вычитателе 2 значение Xj подается на вход блока возведени я в квадрат 3. Удвоенный квадрат этого значения подается на первый вход сумматора-вычитателя 2 и т.д.

Последовательность и порядок выполнения указанных операций определяются серией тактовых импульсов, подаваемых с выходов блока управления 6 .

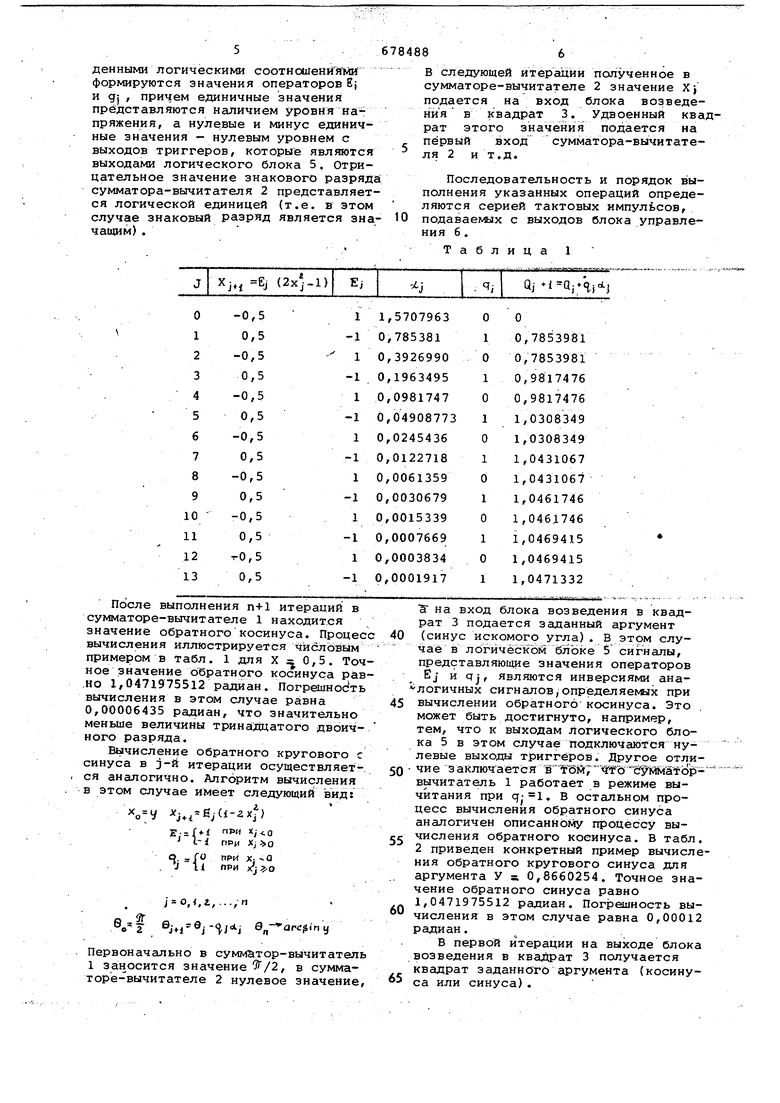

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления обратного кругового синуса | 1973 |

|

SU478313A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU607223A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU684551A1 |

После выполнения п+1 итераций в сумматоре-вычитателе 1 находится значение обратного косинуса. Процесс вычисления иллюстрируется числойым примером в табл. 1 для X 0,5. Точное значение обратного косинуса рав.но 1,0471975512 радиан. norpemHodTb вычисления в этом случае равна 0,00006435 радиан, что значительно меньше величины тринадцатого двоичного разряда.

Вычисление обратного кругового с синуса в j-й итерации осуществляет-. ся аналогично. Алгоритм вычисления в этом случае имеет следующий вид:

с, У (l-2xf}

Ч;-

ПРИ Х: -О

ПРИ xTj о

; о,,г,...,(1

s.-f Sj. 9«

у

Первоначально в сумматор-вычитатель 1 заносится значение5/2, в сумматоре-вычитателе 2 нулевое значение.

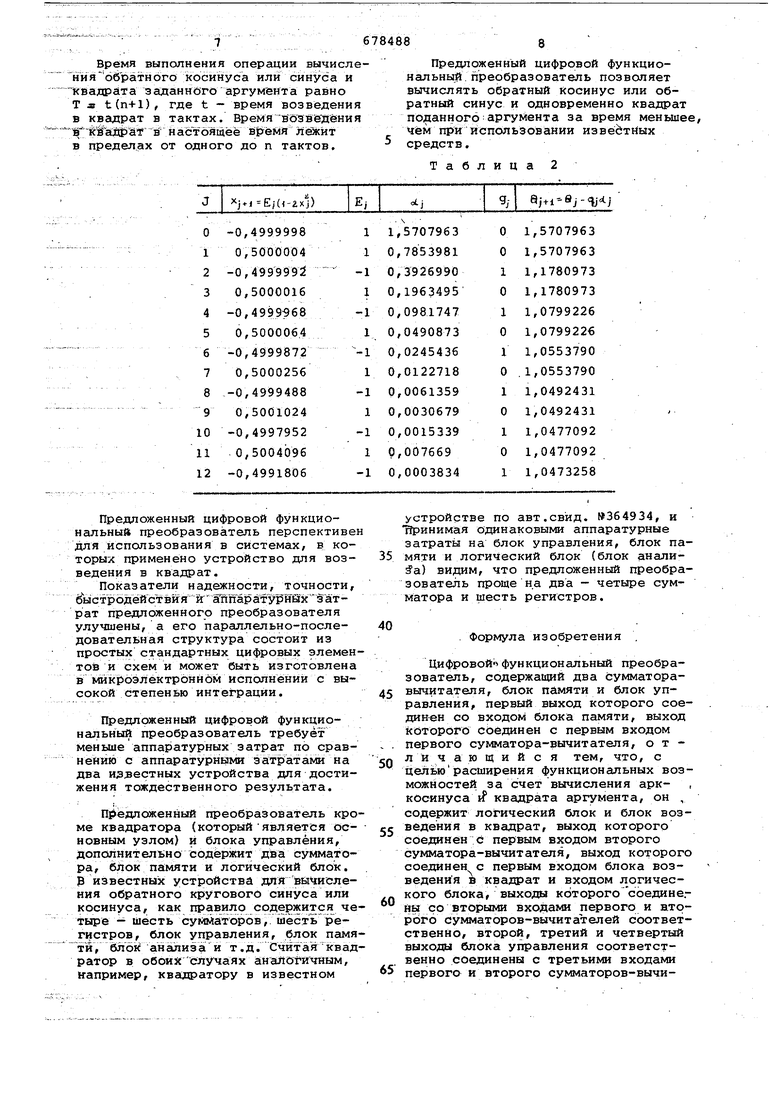

S на вход блока возведения в квадрат 3 подается заданный аргумент (синус искомого угла). В этом случае в логической блоке 5 сигналы, представляющие значения операторов EJ и qj, являются инверсиями аналогичных сигналов,определяе1 ых при вычислении обратного косинуса. Это может быть достигнуто, например, тем, что к выходам Логического блока 5 в этом случае подключаются нулевые выходы триггеров. Другое отли0 чие 3 аключается 1 в сГ;р Ш1а : рвычитатель 1 работает в режиме вычитания при . В остальном процесс вычисления обратного синуса аналогичен описанному процессу вычисления обратного косинуса. В табл. 2 приведен конкретный пример вычисления обратного кругового синуса для аргумента У . 0,8660254. Точное значение обратного синуса равно 1,0471975512 радиан. Погрешность вы0числения в этом случае равна 0,00012 радиан.

В первой итерации на выходе блока возведения в квадрат 3 получается квадрат заданного аргумента (косинуса или синуса).

Время выполнения операции вычисле нй я обратного косинуса или синуса и квадрага заданнбто аргумента равно Т а t(n4-l), где t - время возведения в квадрат в тактах. Времявбзвёйёния B WгШРй в наст оящёё лежит в пределах от одного до п тактов. Предложенный цифровой функциональны преобразователь перспективе для использования в системах, в которых применено устройство для возведения в квадрат. Показатели надежности, точности, &стр6дёйЪтвйя иг SnMpaWPffSx 3 рат предложенного преобразователя улучшены, а его параллельно-последовательная структура состоит из простых стандартных цифровых элемен тов и схем и может быть изготовлена в мйкрбэлектрЬнНбм исполнений с высокой степенью интеграции. Предложенный цифровой функциональный преобразователь требует меньше аппаратурных затрат по сравнению с аппаратурными затратами на два известных устройства для достижения тождественного результата. Предложенный преобразователь кро ме квадратора (которыйявляется основным узлом) и блока управления, дополнительно содержит два сумматора, блок памяти и логический блок. Э известных устройства для вычисления обратного кругового синуса или косинуса, как правило содержится че тыре - шесть сумматоров,, шесть регистров, блок управления, блок памя тй, (5л6й анализа и т .д. Считая квад ратор в обоих случаях аналОТйчным, например, квадратору в известном

Предложенный цифровой функциональный, преобразователь позволяет вычислять обратный косинус или обратный синус и одновременно квадрат по,цанного: аргумент а за время меньшее, чём при йспсэльзовании извёЬтНых средств.

Таблица 2 устройстве по авт.свид. 364934, и йринимая одинаковыми аппаратурные затраты на блок управления, блок памяти и логический блок (блок аналиSa) видим, что предложенный преобразователь проще на два - четыре сумматора и шесть регистров. . Формула изобретения . Цифровой функциональный преобразователь, содержащий два сумматоравычитателя, блок памяти и блок управления, первый выход которого соединен со входом блока памяти, выход которого соединен с первым входом первого сумматора-вычитателя, отличающийся тем, что, с цельюрасширения функциональных возможностей за счет вычисления арк- , косинуса if квадрата аргумента, он , содержит логический блок и блок возведения в квадрат, выход которого соединен с первым входом второго сумматора-вычитателя, выход которого соединен с первым входом блока возведения в квадрат и входом логического блока, выходы которого соедине,ны со вторыми входами первого и нтррого сумматоров-вычитателей соответственно, второй, третий и четвертый выходы блока управления соответственно соединены с третьими входами первого и второго сумматоров-вычитателей и вторым входом блока возведения в квадрат.

Источники информации, приня Шё йб внимание при экспертизе

Авторы

Даты

1979-08-05—Публикация

1977-04-19—Подача