Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных вычислительных системах для.обслуживания запросов на прерывание Q-шины и шины VME.

Цедью изобретения является р.асшире- ние области применения за.счёт совместной обработки запросов различных магистралей, / -.О. - - . .

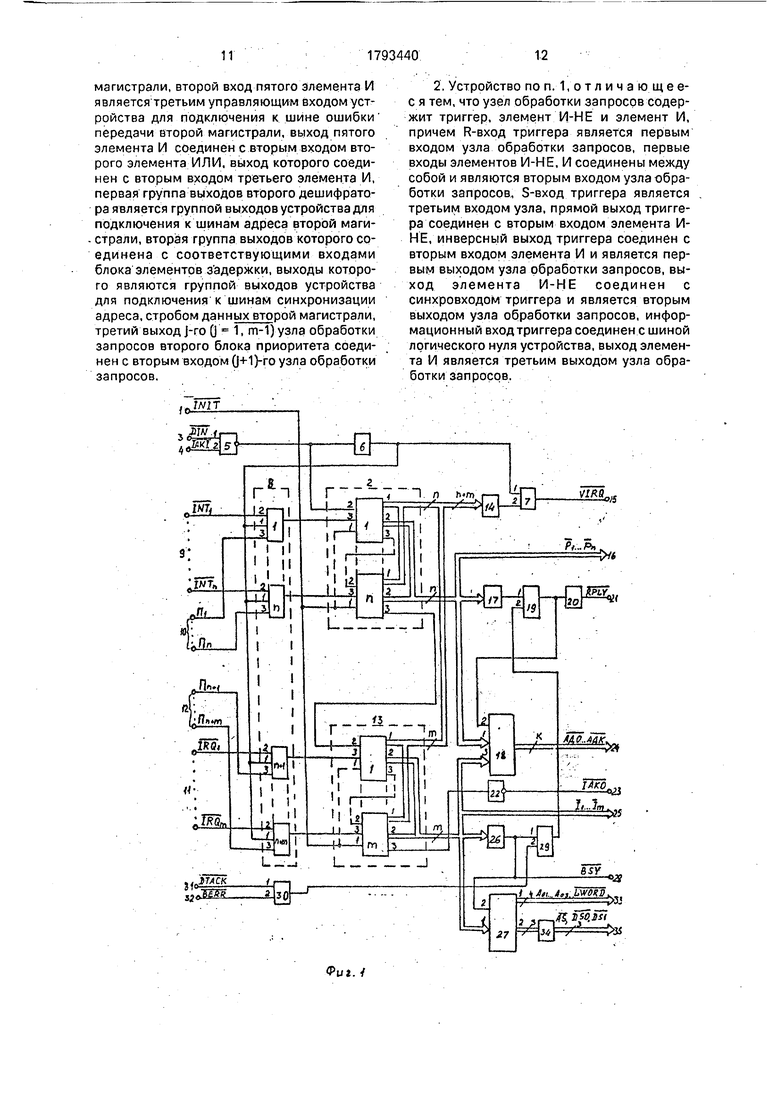

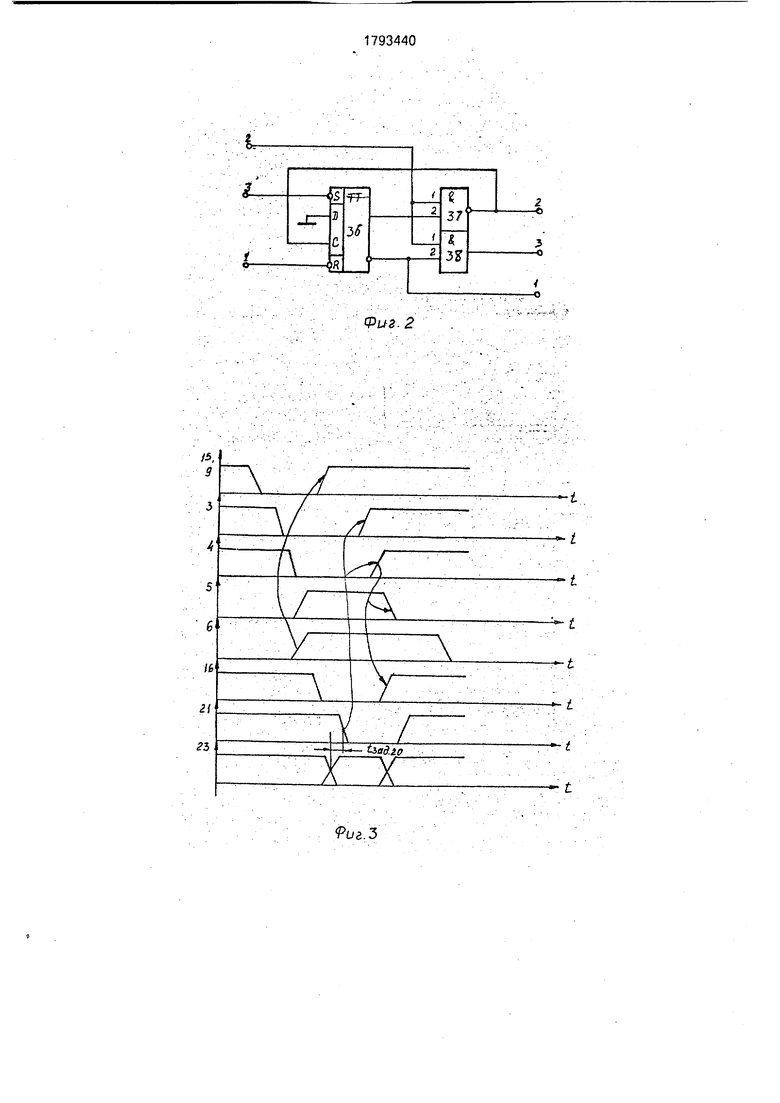

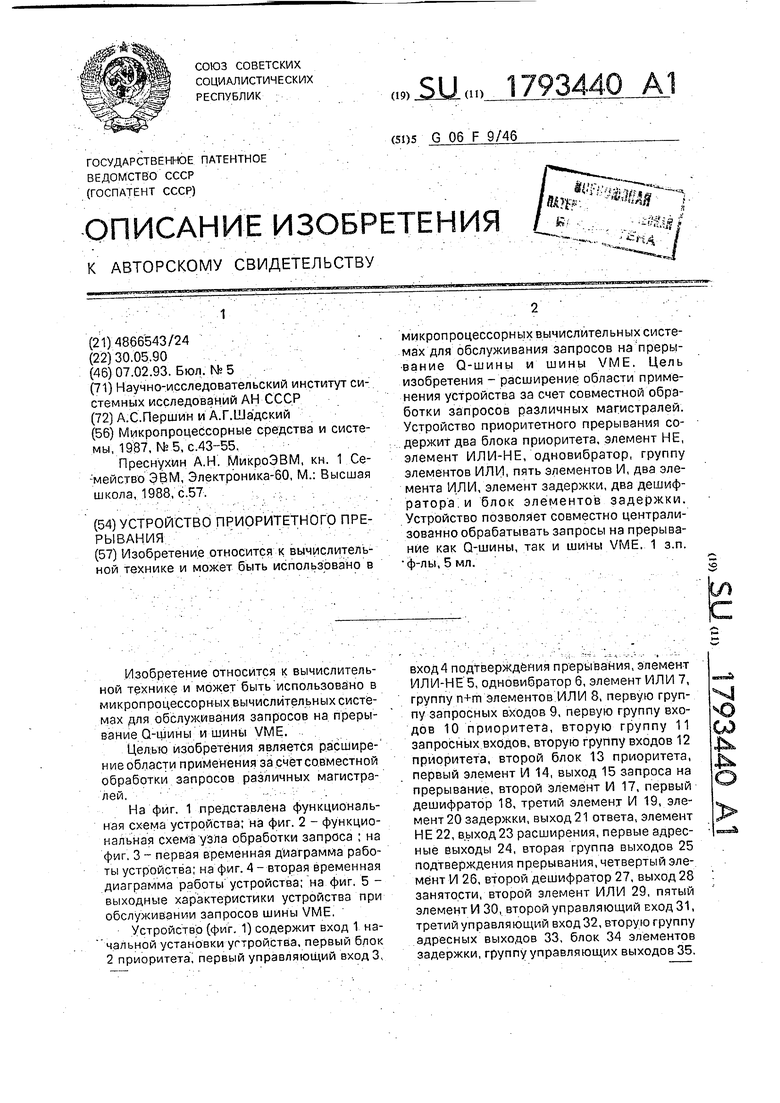

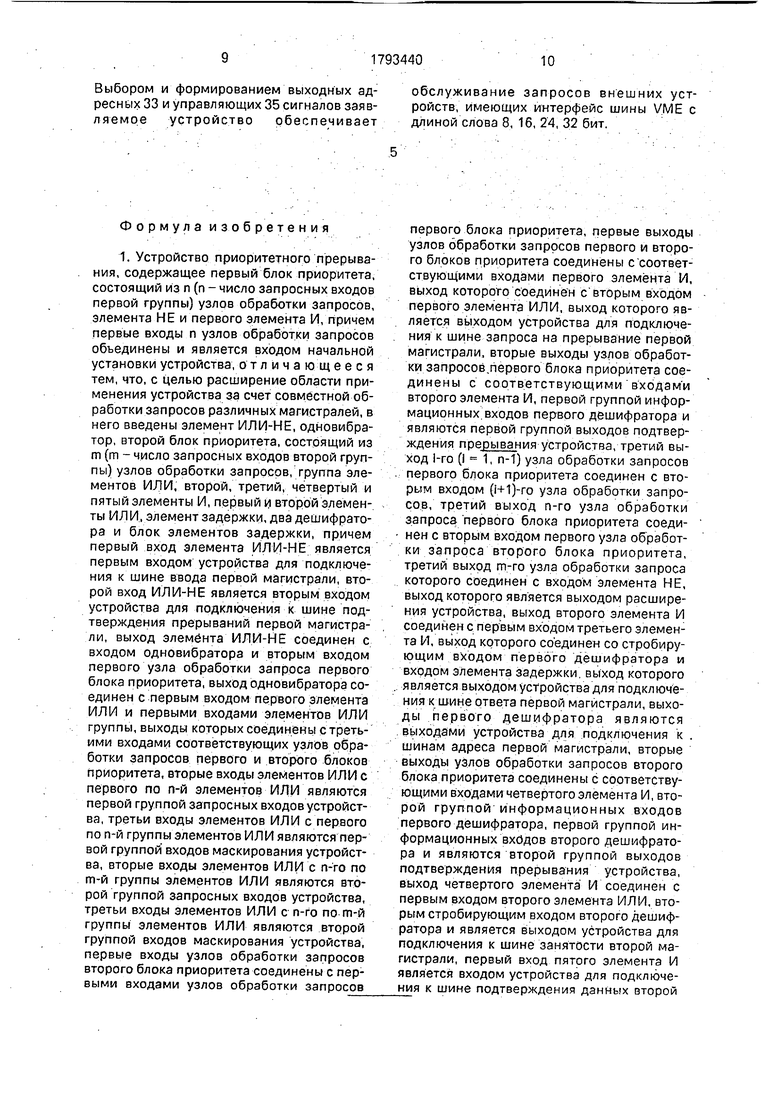

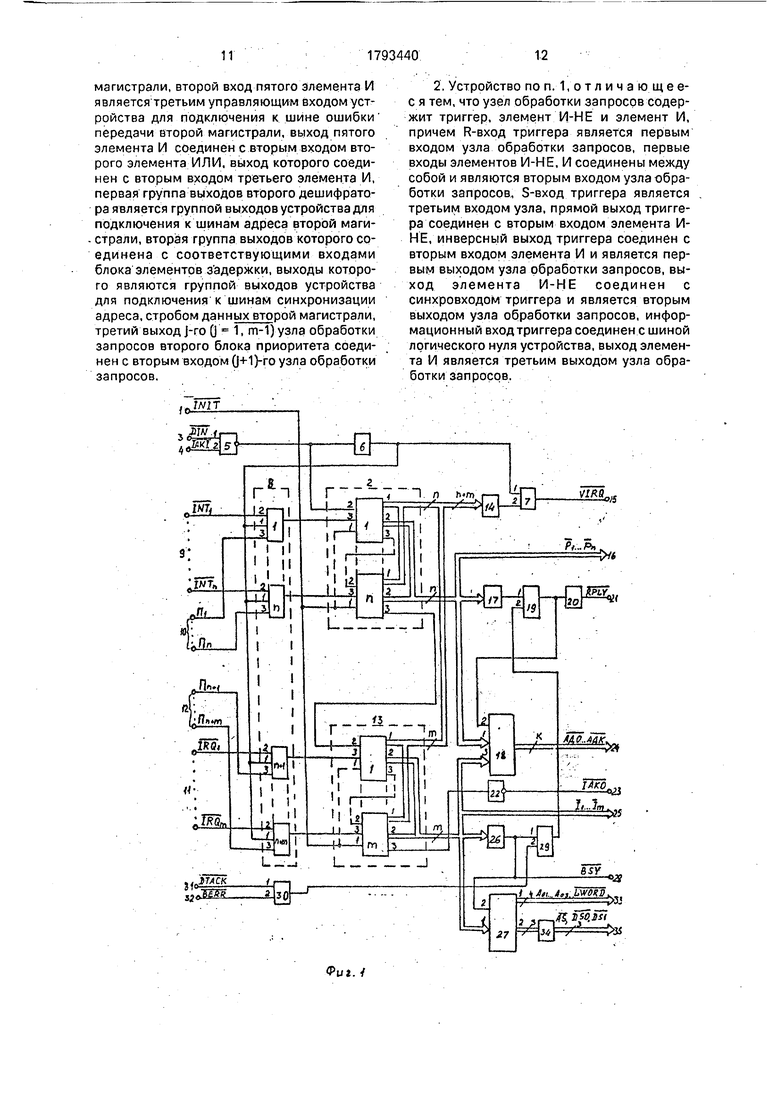

На фиг, 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема узла обработки запроса ; на фиг. 3 - первая временная диаграмма работы устройства; на фиг. 4 - вторая временная диаграмма работы устройства; на фиг. 5 - выходные характеристики устройства при обслуживании запросов шины УМЕ,

Устройство (фиг. 1) содержит вход 1 на чальной установки устройства, первый блок

2 приоритета первый управляющий вход 3,

вход4 подтверждения прерывания, элемент ИЛИ-НЕ 5, одновибратор 6, элемент ИЛИ 7, группу n+m элементов ИЛИ 8, первую группу запросных входов 9, первую группу входов 10 приоритета, вторую группу 11 запросных входов, вторую группу входов 12 приоритета, второй блок 13 приоритета, первый элемент И 14, выход 15 запроса на прерывание, второй элемент И 17, первый дешифратор 18, третий элемент И 19, элемент 20 задержки, выход 21 ответа, элемент НЕ 22, выход 23 расширения, первые адресные выходы 24, вторая группа выходов 25 подтверждения прерывания, четвертый элемент И 26, второй дешифратор 27, выход 28 занятости, второй элемент ИЛИ 29, пятый элемент И 30, второй управляющий вход 31, третий управляющий вход 32, вторую группу адресных выходов 33, блок 34 элементов задержки, группу управляющих выходов 35.

Каждый из n+m узлов обработки запросов первого 2 и второго i3 блоков приоритета содержит триггер р-типа 36, элемент И-НЕ

37,изв. ;;;.. ;--,;v:,./. .:/ ..;..- :-.

Заявленное устройство позволяет построить (п+т уровневую векторную систему прерываний с врзмржностью маскирования и реализовано: ;в двух вари- антахгдля п 1, m 7, kV8, (Ыакс 1:б), Для п 3, m 7, k - В, формируя вреьмиразряд- ный адрес.вектора прерыв йя проце ССОру, работающ ему по Q шине (микроЭВМ Элек- троника-бО , микропроцессоры Т806ВМ2, 1801ВМ2,1801ЕМЗ). Вкачестве элементной базҐ иепользойзнь микросхемы 533, 556, 559 серий. Могут быть использованы микросхемы К155, К555 серий, ; - л

Одновибратор 6 реализованна микро- схеме 533;АГ3 5АГЗ) по схеме; приведен ной в справочнике Шило В.Л. Популярные цифровые микросхемы, 1988, с.189, табл.. 1.115 и с. 190, рис.1.138г, для запуска по положительному перепаду (из логического О в логическую 1) входного сигнала. Учитывая, что время цикла записи-чтения, приема адреса вектора прерывания в .указанных выше микроЭВМ составляет примерно 1,5,..2,5 мкс, длительность импульса высокого уровня на выходе одновиб- ратора 6 выбирается равной 3...7 мкс. Для построения первого и второго дешифраторов 18 и 27 использованы постоянные запоминающие устройства (ПЗУ) 556 РТ5 емкостью 4096 бит с организацией 512 8 и открытым коллектором. Для реализации устройства при п 3, т 7 используется 556 РТ6 с организацией 2К 8 и открытым коллектором. Первый, вторые и третьи управляющие входы первого дешифратора 18 и-. первыми и вторъгеуправляющйе входы второго дешифратора 27 подключены к адресным входам соответственно первого и второго ПЗУ. Неиспользованные адресные входы второго дешифратора 27 соединены с нулевой шиной источника питания. Выходами дешифраторов 18, 27 являются выходы информационных разрядов ПЗУ, причём каждый из выходов ПЗУ соединен через резистор 1...3 кОм с напряжением питания +5 В. Четыре управляющих входа первого и второго ПЗУ соединены с шинами питания устройства со глаено режиму считывания. Восьмиразрядный адрес вектора прерывания на выходе первого дешифратора 18 и семь управляющих сйгналов на выходе второго дешифратора 27 программируются пользователем в зависимости от кодов сиг- налов на первых и Третьих входах дешифратора 18 и первых входах дешифратора 27. При этом на вторых: управляющих входах

данных дешифраторов сигнал логического О. При наличии на вторых управляющих входах первого 18 и второго 27 дешифраторов сигналов логической 1 на выходах

данных дешифраторов (ПЗУ) также сигна- . лы логической 1 (высокого уровня) при любой комбинации входных сигналов на входах 1,3..

Элемент 20 задержки реализован набуферном элементе без инверсии, с открытым коллектором микросхемы К155 Л Н4. На входе буферного элемента установлена интегрирующая цепочка, состоящая из резистора и конденсатора, причем входом элемента 20

5 задержки является первый вывод резистора, второй вывод которого соединен с входом буферного элемента и первым выводом Конденсатора, второй вывод которого соединен с нулевой шиной источника питания.

0 Выходом элемента задержки служит выход буферного элемента, .соединенный с первым выводом резистора порядка 1 кОм, второй вывод которого соединен с напряжением источника питания +5 В. Вы5 бором номинала резистора и,конденсатора интегрирующей цепочки осуществляется выбор времени задержки, равной Od ..,0,2 мкс, . . / ,--

Блок 34 элементов задержки состоит из

0 трех элементов задержки для сигналов 35, Каждый из элементов задержки блока 34 реализован анал огично элементу 20 задер- жки. Время задержки каждого из элементов задержки блока 34 составляет 35...60 не.

5 При необходимости (большой загруженности Q-шины И шины VME выходные сигналы 15, 16, 23, 24, 25, 28, 33, 35 также следует подключить к магистралям через буферные элементы микросхемы К155 Л Н4.

0 Следует отметить, что работой заявляемого устройства управляет микроЭВМ, имеющая системный канал (магистральный интерфейс) Q-шины, являющийся упрощенным вариантом интерфейса Общая шина

5 (ГОСТ 26765,51-8). Заявляемое устройство обеспечивает также обработку запросов на прерывание программы устройств ввода- вывода, имеющих системный канал шины VME, являющийся в настоящее время един0 ственным международным стандартом для 8, 16, 24, 32 разрядных микропроцессорных систем (4, 5).:

ПРИ.ЭТОМ сигналы 1,3,4,9, 15,21,23,24 являются магистральными сигналами Q-ши5 ны,Сигналы 11, 28, 31, 32, 33, 35 являются магистральными сигналами шины VME. Входные сигналы первой 10 и второй 12 трупп приоритета могут задаваться как с помощью дополнительного регистра приоритета, управляемого магистральными

сигналами, так и с помощью перемычек (наличие логической 1 блокирует обработку соответствующего запроса на прерывание; наличие логического О разрешает обслуживание запроса).

Устройство работает следующим образом (фиг. 1).

После подачи напряжения питания процессор формирует сигнал начальной установки 1 низкого уровня, который устанавливает в исходное (начальное) состояние n+m узлов обработки запросов первого 2 и второго 13 блоков приоритета, поступая на третьи входы каждого узла и соответственно на R-входы триггеров D-ти- па 36 (фиг. 2). При этом на первых и вторых выходах каждого из узлов обработки запросов формируются сигналы высокого уровня, на третьих выходах - сйгналы-низкогр уровня. Одновременно устанавливаются в ис- ходное состояние источники, прерывания и на входах 3, 4, 9, 11, 31, 32 заявляемого устройства формируются также сигналы высокого уровня, Каждое устройство (источ- ник), требующее прерывание и формирующее запрос на прерывание, име- ет подпрограмму обслуживания, хранящуюся в ПЗУ микроЭВМ, вход в которую осуществляется автоматически с помощью вектора прерывания. В случаен 2, m 2, К 8 заявляемое устройство обслуживает два запроса на прерывание. 9 Q-шины 1NTi, 1NT2 с приоритетами 10 П i, Tig и два запроса на прерывание 11 шины VME, 1 RQi, 1 R02 с приоритетами 12 Пз, П4. Маскирование (запрет обслуживания) запроса осуществляется подачей логической 1 на входы приоритетов 10, 12, разрешение обслуживания запросов - подачей логического О. Процесс обслуживания прерывания начинается по окончании сигнала 1 (появление потенциала высокого уровня) в момент появления запроса на прерывание одной из групп, заз просов 9, 11. При появлении запроса 1NT2 первой группы запросов 9 и отсутствии ма- скирования по данному запросу на выходе второй схемы ИЛИ группы элементов ИЛИ 8 появляется сигнал низкого уровня, поступающий на третий вход второго узла обработки запроса первого блока 2 приоритета. Данный сигнал устанавливает триггер D-ти- па 36 в единичное состояние и на инверсном выходе триггера D-типа 36 и соответственно первом выходе второго узла обработки запроса первого блока 2 приори- тета появляется сигнал низкого уровня, поступающий на второй вход элемента И 14. Сигнал низкого уровня на выходе элемента И 14, поступая на второй вход элемента ИЛИ 7, вызывает появление выходного сиг-

нала запроса 15 (фиг. 3), поступающего на вход запроса на прерывание процессора. Процессор удовлетворяет требование запроса на прерывание, вырабатывая сигналы 3, 4 низкого уровня, что в св ою очередь, вызывает появление на выходе элемента ИЛИ-НЕ 5 сигнала высокого уровня, запуска ющего однбвйбратор 6. Сигнал с выхода одновибратора 6, поступая н.а первый вход элемента ИЛИ 7. снимает требование запроса на прерывание 15 и блокирует поступление запросов 9, 11 на третьи входы узлов обработки запросов на прерывание первого 2 и второго 13 блоков приоритета. Сигнал подтверждения прерывания с выхода элемента ИЛИ-НЕ 5 поступает также на второй вход первого узла обработки запроса первого блока 2 приоритета и соответственно на первые .входы элементов И-НЕ 37, И 38, с помощью которых анализируется состояние триггера D-типа 36 данного узла. Поскольку триггер D-типа 36 первого узла обработки запроса первого блока 2 приоритета установлен в исходное состояние, то сигнал под- тверждения прерывания поступает на выход элемента И 38 и соответственно на третий выход данного узла. Далее сигнал подтверждения прерывания поступает на второй вход второго узла обработки запроса первого блока 2 приоритета. Так как триггер D-типа 36 данного узла установлен в единичное состояние, то дальнейшее прохождение.сигнала подтверждения прерывания блокируется и на выходе элемента И-НЕ 37 и соответственно втором выходе второго узла обработки запроса первого блока 2 приоритета формируется выходной сигнал Р2 первой группы подтверждения прерывания 16 в виде потенциала низкого уровня. По данному сигналу источник прерывания снимает запрос на прерывание. Одновременно на выходе элемента И 17 формируется сигнал низкого уровня, поступающий на первый вход элемента И 19, вызывая появление сигнала низкого уровня на его выходе. В результате на выходе первого дешифратора 18 появляется восьмиразрядный код адреса вектора прерывания 24, поступающий на магистральные линии АДО...АД7 Q-шины. Далее на выходе элемента 20 задержки появляется сигнал ответа 21 устройства RPLY. Процессор принимает адрес вектора прерывания 24 и Снимает сигналы 3, 4. При этом на выходе элемента И-НЕ 37 и соответственно на втором выходе второго узла обработки запроса первого блока 2 приоритета появляется сигнал высокого уровня, по фронту которого (переход из низкого уровня в высокий) происходит установка триггера D-типа 36 в исодное состояние. Заявляемое устройство авершает передачу адреса вектора и- сниает сигнал 21. По окончании импульса на ыходе рдновибратора 6 заявляемое устойство вновь выставляет выходной сигнал 15 при наличии запросов (требований) нешних .устройств, поступающих на перые 9 или вторые Т1 з апросные входы. При оявлении запроса IRQ2 второй группы запросов 11 и отсутствии маскирования по

анному запросу на выходе элемента ИЛИ группы элементов ИЛИ 8 появляется сигнал низкого уровня, поступающий на третий вход второго узла обработки запроса второго блока 13 приоритета. В результате на первом выходе второго узла обработки запроса появляется сигнал низкого уровня, поступающий на четвертый вход элемента И 14/что вызывает появление выходного сигнала запроса 15 (фиг. 4), По выполнении очередной команды процессор удовлетворяет требование запроса, вырабатывая сиг- нальГ 3, 4, также Низкого уровня (нулевой потенциал). Сигналом высокого уровня с выхода элемента ИЛИ-НЕ 5 запускается одно- вибратор 6. Требование запроса на прерывание 15 снимается. Блокируется также поступление запросов на третьи входы узлов обработки запросов на прерывание первого 2 и второго 13 блоков приоритета. Далее сигналом с выхода элемента ИЛИ-НЕ 5 последовательно по приоритету опрашиваются узлы обработки запросов первого блока 2 приоритета и первый узел обработки запросов второго блока 13 приоритета.

При отсутствии зафиксированных запросов в более высокоприоритетных узлах обработки запросо в-сигнал подтверждения прерывания поступает на второй вход второго узла обработки запроса второго блока 13 приоритета1, на втором выходе которого появляется потенциал низкого уровня. Данный сигнал входит в состав второй группы выходов 25 подтверждения прерывания и поступает на вход источника запроса на прерывание IRQ2. Одновременно сигнал низкого уровня поступает на второй вход элемента И 26. При этом на выходе данной схем ы формируется сигнал низкого уровня, являющийся выходом 28 занятости устройства, поступающий на второй управляющий вход второго дешифратора 27, При этом на выходе второго дешифратора 27 формируются выходные сигналы согласно фиг. 5. Выходные сигналы 33, 35 поступают на шину VME. Получала подтверждение 25, источник запроса I RCte проверяет выполнение следующих условий: соответствует ли его приоритет уровням на линиях А01...АОЗ, ожидаемая разрядность данных (линии DSO, DS1,

(WQPD) больше или равна разрядности его слова-статуса.

Если все условия выполнены, источник сообщает об этом, устанавливая на линиях

шины VME второй 31 и третий 32 управляющие сигналы низкого уровня. В результате на выходах элемента И 30, элемента ИЛИ 29 и элемента И 19 формируются сигналы низкого уровня.. На выходах первого дешифра0 тора 18 формируется адрес вектора прерывания 24, а на выходе элемента 20 задержки - сигнал ответа 21 устройства. Процессор принимает адрес вектора прерывания 24 и снимает сигналы 3, 4, что пр.иво5 дит к появлению сигнала высокого уровня на втором выходе второго узла обработки запроса второго блока 13 приоритета. При этом триггер D-типа 36 данного узла устанавливается в исходное (начальное)состря0 ние. Сигнал высокого уровня появляется на выходе элемента И 26 и выходе 28 устройства. Данный сигнал блокирует работу второго дешифратора 27 и на его выходах и выходах 33, 35 устройства в целом также

5 появляются сигналы высокого уровня, что приводит к снятию источником прерывания сигналов 31 или 32. Учитывая высокую скорость работы устройства ввода-вывода, имеющих интерфейс шины VME (минималь0 ное время цикла равно 100 не), время обслуживания сигналов запроса шины VME процессором Q-шины составляет примерно . 2...3 мкс. Следует отметить, что запрос шины VME сохраняется в течение 2 мкс по

5 окончании его обслуживания (фиг. 4). В течение этого времени процессором выполняется подпрограмма обслуживания прерывания (не определяется протоколом VME). При этом одновибратором 6 обеспе0 чивается блокировка формирования выходного сигнала 15 запроса устройства.

Заявляемое устройство обеспечивает последовательное обслуживание запросов на прерывание Q-шины и шины VME с воз5 можностью наращивания данных устройств. В этом случае выходной сигнал расширения 23 первого устройства приори- тетного прерывания является входным сиг-, налом 4 второго устройства приоритетного

0 прерывания. Наивысшим приоритетом обслуживания запросов Q-шины обладает первый вход первой группы запросов 9, наинизшим - n-й вход. Наивысшим приоритетом обслуживания запросов шины VME

5 также обладает первый вход второй группы запросов 11, наинизшим - m-й вход. Поскольку шина VME имеет семь линий (уровней) запросов на прерывания, то линия с наивысшим приоритетом соединяется с первым входом второй группы запросов 11.

Выбором и формированием выходных адресных 33 и управляющих 35 сигналов заявляемое устройство обеспечивает

обслуживание запросов внешних устройств, имеющих интерфейс шины VME с длиной слова 8, 16, 24, 32 бит.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1984 |

|

SU1226479A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| Устройство приоритета | 1989 |

|

SU1705826A1 |

| Система коммутации устройств обработки информации | 1989 |

|

SU1798796A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Система коммутации устройств обработки информации | 1989 |

|

SU1802362A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

Изобретение относится к вычислитель ной технике и может быть использовано в микропроцессорных вычислительных системах для обслуживания запросов на преры- вание Q-шины и шины VME. Цель изобретения - расширение области применения устройства за счет совместной обработки запросов различных магистралей. Устройство приоритетного прерывания содержит два блока приоритета, элемент НЕ, элемент ИЛИ-НЕ, одновибратор, группу элементов ИЛИ, пять элементов И, два элемента ИЛИ, элемент задержки, два дешифратора: и блок элементов задержки. Устройство позволяет совместно централизованно обрабатывать запросы на прерывание как Q-шины, так и шины.УМЕ.. 1 з.п. ф-лы, 5мл.

Формула изобретения

первого блока приоритета, первые выходы узлов обработки запросов первого и второго блоков приоритета соединены с соответствующими входами первого элемента И, выход которого соединён с вторым входом первого элемента ИЛИ, выход которого является выходом устройства для подключения к шине запроса на прерывание первой магистрали, вторые выходы узлов обработки запросов,первого блока приоритета соединены с соответствующими входэм и второго элемента И, первой группой информационных, входов первого дешифратора и являются первой группой выходов подтверждения прерывания устройства, третий выход 1-го (1 1, п-1) узла обработки запросов

первого блока приоритета соединен с вторым входом (i+1)-ro узла обработки запросов, третий выход n-го узла обработки запроса первого блока приоритета соединен с вторым входом первого узла обработки запроса второго блока приоритета, третий выход т-го узла обработки запроса которого соединен с входом элемента НЕ, выход которого является выходом расширения устройства, выход второго элемента И соединен с первым входом третьего элемента И, выход которого соединен со стробиру- ющим входом первого дешифратора и входом элемента задержки, выход которого

. является выходом устройства для подключения к шине ответа первой магистрали, выходы первого дешифратора являются

.выходами устройства для подключения к. шинам адреса первой магистрали, вторые выходы узлов обработки запросов второго блока приоритета соединены с соответствующими входами четвертого элемента И, второй группой информационных входов первого дешифратора, первой группой информационных входов второго дешифратора и являются второй группой выходов подтверждения прерывания устройства, выход четвертого элемента И соединен с первым входом второго элемента ИЛИ, вторым стробирующим входом второго дешифратора и является выходом устройства для подключения к шине занятости второй магистрали, первый вход пятого элемента И является входом устройства для подключения к шине подтверждения данных второй

магистрали, второй вход пятого элемента И является;третьим управляющим входом устройства для подключения к шине ошибки передачи второй магистрали, выход пятого элемента И соединен с вторым входом второго элемента ИЛИ. выход которого соединен с вторым входом третьего элемента И, первая группа выходов второго дешифратора является группой выходов устройства для подключения к шинам адреса второй маги- . страли, вторая группа выходов которого соединена с соответствующими входами блока элементов з адержки, выходы которого являются группой выходов устройства для подключения к шинам синхронизации адреса, стробом данных второй магистрали, третий выход j-го О 1, т-1)узла обработки запросов второго блока приоритета соединен с вторым входом (j+1)-ro узла обработки запросов.

Рог.З

Фиг. 2

«О

«

М

Ј

| Микропроцессорные средства и системы, 1987, Ms 5, с.43-55 | |||

| Преснухин А.Н | |||

| МикроЭВМ, кн | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-02-07—Публикация

1990-05-30—Подача