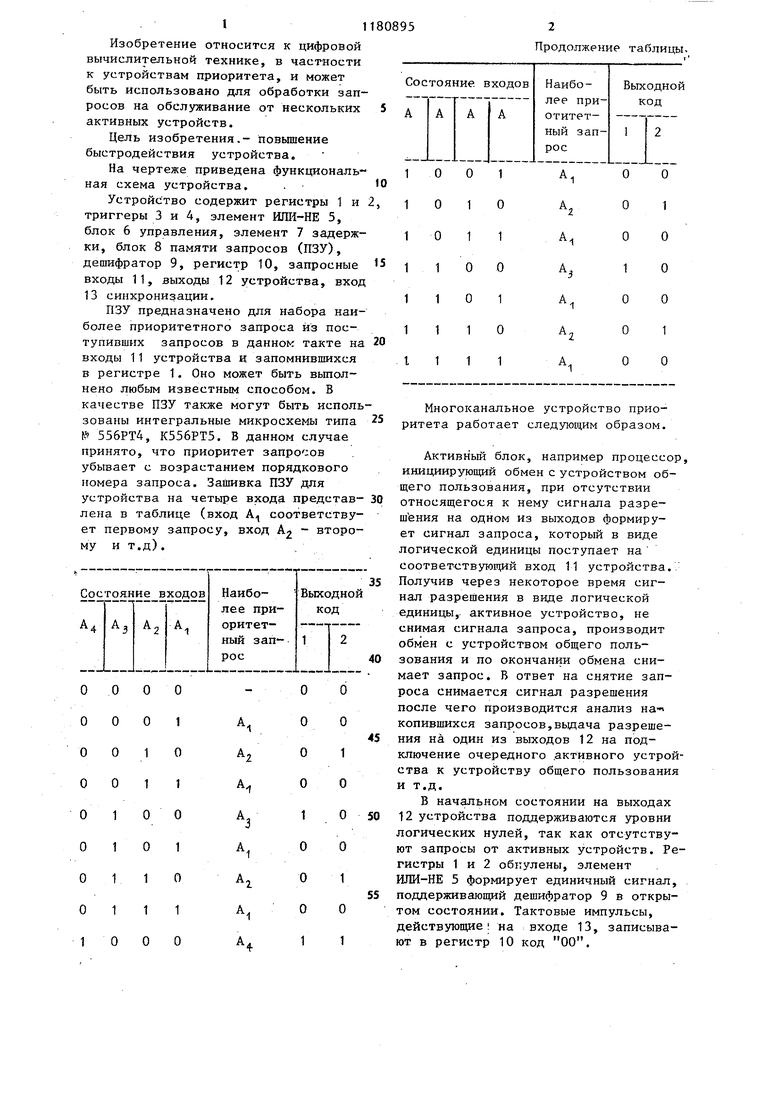

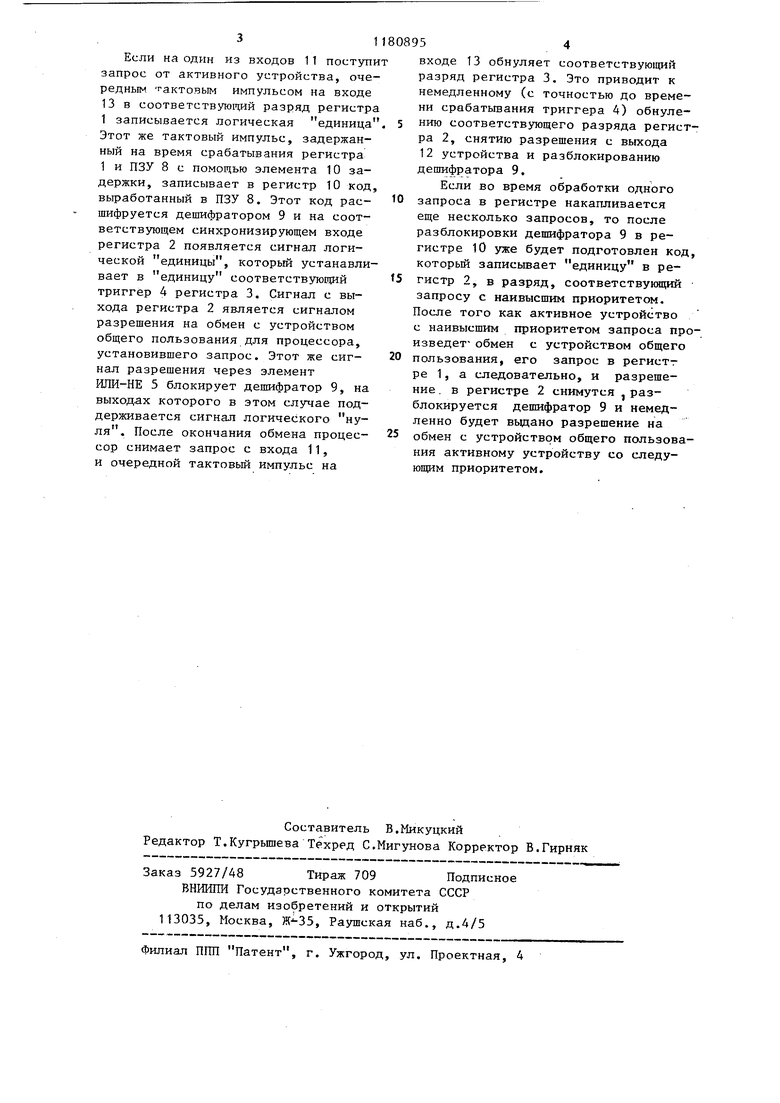

I Изобретение относится к цифровой вычислительной технике, в частности к устройствам приоритета, и может быть использовано для обработки запросов на обслуживание от нескольких активных устройств. Цель изобретения.- повьшение быстродействия устройства. На чертеже приведена функциональная схема устройства. Устройство содержит регистры 1 и триггеры 3 и 4, элемент HJlIi-HE 5, блок 6 управления, элемент 7 задержки, блок 8 памяти запросов (ПЗУ), дешифратор 9, регистр 10, запросные входы 11, выходы 12 устройства, вход 13 синхр ониз ации. ПЗУ предназначено для набора наиболее приоритетного запроса из поступивших запросов в данном такте на входы 11 устройства и запомнившихся в регистре 1. Оно может быть вьшолнено любым известным способом. В качестве ПЗУ также могут быть исполь зованы интегральные микросхемы типа fs 556РТ4, К556РТ5. В данном случае принято, что приоритет запросов убывает с возрастанием порядкового номера запроса. Зашивка ПЗУ для устройства на четыре входа представлена в таблице (вход А, соответствует первому запросу, вход второму и т.д).. 95 Продолжение таблицы. Многоканальное устройство приоритета работает следующим образом. Активный блок, например процессор, инициирующий обмен с устройством общего пользования, при отсутствии относящегося к нему сигнала разрешения на одном из выходов формирует сигнал запроса, который в виде логической единицы поступает на соответствующий вход 11 устройства. Получив через некоторое время сигнал разрешения в виде логической единицы, активное устройство, не снимая сигнала запроса, производит обмен с устройством общего пользования и по окончании обмена снимает запрос. В ответ на снятие запроса снимается сигнал разрешения после чего производится анализ на- копившихся запросов,вьщача разрешения на один из выходов 12 на подключение очередного .активного устройства к устройству общего пользования и т.д. В начальном состоянии на выходах 12 устройства поддерживаются уровни логических нулей, так как отсутствуют запросы от активных устройств. Регистры 1 и 2 обнулены, элемент ИЛИ-НЕ 5 формирует единичный сигнал, поддерживающий дешифратор 9 в открытом состоянии. Тактовые импульсы, действующие на входе 13, записывают в регистр 10 код 00.

Если на один из входов 11 поступи запрос от активного устройства, очередным актовым импульсом на входе 13 в соответствуюрщй разряд регистра 1 записывается логическая единица Этот же тактовый импульс, задержанный на время срабатывания регистра 1 и ПЗУ 8 с помощью элемента 10 задержки, записывает в регистр 10 код вьфаботанный в ПЗУ 8. Этот код расшифруется дешифратором 9 и на соответствующем синхронизирующем входе регистра 2 появляется сигнал логической единицы, который устанавливает в единицу соответствующий триггер 4 регистра 3. Сигнал с выхода регистра 2 является сигналом разрешения на обмен с устройством общего пользования для процессора, установившего запрос. Этот же сигнал разрешения через элемент ИЛИ-НЕ 5 блокирует дешифратор 9, на выходах которого в этом случае поддерживается сигнал логического нуля. После окончания обмена процессор снимает запрос с входа 11, и очередной тактовый импульс на

входе 13 обнуляет соответствующий разряд регистра 3. Это приводит к немедленному (с точностью до времени срабатьгаания триггера 4) обнулению соответствующего разряда регистра 2, снятию разрешения с выхода 12 устройства и разблокированию депшфратора 9.

Если во время обработки одного запроса в регистре накапливается еще несколько запросов, то после разблокировки дешифратора 9 в регистре 10 уже будет подготовлен код который записьшает единицу в регистр 2, в разряд, соответствукндий запросу с наивысшим приоритетом. После того как активное устройство с наивысшим приоритетом запроса произведет- обмен с устройством общего пользования, его запрос в регистт ре 1, а следовательно, и разрешение . в регистре 2 снимутся , разблокируется дешифратор 9 и немедленно будет вьщано разрешение на обмен с устройством общего пользования активному устройству со следующим приоритетом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1986 |

|

SU1352487A2 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Многоканальное приоритетное устройство | 1980 |

|

SU896624A1 |

| Приоритетное устройство | 1982 |

|

SU1027727A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Контроллер с переменным приоритетом | 1980 |

|

SU907550A1 |

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА, содержащее два регистра элемент ИЛИ-НЕ и блок управления, включающий дешифратор и элемент задержки, причем информационные входы первого регистра являются запросным входами устройства, выходы первого регистра.соединены с соответствующи ми разрядными информационными и установочными входами второго регистра, выходы которого подключены к входам элемента ИЛИ-НЕ и к выходам устройства, а вход синхронизации устройства соединен с входом синхронизации первого регистра и входом элемента задержки блока управления, выходы дешифратора блока управления соединены с входами синхронизации соответствующих разделов второго регистра, отличающееся тем, что, с целью повьппения быстродействия устройства, блок управления содержит регистр и блок памяти запросов, причем адресные входы блока памяти соединены с соответствующими выходами первого регистра, а выходы блока памяти запросов - с информационными выходами регистра блок управления, управляющий вход которого соединен с выходом элемента задержки, а информационные выходы регистра блока управления соединены с информационными входами дешифратора, управляющий вход которого подключен к выходу элемента ИЛИ-HF..

| Патент США № 4017841, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-06—Подача