113524952

Изобретение относится к вычисли-тивной ячейки памяти, выход 37 адрес- тельной технике и предназначено дляного чтения ассоциативной ячейки па- построения отказоустойчивых вычисли-мяти, 2т элементов И с тремя состоятельных систем.ниями 38, 38, , вход 39 задания режиЦель изобретения - повышение на-ма ассоциативного чтения блока,вход

дежности функционирования устройства40 разрешения работы блока, информаза счет реализации режима самодиагно-ционный вход 41 блока, вход 42 задатстирования и самоотключения отказав-ния режима адресного чтения блока,

ших блоков устройства. Qвыход 43 признака сравнения блока.

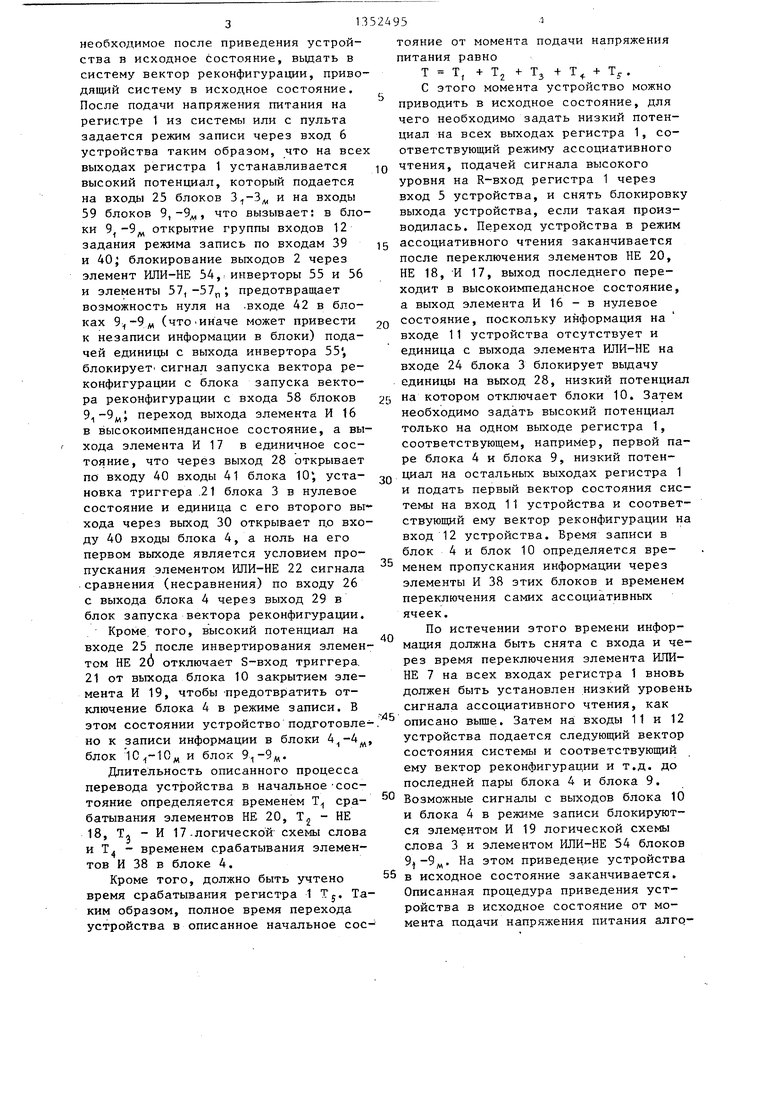

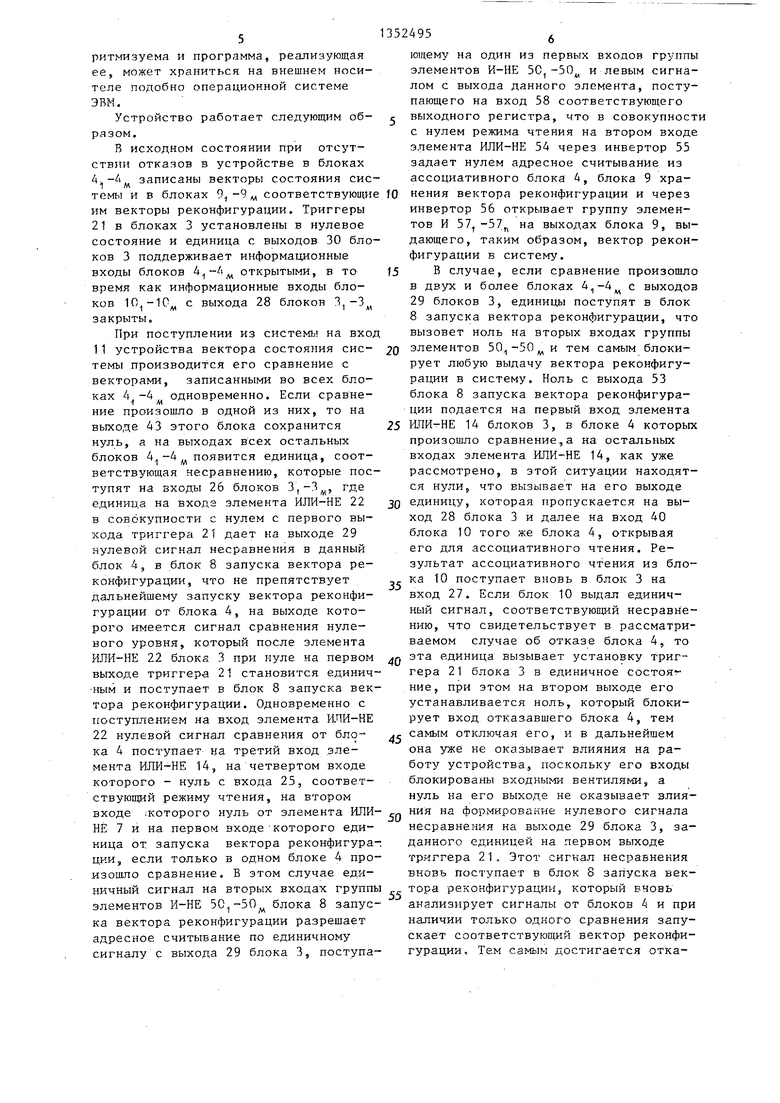

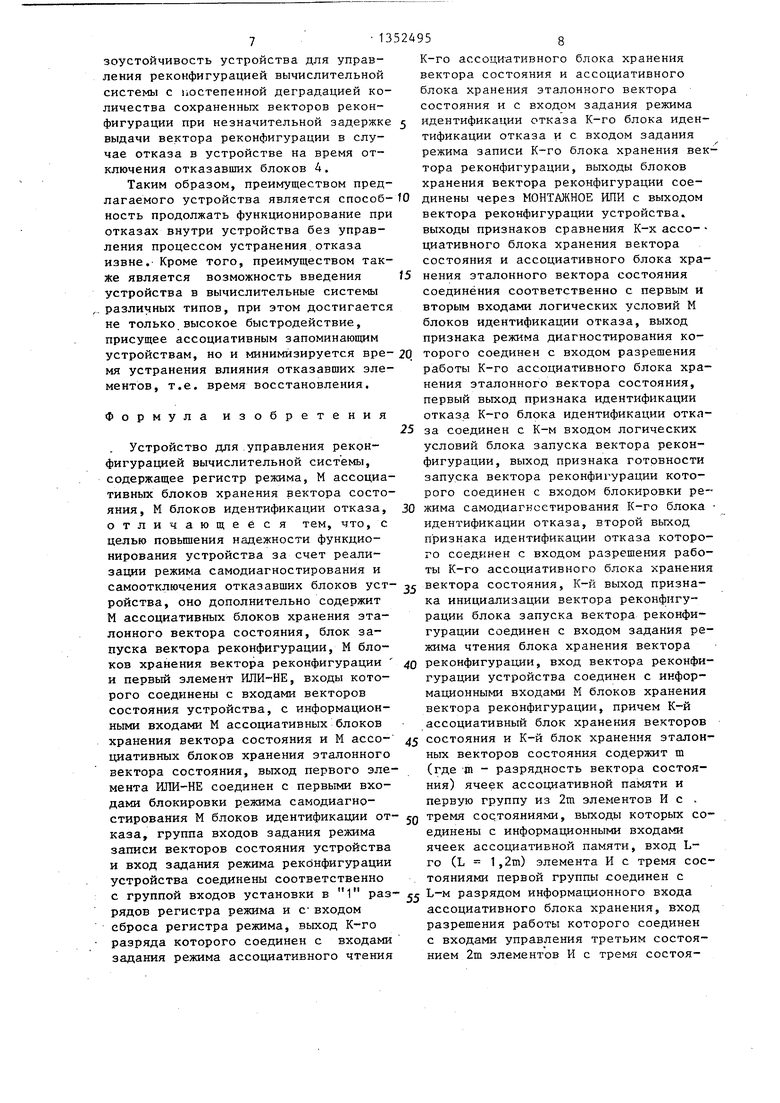

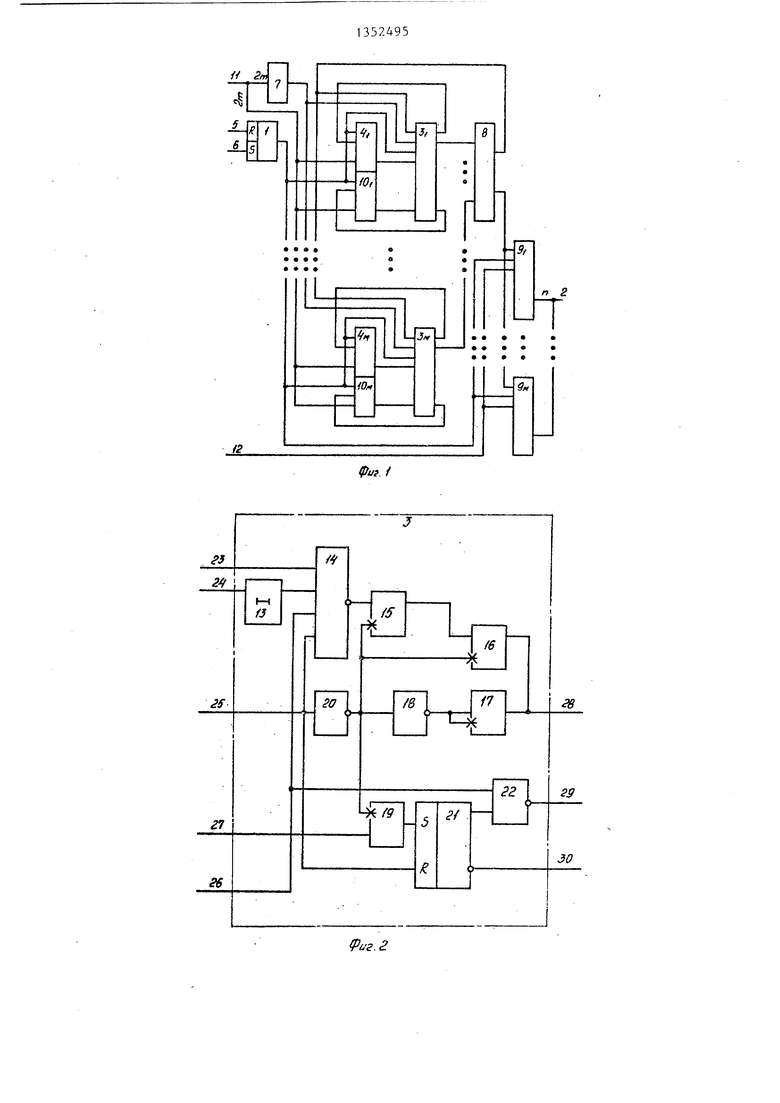

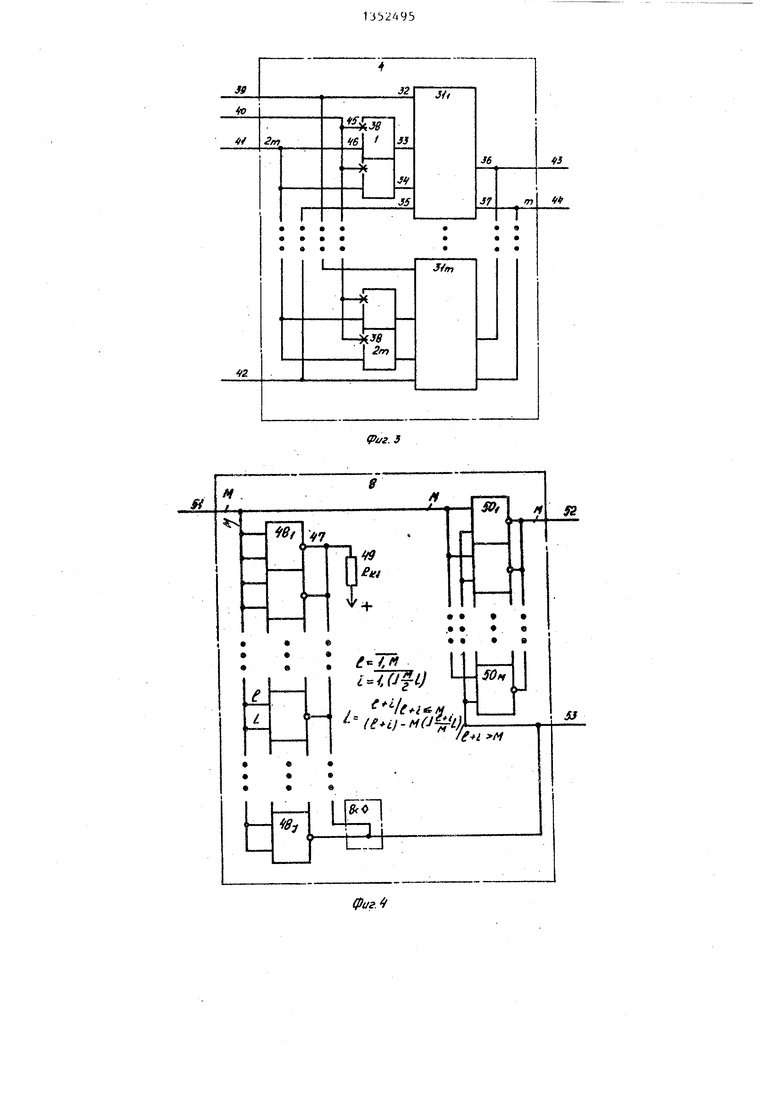

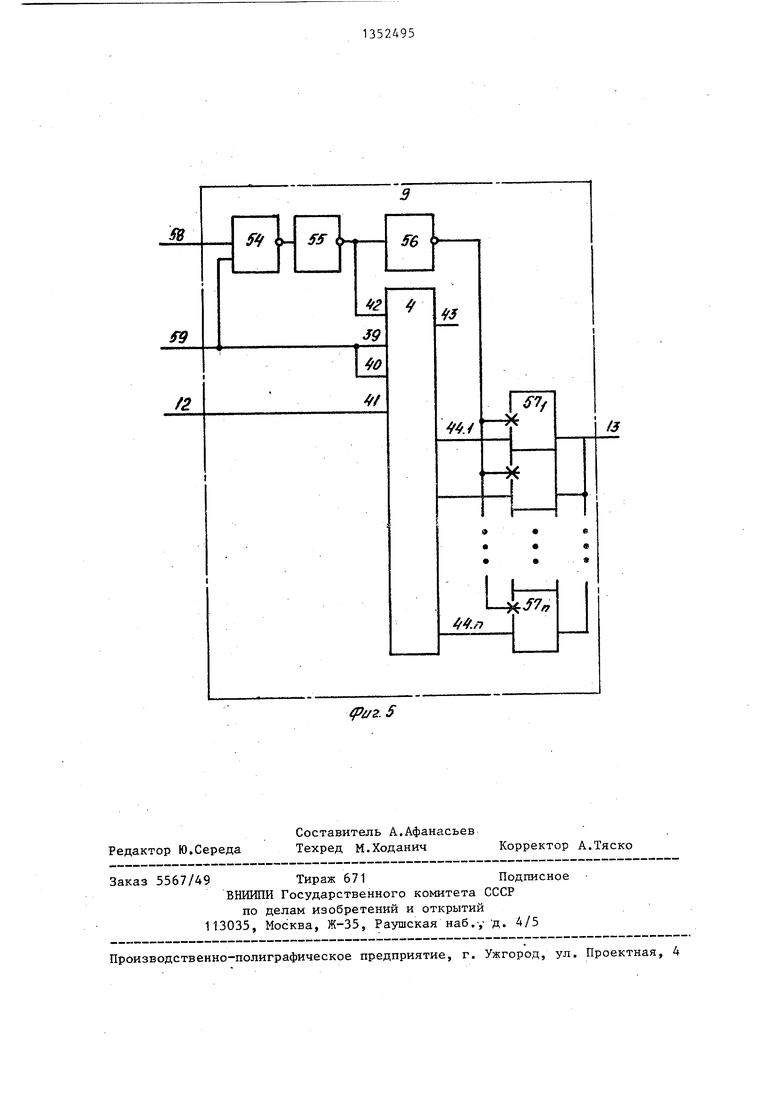

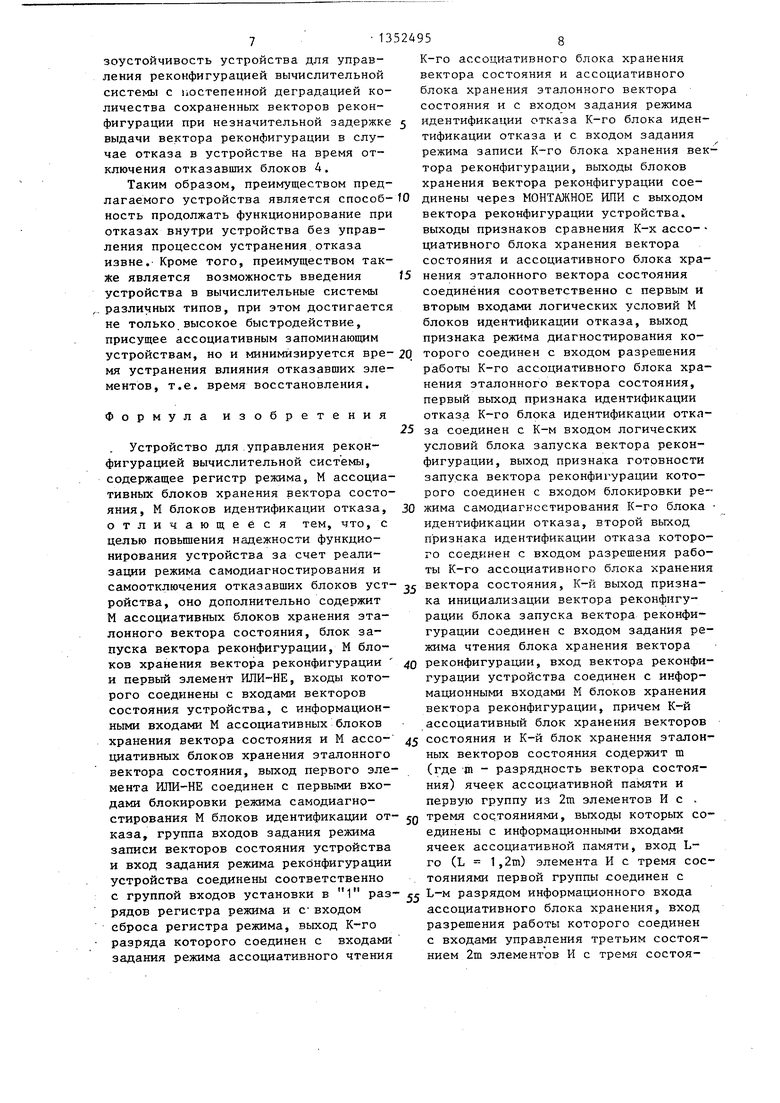

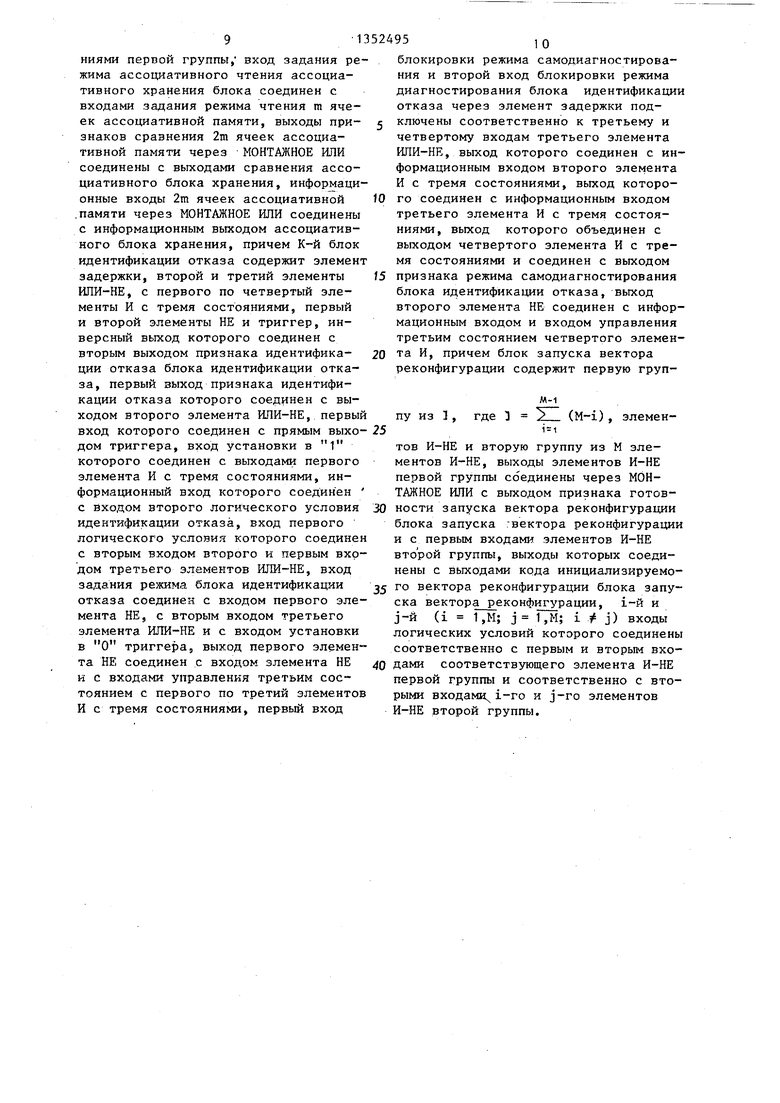

На фиг.1 приведена структурнаяинформационные выходы 44 блока, вход схема предлагаемого устройства для45 управления третьим состоянием и управления реконфигурацией вычисли-вход 46 элементов И группы, тельной системы; на фиг.2 - функцио- Блок запуска вектора реконфигура- нальная схема блока идентификации от- 5дии (фиг.4) содержит выходы 47 первой каза на фиг.З - функциональная схемагруппы элементов И-НЕ 48.-48 с от- блока хранения вектора состояния; накрытым коллектором, количество кото- фиг. 4 - функциональная схема блокарых определяется числом сочитаний из запуска вектора реконфигурации; наМ по 2 по формуле фиг.5 - функциональная схема блока joм хранения вектора реконфигурации. I С ---г- ггт.

Устройство (фиг.1) содержит ре-„ -v ;. гистр 1 режима, выход 2 вектора ° запуска вектора реконфигурации устройства, М блоковконфигурации содержит резистор R,,,49 идентификации отказа 3,-3«, М-т-раз- питания элемен- рядных ассоциативных блоков хранения ° И-1Ь, вторую группу элементов

/ / сИ-НЕ 50.1-50.М. входы 51 логических вектора состояния 4.-4м- вход 5 зада- „

,„условии, группу выходов 52 кода ининия режима реконфигурации устройства, i- . м

,циализируемого вектора реконфигура- входы 6 задания режима записи векто-..„ , выход 53 признака готовности роа состояния устройства, первый -эле- tn

мент Ш1И-НЕ 7, блок 8 запуска векто- ° кто реконфигурации ра реконфигурации, блок 9 хранения ° хранения вектора реконфигу. , ч,рации содержит ассоциативный блок вектора реконфигурации, М ассоциатив.0хранения вектора реконфигурации, ана- ных блоков 10 хранения эталонных век-«- ,,

торов состояния, вход 11 вектора со- о™чньш ассоциативному блоку хране- „,0 35 ния вектора состояния или ассоциативстояния устройства, вход 12 вектора «--.ному блоку хранения эталонного вектореконфигурации устройства.с/ пг ,„

, . /, -1Л ра состояния, элементы 54 и 55 и ИЛИ- Блок идентификации отказа (фиг.2) „„ .-,,,

,ГНЕ 56 и группу элементов И с тремя

содержит элемент (: задержки, элемент ..

„ ™ /,, ,г ,-,состояниями 57. -57...

ИПИ-НЕ 14, элементы И 15-17 с тремя ,„

гтг- 40 тт 0 Устройство выполняет функции уст- состояниями, элемент НЕ 18, элемент И „ ч. MJ yv..

tnттт- роиства для управления реконфигураци19с тремя состояния - : :, элемент НЕн, i f t- .

п 01 - ей вычислительной системы только в 20, триггер /I, первый и второй входы

г,., п/ ,-режиме ассоциативного чтения. Поэтому

23 и 24 блокировки режима самодиагно- „ . i у

тсработе устройства предшествует привестирования, вход 25 задания режима, t- « j f

с., 45 дение устройства в начальное состоявходы первого 26 и второго 27 логи00ние после подачи напряжения питания ческих условии, выход 28 признака ре

„ onи затем приведение его в исходное

жима самодиагностирования, первый 29 , ,„

„ опсостояние записью в блоки 4 и 10 и второй 30 выходы признака иденти,векторов состояния системы и соответ- фикации отказа.

50 ствующих им векторов реконфигура щи

Ассоциативный блок хранения векто-в предопределенные блоки 9 под управ- ра состояния (фиг.З) содержит m ассо- -лением извне. Приведение устройства циативньпх ячеек памяти , вкодв начальное состояние начинается по- 32 задания режима записи (ассоциатив-дачей в него напряжения питания При ного чтения) ассоциативной ячейки . . 55 этом выходы устройства можно блоки- памяти , информационные входы 33 и 34,ровать средствами системы, в которую вход 35 задания режима адресного чте-встраивается устройство, на .время, ния ассоциативной ячейки памяти, вы-необходимое для завершения переходных ход 36 ассоциативного чтения ассоциа-процессов после включения питания или

3

необходимое после приведения устройства в исходное состояние, вьщать в систему вектор реконфигурации, приводящий систему в исходное состояние. После подачи напряжения питания на регистре 1 из системы или с пульта задается режим записи через вход 6 устройства таким образом, что на все выходах регистра 1 устанавливается высокий потенциал, который подается на входы 25 блоков , и на входы 59 блоков 9,-Эд,, что вызывает: в блоки открытие группы входов 12 задания режима запись по входам 39 и 40 блокирование выходов 2 через элемент ИЛИ-НЕ 54, инверторы 55 и 56 и элементы 57, предотвращает возможность нуля на .входе 42 в блоках , (что Иначе может привести к незаписи информации в блоки) подачей единицы с выхода инвертора 55, блокирует сигнал запуска вектора реконфигурации с блока запуска вектора реконфигурации с входа 58 блоков переход выхода элемента И 16 в высокоимпендансное состояние, а выхода элемента И 17 в единичное состояние, что через выход 28 открывает по входу 40 входы 41 блока 10, установка триггера .21 блока 3 в нулевое состояние и единица с его второго вы хода через выход 30 открывает п.о входу 40 входы блока 4, а ноль на его первом выходе является условием пропускания элементом ИЛИ-НЕ 22 сигнала сравнения (несравнения) по входу 26 с выхода блока 4 через выход 29 в блок запуска вектора реконфигурации

Кроме того, высокий потенциал на входе 25 после инвертирования элементом НЕ 20 отключает S-вход триггера. 21 от выхода блока 10 закрытием элемента И 19, чтобы -предотвратить отключение блока 4 в режиме записи, В этом состоянии устройство подготовлено к записи информации в блоки блок , и блок 9,-9д,.

Длительность описанного процесса перевода устройства в начальное-сос

м

тояние определяется временем Тх

сра- НЕ

батывания элементов НЕ 20, - И 17-логической с временем срабатывания элемен- 58 в блоке 4, Кроме того, должно быть учтено

Т «

2 18, Тл - И 17-логической схемы слова

и Т, тов и 38 в блоке 4,

время срабатывания регистра 1 Tj,

ким образом, полное время перехода устройства в описанное начальное сос.:

b

10

15

20

25

30

тояние от момента подачи напряжения питания равно

Т Т, + Т + Тз -t- Т + Ту . С этого момента устройство можно приводить в исходное состояние, для чего необходимо задать низкий потенциал на всех выходах регистра 1, соответствующий режиму ассоциативного чтения, подачей сигнала высокого уровня на R-вход регистра 1 через вход 5 устройства, и снять блокировку выхода устройства, если такая производилась. Переход устройства в режим ассоциативного чтения заканчивается после переключения элементов НЕ 20, НЕ 18, И 17, выход последнего переходит в высокоимпедансное состояние, а выход элемента И 16 - в нулевое состояние, поскольку информация на входе 11 устройства отсутствует и единица с выхода элемента ИЛИ-НЕ на входе 24 блока 3 блокирует вьщачу единицы на выход 28, низкий потенциал на котором отключает блоки 10. Затем необходимо задать высокий потенциал только на одном выходе регистра 1, соответствующем, например, первой паре блока 4 и блока 9, низкий потенциал на остальных выходах регистра 1 и подать первый вектор состояния системы на вход 11 устройства и соответствующий ему вектор реконфигурации на вход 12 устройства. Время записи в блок 4 и блок 10 определяется вре менем пропускания информации через элементы И 38 этих блоков и временем переключения самих ассоциативных ячеек.

По истечении этого времени информация должна быть снята с входа и через время переключения элемента ИЛИ- НЕ 7 на всех входах регистра 1 вновь должен быть установлен низкий уровень сигнала ассоциативного чтения, как . описано выше. Затем на: входы 11 и 12 устройства подается следующий вектор состояния системы и соответствующий ему вектор реконфигурации и т.д. до последней пары блока 4 и блока 9.

50 Возможные сигналы с выходов блока 10 и блока 4 в режиме записи блокируются элементом И 19 логической схемы слова 3 и элементом ИЛИ-НЕ 54 блоков 9|-9„. На этом приведение устройства

55 в исходное состояние заканчивается, Описанная процедура приведения устройства в исходное состояние от момента подачи напряжения питания алго

40

ритмизуема и программа, реализующая ее, может храниться на внешнем носителе подобно операционной системе ЭВМ.

Устройство работает следующим образом.

В исходном состоянии при отсутствии отказов в устройстве в блоках . записаны векторы состояния сис

1 Л

и в блоках 9,-9 соответствующие им векторы реконфигурации. Триггеры

21в блоках 3 установлены в нулевое состояние и единица с выходов 30 блоков 3 поддерживает информационные входы блоков открытыми, в то время как информационные входы блоков с выхода 28 блоков 3,-3 закрыты.

При поступлении из системь на вход 11 устройства вектора состояния системы производится его сравнение с векторами, записанными во всех блоках одновременно. Если сравнение произошло в одной из них, то на выходе 43 этого блока сохранится нуль, а на выходах в сех остальных блоков появится единица, соответствующая несравнению, которые поступят на входы 26 блоков 3,-3, где единица на входа элемента ИЛИ-НЕ 22 в совокупности с нулем с первого выхода триггера 21 дает на выходе 29 нулевой сигнал несравнения в данный блок 4, в блок 8 запуска вектора реконфигурации, что не препятствует дальнейшему запуску вектора реконфигурации от блока 4, на выходе которого имеется сигнал сравнения нулевого уровня, который после элемента ИЛИ-ИЕ 22 блока 3 при нуле на первом выходе триггера 21 становится единич- ным и поступает в блок 8 запуска вектора реконфигурации. Одновременно с поступлением на вход элемента ЯПИ-НЕ

22нулевой сигнал сравнения от блока 4 поступает на третий вход элемента ИЛИ-НЕ 14, на четвертом входе которого - нуль с входа 25, соответствующий режиму чтения, на втором входе :которого нуль от элемента ИЛИ- НЁ 7 и на первом входе-которого единица от запуска вектора реконфигурации, если только в одном блоке 4 произошло сравнение. В этом случае единичный сигнал на вторых входах группы элементов И-НЕ 50,-50. блока 8 запусг fA

ка вектора реконфигурации разрешает адресное считывание по единичному сигналу с выхода 29 блока 3, поступа

5

0

0

0

ющему на один из первых входов группы элементов И-НЕ 50,-50 и левым сигналом с выхода данного элемента, поступающего на вход 58 соответствующего выходного регистра, что в совокупности с нулем режима чтения на втором входе элемента ИЛИ-НЕ 54 через инвертор 55 задает нулем адресное считывание иэ ассоциативного блока 4, блока 9 хранения вектора реконфигурации и через инвертор 56 открывает группу элементов И на выходах блока 9, выдающего, таким образом, вектор реконфигурации в систему.

В случае, если сравнение произошло в двух и более блоках 4.-4. с выходов

I Д

29 блоков 3, единицы поступят в блок 8 запуска вектора реконфигурации, что вызовет ноль на вторых входах группы элементов и тем самым блокирует любую выдачу вектора реконфигурации в систему. Ноль с выхода 53 блока 8 запуска вектора реконфигурации подается на первый вход элемента

5 ИЛИ-НЕ 14 блоков 3, в блоке 4 которых произошло сравнение,а на остальных входах элемента ИЛИ-НЕ 14, как уже рассмотрено, в этой ситуации находятся нули, что вызывает на его выходе единицу, которая пропускается на выход 28 блока 3 и далее на вход 40 блока 10 того же блока 4, открывая его для ассоциативного чтения. Результат ассоциативного чтения из блока 10 поступает вновь в блок 3 на вход 27. Если блок 10 выдал единичный сигнал, соответствуюпщй несравнению, что свидетельствует в рассматриваемом случае об отказе блока 4, то

Q эта единица вызывает установку триггера 21 блока 3 в единичное состояг- ние, при этом на втором выходе его устанавливается ноль, который блокирует вход отказавщего блока 4, тем

f самым отключая его, и в дальнейшем она уже не оказывает влияния на работу устройства., поскольку его входы блокированы входными вентилями, а нуль на его выходе не оказывает влияния на формирование нулевого сигнала несравнения на выходе 29 блока 3, заданного единицей на первом выходе триггера 21, Этот сигнал несравнения вновь поступает в блок 8 запуска век тора реконфигурации, который вновь анализирует сигналы от блоков 4 и при наличии только одного сравнения запускает соответствующий вектор реконфигурации. Тем самым достигается отка5

зоустойчивость устройства для управления реконфигурацией вычислительной системы с постепенной деградацией количества сохраненных векторов реконфигурации при незначительной задержке выдачи вектора реконфигурации в случае отказа в устройстве на время отключения отказавших блоков 4.

Таким образом, преимуществом предлагаемого устройства является способкость продолжать функционирование при отказах внутри устройства без управления процессом устранения отказа извне. Кроме того, преимуществом также является возможность введения устройства в вычислительные системы различных типов, при этом достигается не только высокое быстродействие, присущее ассоциативным запоминающим устройствам, но и минимизируется вре- мя устранения влияния отказавших элементов, т.е. время восстановления.

Формула изобретения

Устройство для управления реконфигурацией вычислительной системы, содержащее регистр режима, М ассоциативных блоков хранения вектора состояния, М блоков идентификации отказа, отличающееся тем, что, с целью повышения надежности функционирования устройства за счет реализации режима самодиагностирования и

самоотключения отказавших блоков уст- вектора состояния, К-й выход признаройства, оно дополнительно содержит М ассоциативных блоков хранения эталонного вектора состояния, блок запуска вектора реконфигурации, М блоков хранения вектора реконфигурации и первый элемент ИЛИ-НЕ, входы которого соединены с входами векторов состояния устройства, с информационными входами М ассоциативных блоков хранения вектора состояния и М ассо- циативных блоков хранения эталонного вектора состояния, выход первого элемента ИЛИ-НЕ соединен с первыми входами блокировки режима самодиагностирования М блоков идентификации отказа, группа входов задания режима записи векторов состояния устройства и вход задания режима реконфигурации устройства соединены соответственно

ка инициализации вектора реконфигурации блока запуска вектора реконфигурации соединен с входом задания режима чтения блока хранения вектора

40 реконфигурации, вход вектора реконфигурации устройства соединен с информационными входами М блоков хранения вектора реконфигурации, причем К-й ассоциативный блок хранения векторов

45 состояния и К-й блок хранения эталонных векторов состояния содержит m (где т - разрядность вектора состояния) ячеек ассоциативной памяти и первую группу из 2т элементов И с .

5Q тремя состояниями, выходы которых соединены с информационными входами ячеек ассоциативной памяти, вход L- го (L 1,2т) элемента И с тремя состояниями первой группы соединен с

с группой входов установки в 1 раз- L-M разрядом информационного входа рядов регистра режима и с- входом ассоциативного блока хранения, вход сброса регистра режима, выход К-го разрешения работы которого соединен разряда которого соединен с входами с входами управления третьим состоя- задания режима ассоциативного чтения нием 2т элементов И с тремя состоя

5 0

5

0

К-го ассоциативного блока хранения вектора состояния и ассоциативного блока хранения эталонного вектора состояния и с входом задания режима идентификации отказа К-го блока идентификации отказа и с входом задания режима записи К-го блока хранения вектора реконфигурации, выходы блоков хранения вектора реконфигурации соединены через МОНТАЖНОЕ ИЛИ с выходом вектора реконфигурации устройства, выходы признаков сравнения К-х ассо- циативного блока хранения вектора состояния и ассоциативного блока хранения эталонного вектора состояния соединения соответственно с первым и вторым входами логических условий М блоков идентификации отказа, выход признака режима диагностирования которого соединен с входом разрешения работы К-го ассоциативного блока хранения эталонного вектора состояния, первый выход признака идентификации отказа К-го блока идентификации отказа соединен с К-м входом логических условий блока запуска вектора реконфигурации, выход признака готовности запуска вектора реконфигурации которого соединен с входом блокировки режима самодиагнсстирования К-го блока идентификации отказа, второй выход признака идентификации отказа которого соединен с входом разрешения работы К-го ассоциативного блока хранения

ка инициализации вектора реконфигурации блока запуска вектора реконфигурации соединен с входом задания реима чтения блока хранения вектора

реконфигурации, вход вектора реконфигурации устройства соединен с инфорационными входами М блоков хранения вектора реконфигурации, причем К-й ассоциативный блок хранения векторов

состояния и К-й блок хранения эталонных векторов состояния содержит m (где т - разрядность вектора состояния) ячеек ассоциативной памяти и первую группу из 2т элементов И с .

тремя состояниями, выходы которых соединены с информационными входами ячеек ассоциативной памяти, вход L- го (L 1,2т) элемента И с тремя состояниями первой группы соединен с

9 1

ниями первой группы, вход задания режима ассоциативного чтения ассоциативного хранения блока соединен с входами задания режима чтения га ячеек ассоциативной памяти, выходы при- знаков сравнения 2т ячеек ассоциативной памяти через МОНТАЖНОЕ ИЛИ соединены с выходами сравнения ассоциативного блока хранения, информационные входы 2т ячеек ассоциативной .памяти через МОНТАЖНОЕ ИЛИ соединены с информационным выходом ассоциативного блока хранения, причем К-й блок идентификации отказа содержит элемен задержки, второй и третий элементы ИПИ-НЕ, с первого по четвертый элементы И с тремя состояниями, первый и второй элементы НЕ и триггер, инверсный выход которого соединен с вторым выходом признака идентифика- ции отказа блока идентификации отказа, первый выход признака идентификации отказа которого соединен с выходом второго элемента ИПИ-НЕ, первы вход которого соединен с прямым выхо дом триггера, вход установки в 1 которого соединен с вьпсодами первого элемента И с тремя состояниями, информационный вход которого соедин ен с входом второго логического условия идентификации отказа, вход первого логического условия которого соедине с вторым входом второго и первым входом третьего элементов ИПИ-НЕ, вход задания режима блока идентификации отказа соединен с входом первого элемента HEj с вторым входом третьего элемента ИЛИ-НЕ и с входом установки в О триггера, выход первого элемен та НЕ соединен с входом элемента НЕ

и с входами управления третьим состоянием с первого по третий элементов И с тремя состояниями, первый вход

5

10

блокировки режима самодиагностирования и второй вход блокировки режима диагностирования блока идентификации отказа через элемент задержки подключены соответственно к третьему и четвертому входам третьего элемента ИЛИ-НЕ, выход которого соединен с информационным входом второго элемента И с тремя состояниями, выход которого соединен с информационным входом третьего элемента И с тремя состояниями, выход которого объединен с выходом четвертого элемента И с тремя состояниями и соединен с выходом признака режима самодиагностирования блока идентификации отказа, выход второго элемента НЕ соединен с информационным входом и входом управления третьим состоянием четвертого элемента И, причем блок запуска вектора реконфигурации содержит первую групМ-1

пу из 1, где и

(M-i), элемен1 1

j 10 /5 20 25

30

тов И-НЕ и вторую группу из М элементов И-НЕ, выходы элементов И-НЕ первой группы соединены через МОНТАЖНОЕ ИЛИ с выходом признака готовности запуска вектора реконфигурации блока запуска гвектора реконфигурации и с первым входами элементов И-НЕ второй группы, выходы которых соединены с выходами кода инициализируемо35 го вектора реконфигурации блока запуска вектора еконфигурации, i-й и jй (i 1 ,М; j 1,М; i / j) входы логических условий которого соединены соответственно с первым и вторым вхо40 дами соответствующего элемента И-НЕ

первой группы и соответственно с вторыми входами i-ro и j-ro элементов И-НЕ второй группы.

Редактор Ю.Середа

Составитель А.Афанасьев

Техред М.Ходанич Корректор А.Тяско

Заказ 5567/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.у д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

/г. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство управления обращением к памяти | 1984 |

|

SU1211737A1 |

| Матричное устройство для быстрого поиска вхождений и обработки данных | 2022 |

|

RU2787742C1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1833917A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| Способ и ассоциативное матричное устройство параллельного поиска образца по его префиксам | 2021 |

|

RU2760628C1 |

Изобретение относится к области вычислительной техники и предназначено для построения отказоустойчивости вычислительных систем. Цель изобретения - повьппение надежности функционирования за счет реализации режима самодиагностирования и самоотключения отказавших блоков. Устройство содержит регистр режима, М блоков идентификации отказа, М ассоциативных блоков хранения вектора состояния, элемент ИПИ-НЕ, блок запуска вектора реконфигурации, М блоков хранения вектора реконфигурации, М ассоциативных блоков хранения эталонных векторов состояния. 5 ил. со ел ю й со ел

| Способ электролитического получения алюминия | 1983 |

|

SU1186703A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Похонен Т | |||

| Ассоциативные запоминающие устройства | |||

| М-.: Мир, 1982, с | |||

| Велосипед, приводимый в движение силой тяжести едущего | 1922 |

|

SU380A1 |

Авторы

Даты

1987-11-15—Публикация

1985-07-15—Подача