Изобретение относится к вычислительной технике и предназначено для управления буферной памятью в устрой ствах обработки информации с иерархической организацией памяти.

Целью изобретения является повышение достоверности функционирования.

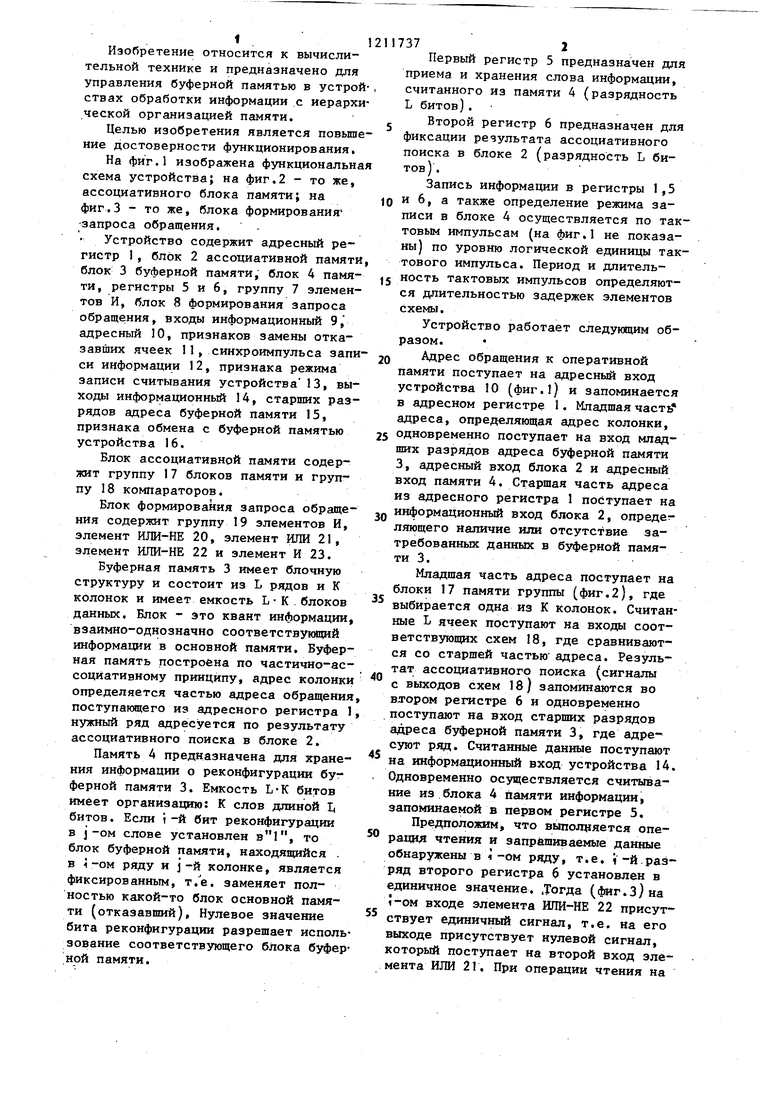

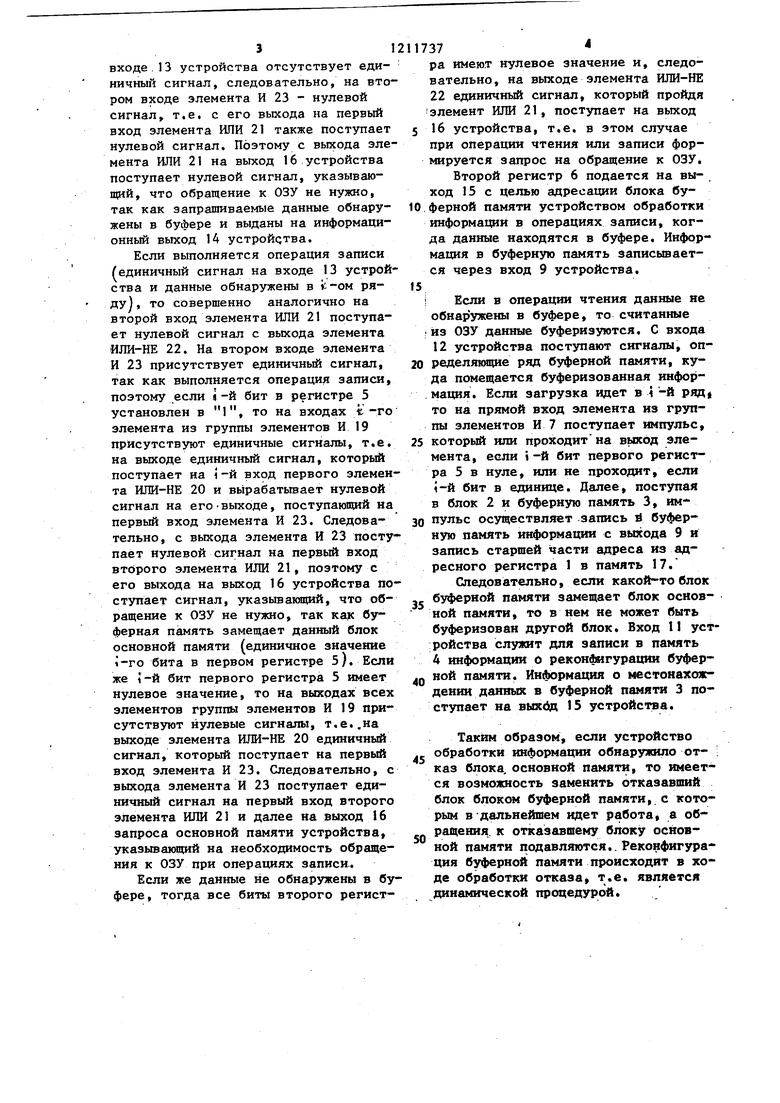

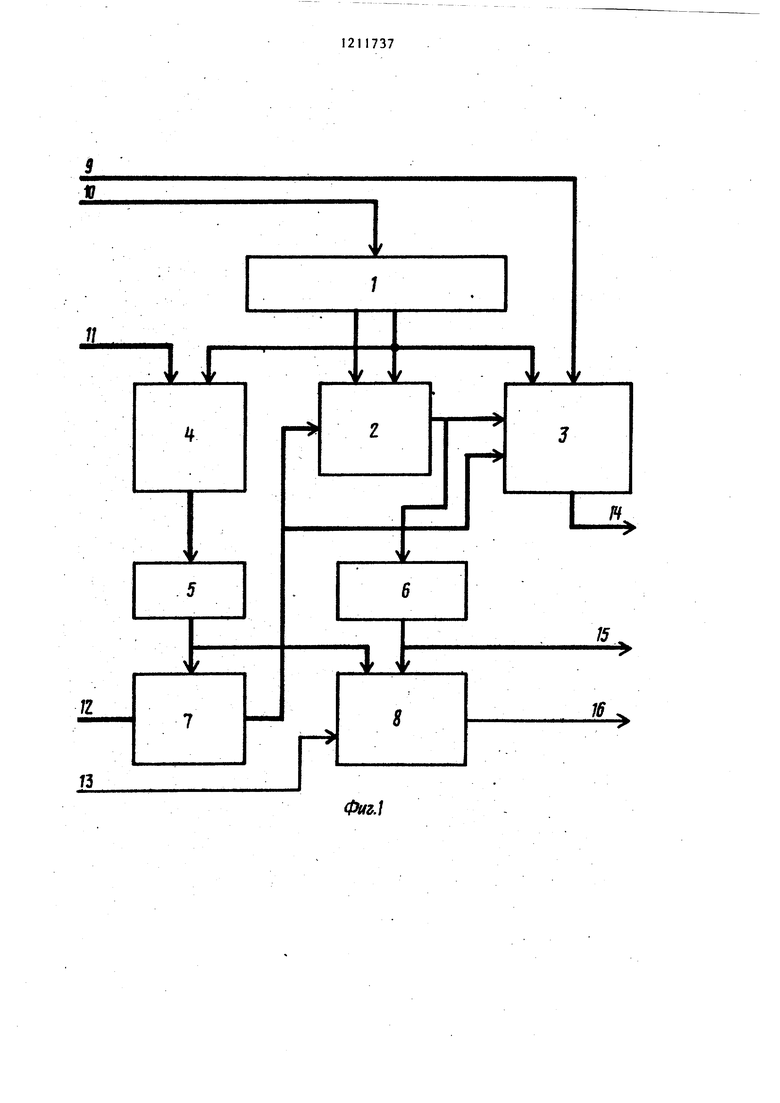

На фиг.1 изображена функциональна схема устройства; на фиг.2 - то же, ассоциативного блока памяти; на фиг.3 - то же, блока формирования -запроса обращения.

Устройство содержит адресный регистр 1, блок 2 ассоциативной памяти блок 3 буферной памяти, блок 4 памяти, регистры 5 и 6, группу 7 элементов И, блок 8 формирования запроса обращения, входы информационный 9, адресный 10, признаков замены отказавших ячеек 11, синхроимпульса записи информации 12, признака режима записи считывания устройства 13, выходы информационный 14, старших разрядов адреса буферной памяти 15, признака обмена с буферной памятью устройства 16.

Блок ассоциативной памяти содержит группу 17 блоков памяти и группу 18 компараторов.

Блок формирования запроса обращения содержит группу 19 элементов И, элемент ИЛИ-НЕ 20, элемент ШШ 21, элемент ИЛИ-НЕ 22 и элемент И 23.

Буферная память 3 имеет блочную структуру и состоит из L рядов и К колонок и имеет емкость L- К . блоков данных. Блок - это квант информации, взаимно-однозначно соответствующий информации в основной памяти. Буферная память построена по частично-ассоциативному принципу, адрес колонки определяется частью адреса обращения поступающего из адресного регистра 1 нужный ряд адресуется по результату ассоциативного поиска в блоке 2.

Память 4 предназначена для хранения информации о реконфигурации буферной памяти 3. Емкость L-K битов имеет организацто: К слов длиной If битов. Если I -и бит реконфигурации в j-ом слове установлен , то блок буферной памяти, находящийся . в 1-ом ряду и j-и колонке, является фиксированным, т.е. заменяет полностью какой-то блок основной памяти (отказавший). Нулевое значение бита реконфигурации разрешает использование соответствующего блока бзгфер- ной памяти.

0

5

0

5

0

5

0

5

0

5

Первый регистр 5 предназначен для приема и хранения слона информации, считанного из памяти 4 (разрядность L битов).

Второй регистр 6 предназначен для фиксации результата ассоциативного поиска в блоке 2 (разрядность L битов).

Запись информации в регистры 1,5 и 6, а также определение режима записи в блоке 4 осуществляется по тактовым импульсам (на фиг.1 не показаны) по уровню логической единицы тактового импульса. Период и длительность тактовых импульсов определяются длительностью задержек элементов схемы.

Устройство работает следующим образом.

Адрес обращения к оперативной памяти поступает на адресный вход устройства 10 (фиг.1) и запоминается в адресном регистре I. Мпадщая часть адреса, определяющая адрес колонки, одновременно поступает на вход младших разрядов адреса буферной памяти 3, адресный вход блока 2 и адресный вход памяти 4. Старшая часть адреса из адресного регистра 1 поступает на информационный вход блока 2, определяющего наличие или отсутствие затребованных данных в буферной памяти 3.

Младщая часть адреса поступает на блоки 17 памяти группы (фиг.2), где выбирается одна из К колонок. Считанные L ячеек поступают на входы соответствующих схем 18, где сравниваются со старшей частью адреса. Результат ассоциативного поиска (сигналы

с выходов схем 18/ запоминаются во втором регистре 6 и одновременно поступают на вход старших разрядов адреса буферной памяти 3, где адре- суют ряд. Считанные данные поступают на информационный вход устройства 14. Одновременно осуществляется считывание из блока 4 памяти информации, запоминаемой в первом регистре 5.

Предположим, что выполняется опе- рацнл чтения и запрйшиваемые данные обнаружены в i -ом ряду, т.е. i-и разряд второго регистра 6 установлен в единичное значение. .Тогда (фиг.З)на 1-ом входе элемента ИПИ-НЕ 22 присутствует единичный сигнал, т.е. на его выходе присутствует нулевой сигнал, который поступает на второй вход элемента ИЛИ 21. При операции чтения на

входе.13 устройства отсутствует еди- ничный сигнал, следовательно, на втором входе элемента И 23 - нулевой сигнал, т.е. с его выхода на первый вход элемента ИЛИ 21 также поступает нулевой сигнал. Поэтому с выхода элемента ИЛИ 21 на выход 16 устройства поступает нулевой сигнал, указывающий, что обращение к ОЗУ не нужно, так как запрашиваемые данные обнаружены в буфере и выданы на информационный выход 14 устройчтва.

Если выполняется операция записи (единичный сигнал на входе 13 устройства и данные обнаружены в k-ом ряду , то совершенно аналогично на второй вход элемента ИЛИ 21 поступает нулевой сигнал с выхода элемента ИЛИ-НЕ 22. На втором входе элемента И 23 присутствует единичный сигнал, так как выполняется операция записи, поэтому если i-и бит в регистре 5 установлен в 1, то на входах t -го элемента из группы элементов И 19 присутствуют единичные сигналы, т.е. на выходе единичньй сигнал, который поступает на -и вход первого элемента ИЛИ-НЕ 20 и вырабатьюает нулевой сигнал на еговыходе, поступающий на первый вход элемента И 23. Следовательно, с выхода элемента И 23 поступает нулевой сигнал на первый вход второго элемента ИЛИ 21, поэтому с его выхода на вькод 16 устройства поступает сигнал, указывакяций, что обращение к ОЗУ не нужно, так как буферная память замещает данный блок основной памяти (единичное значение i-ro бита в первом регистре 5). Если же |-й бит первого регистра 5 имеет нулевое значение, то на выходах всех элементов группы элементов И 19 присутствуют нулевые сигналы, т.е..на выходе элемента ИЛИ-НЕ 20 единичный сигнал, который поступает на первый вход элемента И 23. Следовательно, с выхода элемента И 23 поступает единичный сигнал на первый вход второго элемента ИЛИ 21 и далее на выход I6 запроса основной памяти устройства, указывающий на необходимость обращения к ОЗУ при операциях записи.

Если же данные не обнаружены в буфере, тогда все биты второго регистра имеют нулевое значение и, следовательно, на выходе элемента ИЛИ-НЕ 22 единичный сигнал, который пройдя элемент ИЛИ 21, поступает на выход

16 устройства, т.е. в этом случае при операции чтения или записи формируется запрос на обращение к ОЗУ. Второй регистр 6 подается на выход 15 с целью адресации блока буферной памяти устройством обработки информации в операциях записи, когда данные находятся в буфере. Информация в буферную память записывается через вход 9 устройства.

Если в операции чтения данные не обнаружены в буфере, то считанные из ОЗУ данные буферизуются. С входа 12 устройства поступают сигналы, определякяцие ряд буферной памяти, куда помещается буферизованная инфор- махдая. Если загрузка идет в { -и ряд« то на прямой вход элемента из группы элементов И 7 поступает импульс,

который или проходит на выход элемента, если i-и бит первого регистра 5 в нуле, или не проходит, если -й бит в единице. Далее, поступая в блок 2 и буферную память 3, импульс осуществляет запись и буферную память информации с выхода 9 и запись старшей части адреса из адресного регистра 1 в память 17.

Следовательно, если какой-то блок буферной памяти замещает блок основной памяти, то в нем не может быть буфернзован другой блок. Вход 11 устройства слуяит для записи в память 4 информации о реконфигурации буферной памяти. Информация о местонахождении данных в буферной памяти 3 поступает на Bbocdn 15 устройства.

45

50

Таким образом, если устройство обработки информации обнаружило от- каз блока, основной памяти, то имеется возможность заменить отказавший блок блоком буферной памяти, с которым в-дальнейшем идет работа, а обращения, к отказавшему блоку основной памяти подавляются.. Реконфигурация буферной памяти происходит в ходе обработки отказа, т.е. является динамической процедурой.

f f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для формирования адреса замещаемого блока памяти | 1990 |

|

SU1777142A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1163361A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU959166A1 |

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

/z

Ё

Я.

8

W

CmapMOft часть адреса

Младшая часть чдрвса

5 6

r,zr

Qt

/3

И

п

Составитель M.Ctuura;

Редактор Н.Швыдкая Техред Т.Тупик : Корректор Е. Сирохман,

Заказ 6AI/53 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г, Ужгород, ул. Проектная, 4

а

J$

/

т . I т

Ш Ж.,

djoec 1№9а

we.f

j

2/

/

23

ФИ9.

| Белкин Г.Г | |||

| и др. | |||

| ПРИБОР ДЛЯ ИНТЕГРИРОВАНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ И ДЛЯ НАХОЖДЕНИЯ КОРНЕЙ ЧИСЛЕННЫХ УРАВНЕНИЙ | 1924 |

|

SU1045A1 |

| - Вопросы радиоэлектроники, сер | |||

| ЭВТ, вып | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Патент ОНА № 3840863, ,кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-11—Подача