Входная шина связи сЗЁМ

выходная шина сеязи с эан

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано для контроля цифровых блоков. Целью изобретения является повьшение оперативности контроля. Устройство содержит входную- и выходную шины связи с ЭВМ, буферный регистр 1, буферный блок памяти 2, блок памяти управления адресацией

€

(/)

;3, группу регистров 4, группу реги- ;строи кодов управления записью 5, счетчнк логических номеров 6, блок памяти 7, счетчик длины вектора тес- :тового набора 8, блок микропрограмм- 1НОГО управления 9, блок обмена с кон- |тролируемым цифровым блоком 10, ре- |гистр набора 11, выходной коммутатор И 2. Устройство позволяет при транс

; Изобретение относится к автоматике и вычислительной технике, может быть спользовано дяя контроля цифровых блоков и является усовершенствованием устройства по авт. св. № 1251084, I Цель изобретения - повышение опе- зативности контроля.

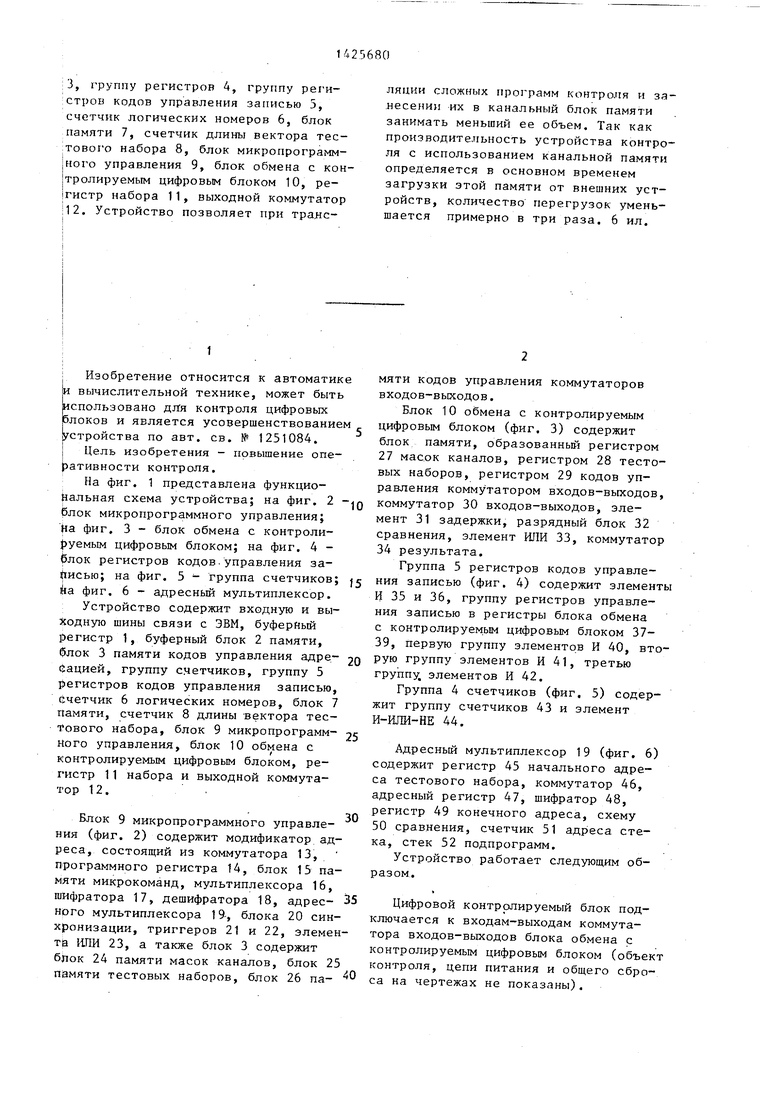

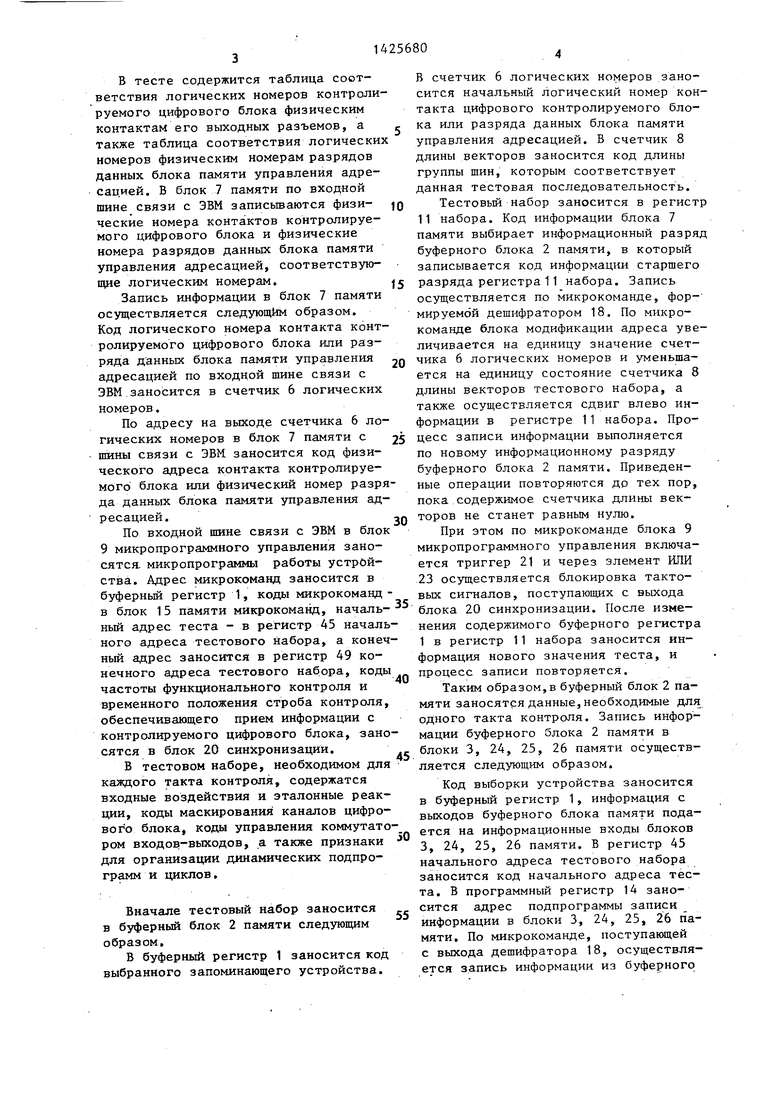

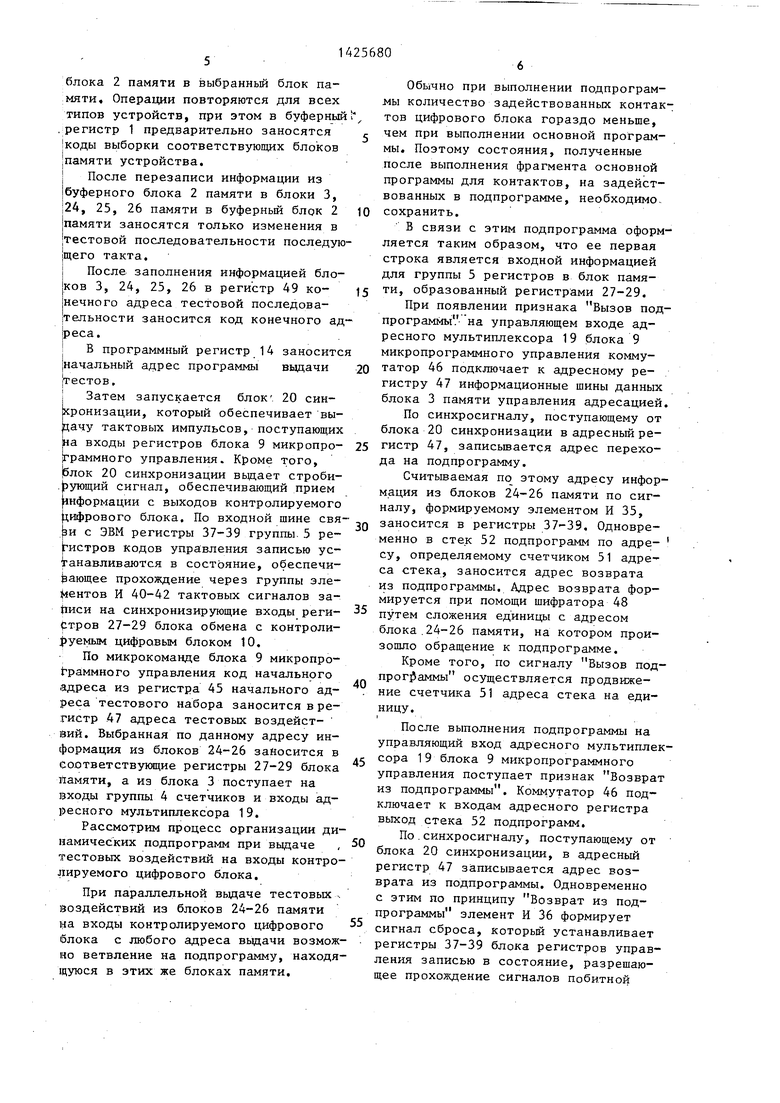

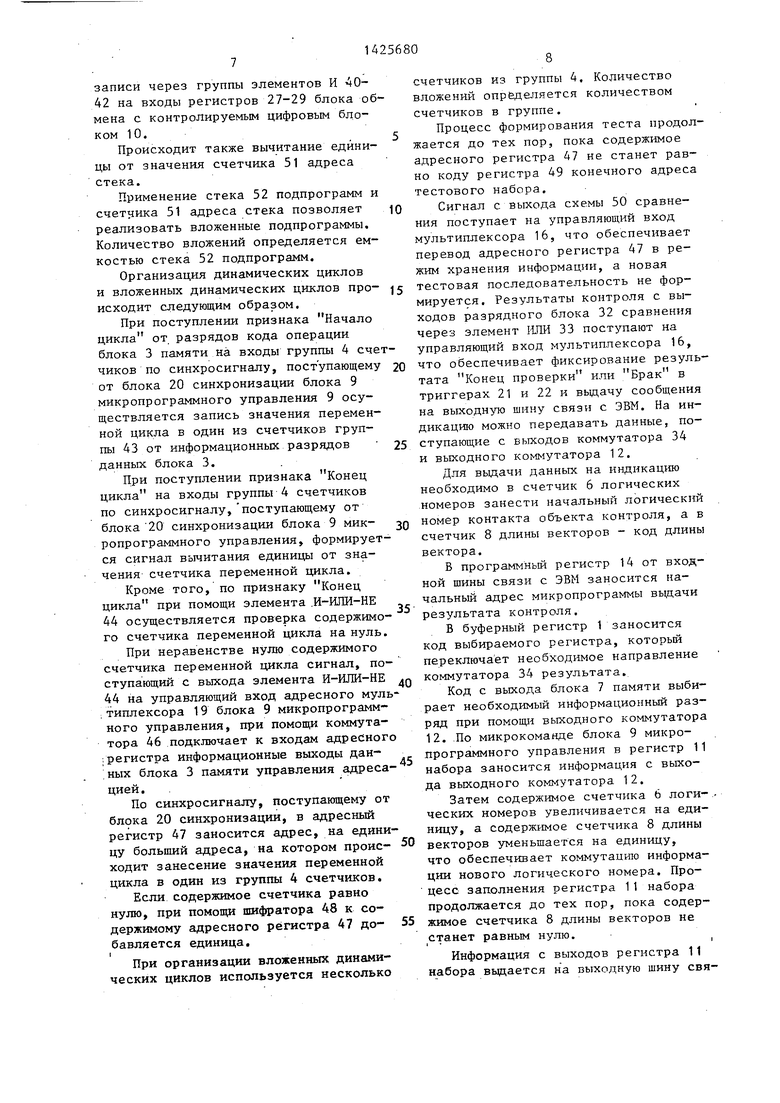

На фиг, 1 представлена функциональная схема устройства; на фиг. 2 блок микропрограммного управления; на фиг, 3 - блок обмена с контроли- jjyeMbiM цифровым блоком; на фиг. 4 - блок регистров кодов.управления записью; на фиг, 5 - группа счетчиков; а фиг, 6 - адресньй мультиплексор.

Устройство содержит входную и выходную шины связи с ЭВМ, буферный регистр 1, буферный блок 2 памяти, 0ЛОК 3 памяти кодов управления адре- Нацией, группу сметчиков, группу 5 регистров кодов управления записью, счетчик 6 логических номеров, блок 7 памяти, счетчик 8 длины вектора тестового набора, блок 9 микропрограмм- кого управления, блок 10 обмена с контролируемым цифровым блоком, регистр 11 набора и выходной коммутатор 12,

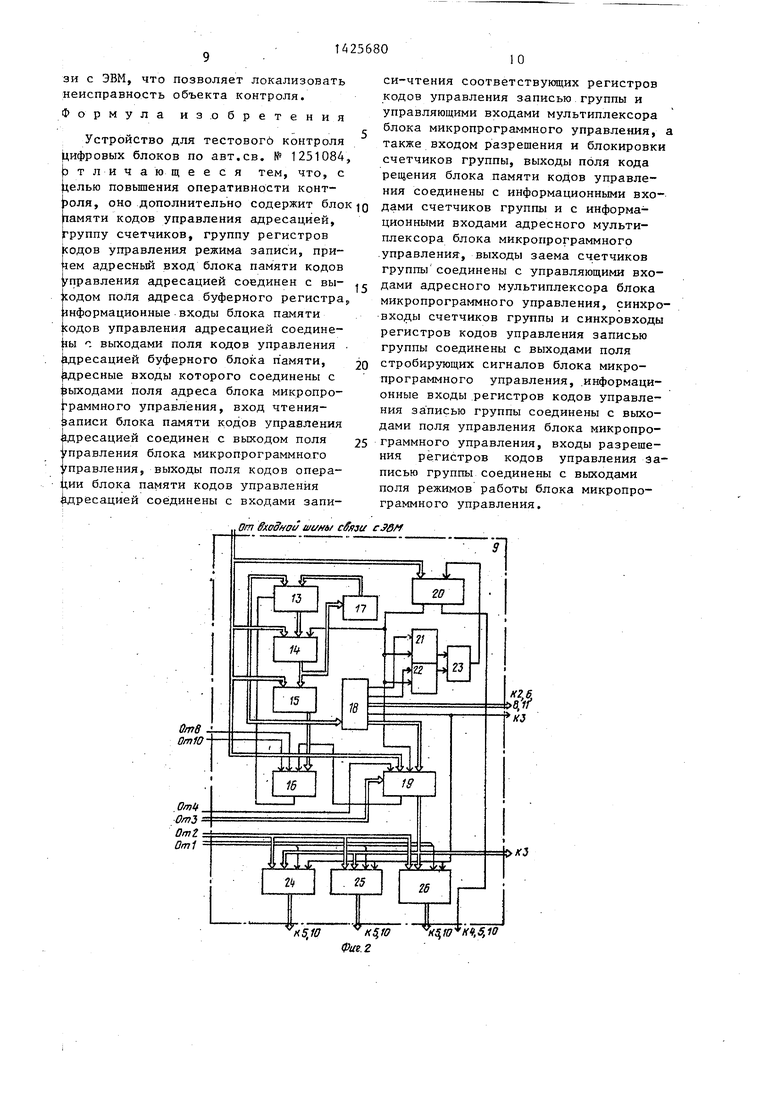

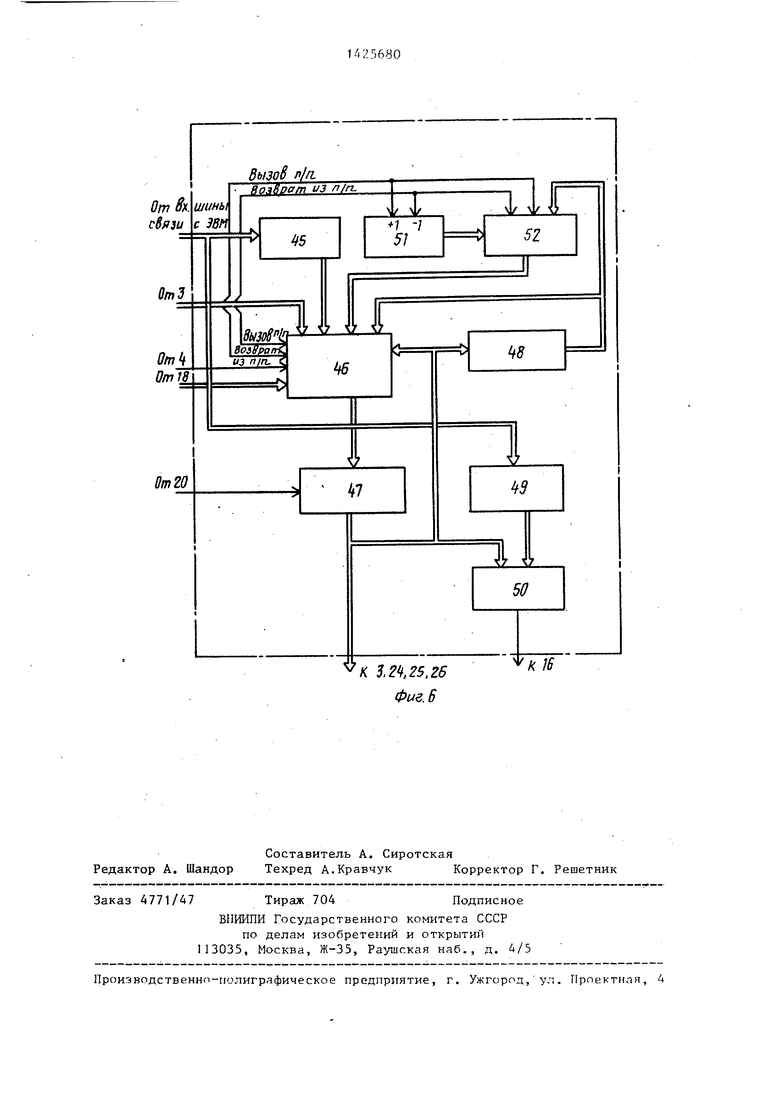

Блок 9 микропрограммного управления (фиг. 2) содержит модификатор адреса, состоящий из коммутатора 13, программного регистра 14, блок 15 памяти микрокоманд, мультиплексора 16, шифратора 17, дешифратора 18, адрес- ного мультиплексора 19-, блока 20 синхронизации, триггеров 21 и 22, элемента КПИ 23, а также блок 3 содержит блок 24 памяти масок каналов, блок 25 памяти тестовых наборов, блок 26 па-

ляции сложных программ контроля и занесении их в канальный блок памяти занимать меньший ее объем. Так как производите.тгьность устройства контроля с использованием канальной памяти определяется в основном временем загрузки этой памяти от внешних устройств, количество перегрузок уменьшается примерно в три раза. 6 ил.

мяти кодов управления коммутаторов входов-выходов.

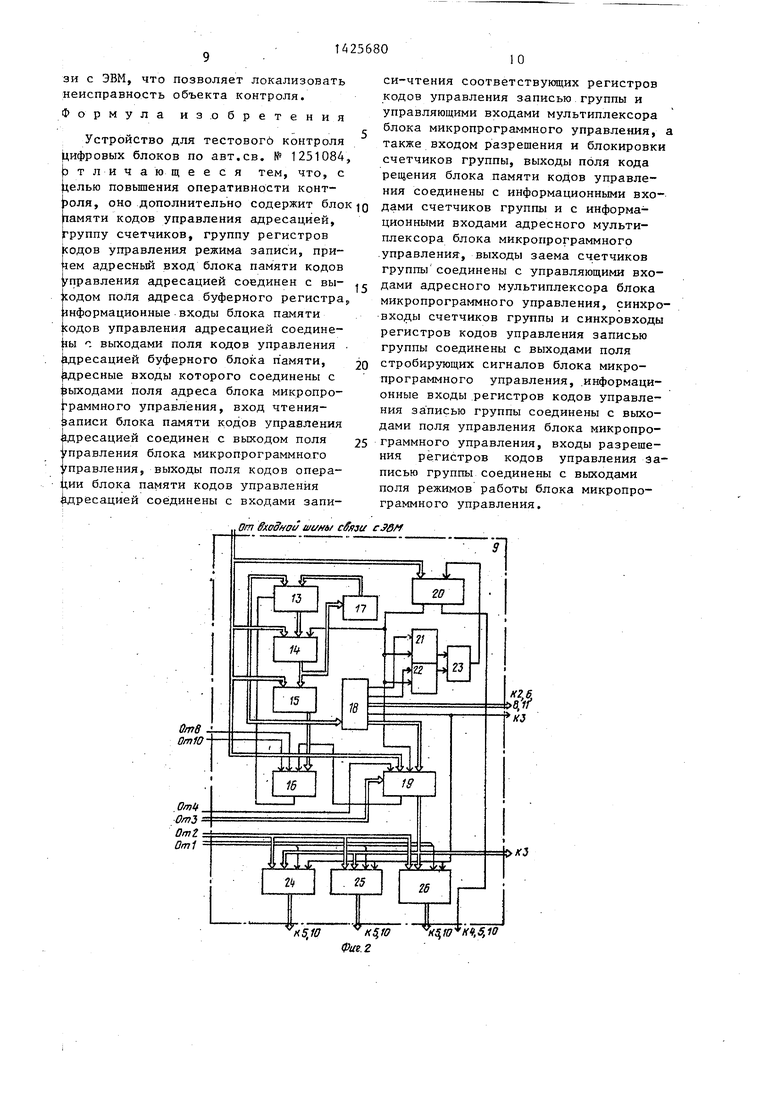

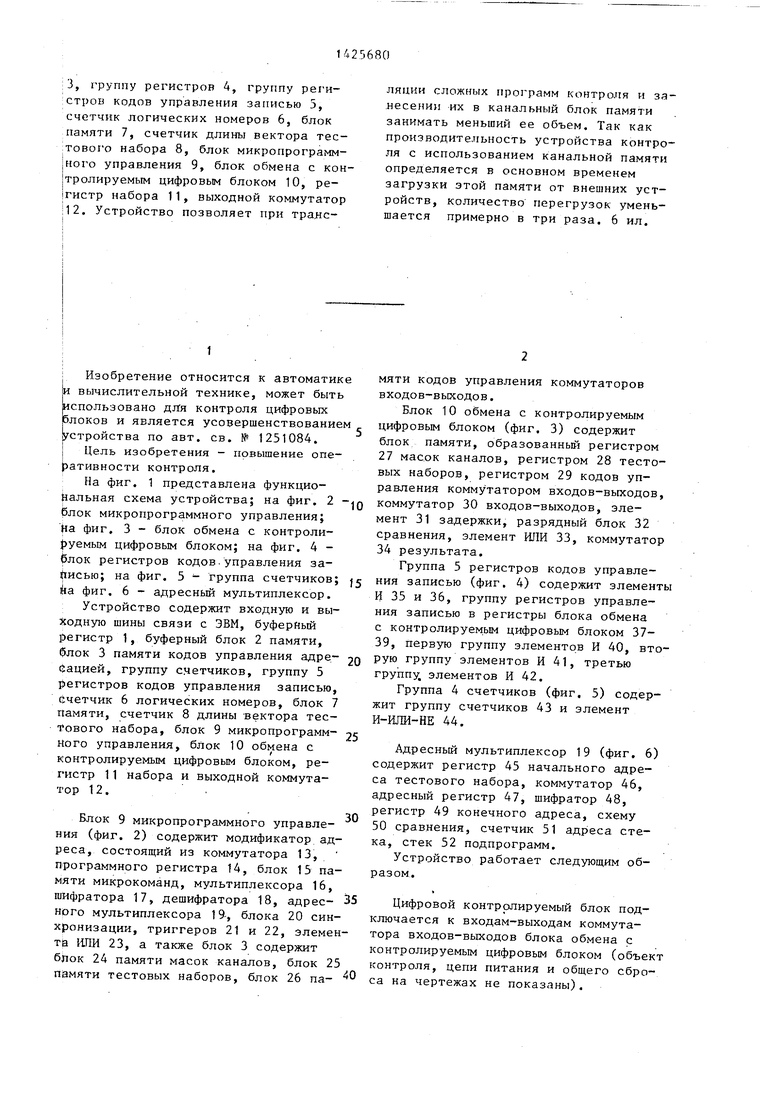

Блок 10 обмена с контролируемым цифровым блоком (фиг, 3) содержит блок памяти, образованный регистром 27 масок каналов, регистром 28 тестовых наборов, регистром 29 кодов управления коммутатором входов-выходов, коммутатор 30 входов-выходов, элемент 31 задержки, разрядный блок 32 сравнения, элемент ИЛИ 33, коммутатор 34 результата.

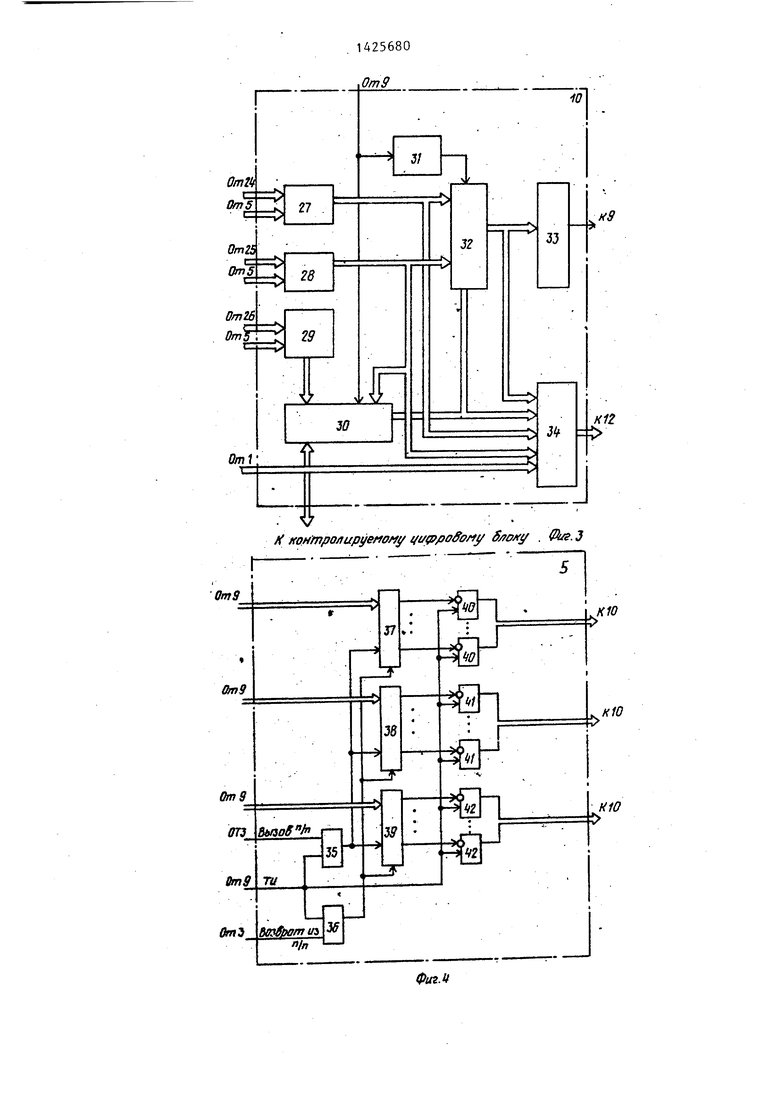

Группа 5 регистров кодов управления записью (фиг, 4) содержит элементы И 35 и 36, группу регистров управления записью в регистры блока обмена с контролируемым цифровым блоком 37- 39, Первую группу элементов И 40, вторую группу элементов И 41, третью группу, элементов И 42,

Группа 4 счетчиков (фиг, 5) содержит группу счетчиков 43 и элемент И-ИЛИ-НЕ 44,

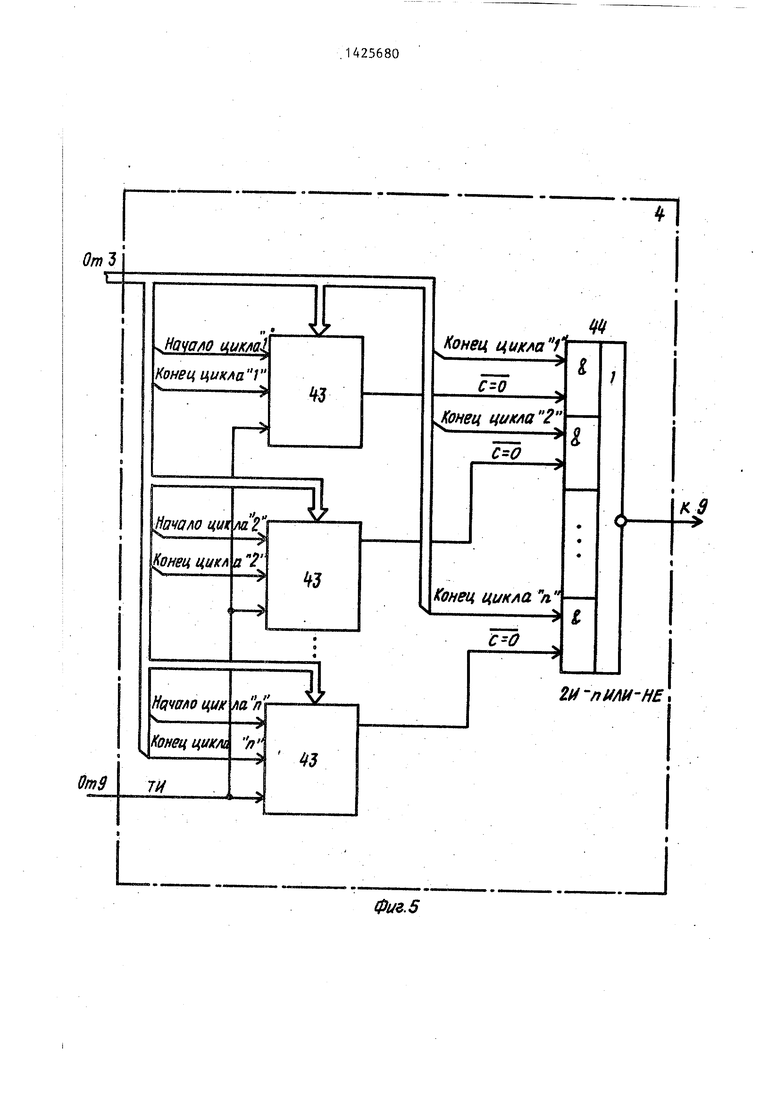

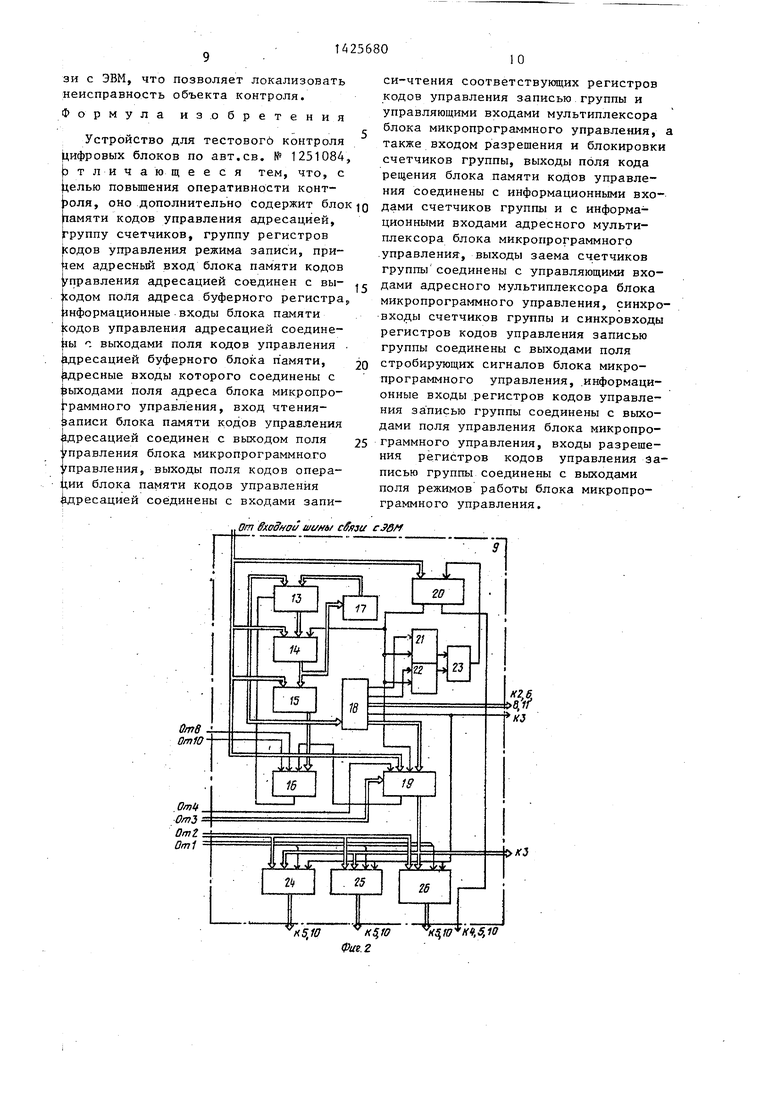

Адресный мультиплексор 19 (фиг, 6) содержит регистр 45 начального адреса тестового набора, коммутатор 46, адресный регистр 47, шифратор 48, регистр 49 конечного адреса, схему 50 сравнения, счетчик 51 адреса стека, стек 52 подпрограмм.

Устройство работает следующим образом.

Цифровой контролируемый блок подключается к входам-выходам коммутатора входов-выходов блока обмена с контролируемым цифровым блоком (объект контроля, цепи питания и общего сброса на чертежах не показаны),

В тесте содержится таблица соответствия логических номеров контролируемого цифрового блока физическим контактам его выходных разъемов, а также таблица соответствия логически номеров физическим номерам разрядов данных блока памяти управления адресацией. В блок 7 памяти по входной шине связи с ЭВМ записываются физические номера контактов контролируемого цифрового блока и физические номера разрядов данных блока памяти управления адресацией, соответствующие логическим номерам.

Запись информации в блок 7 памяти осуществляется следующ11м образом. Код логического номера контакта контролируемого цифрового блока или разряда данных блока памяти управления адресацией по входной шине связи с ЭВМ заносится в счетчик 6 логических номеров.

По адресу на выходе счетчика 6 логических номеров в блок 7 памяти с шины связи с ЭВМ заносится код физического адреса контакта контролируемого блока или физический номер разрда данных блока памяти управления адресацией.

По входной шине связи с ЭВМ в бло 9 микропрограммного управления заносятся, микропрограммы работы устройства. Адрес микрокоманд заносится в

При этом по микрокоманде блока 9 микропрограммного управления включается триггер 21 и через элемент ИЛИ 23 осуществляется блокировка тактовых сигналов, поступающих с выхода

1 в регистр 11 набора заносится информация нового значения теста, и

40

буферньш регистр 1, коды микрокоманд-,,

в блок 15 памяти микрокоманд, началь- блока 20 синхронизации. После изме- ный адрес теста - в регистр 45 началь- нения содержимого буферного регистра ного адреса тестового набора, а конечный адрес заносится в регистр 49 конечного адреса тестового набора, коды частоты функционального контроля и временного положения строба контроля, обеспечивающего прием информации с контролируемого цифрового блока, заносятся в блок 20 синхронизации.

В тестовом наборе, необходимом для каждого такта контроля, содержатся входные воздействия и эталонные реакции, коды маскирования каналов цифрового блока, коды управления коммутато- ром входов-выходов, а также признаки

процесс записи повторяется.

Таким образом,в буферный блок 2 памяти заносятся данные, необходимые для одного такта контроля. Запись информации буферного блока 2 памяти в дс блоки 3, 24, 25, 26 памяти осуществляется следующим образом.

Код выборки устройства заносится в буферный регистр 1, информация с выходов буферного блока памяти пода- :д ется на информационные входы блоков 3, 24, 25, 26 памяти. В регистр 45 начального адреса тестового набора заносится код начального адреса теста. В программный регистр 14 заносится адрес подпрограммы записи информации в блоки 3, 24, 25, 26 памяти. По микрокоманде, поступающей с выхода дешифратора 18, осуществляется запись информации из буферного

для организации динамических подпрограмм и циклов.

Вначале тестовый набор заносится в буферный блок 2 памяти следующим образом,

В буферный регистр 1 заносится код выбранного запоминающего устройства.

0

5

,

5 Q

0

В счетчик 6 логических номеров заносится начальный логический номер контакта цифрового контролируемого блока или разряда данных блока памяти управления адресацией. В счетчик 8 длины векторов заносится код длины группы шин, которым соответствует данная тестовая последовательность.

Тестовый набор заносится в регистр 11 набора. Код информации блока 7 памяти выбирает информационный разряд буферного блока 2 памяти, в который записывается код информации старшего разряда регистра 11 набора. Запись осуществляется по микрокоманде, фор- мируемой дешифратором 18. По микрокоманде блока модификации адреса увеличивается на единицу значение счетчика 6 логических номеров и уменьшается на единицу состояние счетчика 8 длины векторов тестового набора, а также осуществляется сдвиг влево информации в регистре 11 набора. Процесс записи, информации выполняется по новому информационному разряду буферного блока 2 памяти. Приведенные операции повторяются до тех пор, пока содержимое счетчика длины векторов не станет равным нулю.

При этом по микрокоманде блока 9 микропрограммного управления включается триггер 21 и через элемент ИЛИ 23 осуществляется блокировка тактовых сигналов, поступающих с выхода

,,

блока 20 синхронизации. После изме- нения содержимого буферного регистра 1 в регистр 11 набора заносится информация нового значения теста, и

блока 20 синхронизации. После изме- нения содержимого буферного регистра

0

блока 20 синхронизации. После изме- нения содержимого буферного регистра

процесс записи повторяется.

Таким образом,в буферный блок 2 памяти заносятся данные, необходимые для одного такта контроля. Запись информации буферного блока 2 памяти в с блоки 3, 24, 25, 26 памяти осуществляется следующим образом.

Код выборки устройства заносится в буферный регистр 1, информация с выходов буферного блока памяти пода- :д ется на информационные входы блоков 3, 24, 25, 26 памяти. В регистр 45 начального адреса тестового набора заносится код начального адреса теста. В программный регистр 14 заносится адрес подпрограммы записи информации в блоки 3, 24, 25, 26 памяти. По микрокоманде, поступающей с выхода дешифратора 18, осуществляется запись информации из буферного

5

10

20

25

блока 2 памяти в выбранный блок памяти. Операции повторяются для всех типов устройств, при этом в буферный регистр 1 предварительно заносятся коды выборки соответствуюпщх блоков памяти устройства.

После перезаписи информации из буферного блока 2 памяти в блоки 3, 24, 25, 26 памяти в буферньй блок 2 памяти заносятся только изменения в тестовой последовательности последую- 1цего такта,

После заполнения информацией бло- ков 3, 24, 25, 26 в регистр 49 ко- нечного адреса тестовой последоваельности заносится код конечного ад jpeca,

I В программный регистр 14 заносится |начальный адрес программы выдачи |Тестов,

i Затем запускается блок 20 син- |хронизации, который обеспечивает вы- рачу тактовых импульсов, поступающих на входы регистров блока 9 микропро- граммного управления. Кроме того, Ьлок 20 синхронизации вьщает строби- сигнал, обеспечивающий прием {информации с выходов контролируемого Цифрового блока. По входной шине свя- и с ЭВМ регистры 37-39 группы. 5 ре- |гистров кодов управления записью устанавливаются в состояние, обеспечивающее прохождение через группы эле- :| ентов И 40-42 тактовых сигналов за- Циси на синхронизирующие входы регистров 27-29 блока обмена с контроли- руемым цифровым блоком 10.

По микрокоманде блока 9 микропро- t paMMHoro управления код начального адреса из регистра 45 начального адреса тестового набора заносится в регистр .47 адреса тестовых воздействий. Выбранная по данному адресу информация из блоков 24-26 заносится в Соответствующие регистры 27-29 блока памяти, а из блока 3 поступает на входы группы 4 счетчиков и входы адресного мультиплексора 19.

Рассмотрим процесс организации динамических подпрограмм при выдаче , 50 тестовых воздействий на входы контролируемого цифрового блока.

При параллельной выдаче тестовых . воздействий из блоков 24-26 памяти ма входы контролируемого цифрового блока с любого адреса вьщачи возможно ветвление на подпрограмму, находящуюся в этих же блоках памяти.

5

30

35

40

45

0

5

0

Обычно при выполнении подпрограммы количество задействованных контактов цифрового блока гораздо меньше, чем при выполнении основной программы. Поэтому состояния, полученные после выполнения фрагмента основной программы для контактов, на задействованных в подпрограмме, необходимо, сохранить.

В связи с этим подпрограмма оформляется таким образом, что ее первая строка является входной информацией для группы 5 регистров в блок памя- ти, образованный регистрами 27-29.

При появлении признака Вызов подпрограммы на управляющем входе адресного мультиплексора 19 блока 9 микропрограммного управления коммутатор 46 подключает к адресному регистру 47 информационные шины данных блока 3 памяти управления адресацией.

По синхросигналу, поступающему от блока 20 синхронизации в адресный регистр 47, записьшается адрес перехода на подпрограмму.

Считываемая по этому адресу информация из блоков 24-26 памяти по сигналу, формируемому элементом И 35, заносится в регистры 37-39. Одновременно в стек 52 подпрограмм по адре- су, определяемому счетчиком 51 адреса стека, заносится адрес возврата из подпрограммы. Адрес возврата формируется при помощи шифратора 48 путем сложения единицы с адресом блока.24-26 памяти, на котором произошло обращение к подпрограмме.

Кроме того, по сигналу Вызов подпрограммы осуществляется продвижение счетчика 51 адреса стека на единицу.

После выполнения подпрограммы на управляющий вход адресного мультиплексора 19 блока 9 микропрограммного управления поступает признак Возврат из подпрограммы. Коммутатор 46 подключает к входам адресного регистра выход стека 52 подпрограмм.

По.синхросигналу, поступающему от блока 20 синхронизации, в адресный регистр 47 записывается адрес возврата из подпрограммы. Одновременно с этим по принципу Возврат из подпрограммы элемент И 36 формирует сигнал сброса, которьй устанавливает регистры 37-39 блока регистров управления записью в состояние, разрешающее прохождение сигналов побитной

0

5

0

5

10

15

25

записи через группы элементов И 40- 42 на входы регистров 27-29 блока обмена с контролируемым цифровым блоком 10.

Происходит также вычитание единицы от значения счетчика 51 адреса стека.

Применение стека 52 подпрограмм и счетчика 51 адреса стека позволяет реализовать вложенные подпрограммы. Количество вложений определяется емкостью стека 52 подпрограмм.

Организация динамических циклов и вложенных динамических циклов происходит следующим образом.

При поступлении признака Начало цикла от разрядов кода операции блока 3 памяти на входы группы 4 счетчиков по синхросигналу, поступающему 20 от блока 20 синхронизации блока 9 микропрограммного управления 9 осуществляется запись значения переменной цикла в один из счетчиков группы 43 от информационных разрядов данных блока 3.

При поступлении признака Конец цикла на входы группы 4 счетчиков по синхросигналу, поступающему от блока 20 синхронизации блока 9 микропрограммного управления, формируется сигнал вычитания единицы от значения счетчика переменной цикла.

Кроме того, по признаку Конец цикла при помощи элемента .И-ИЛИ-НЕ 44 осуществляется проверка содержимого счетчика переменной цикла на нуль.

При неравенстве нулю содержимого счетчика переменной цикла сигнал, поступающий с выхода элемента И-ИЛИ-НЕ .Q 44 на управляющий вход адресного муль- .типлексора 19 блока 9 микропрограммного управления, при помощи коммутатора 46 подключает к входам адресного ;регистра информационные выходы дан- ,ных блока 3 памяти управления адреса цией.

По синхросигналу, поступающему от блока 20 синхронизации, в адресный регистр 47 заносится адрес, на едини30

35

,-45

счетчиков из группы 4. Количеств вложений определяется количество счетчиков в группе.

Процесс формирования теста пр жается до тех пор, пока содержим адресного регистра 47 не станет но коду регистра 49 конечного ад тестового набора.

Сигнал с выхода схемы 50 срав ния поступает на управляющий вхо мультиплексора 16, что обеспечив перевод адресного регистра 47 в жим хранения информации, а новая тестовая последовательность не ф мируется. Результаты контроля с ходов разрядного блока 32 сравне через элемент 11ПИ 33 поступают н управляющий вход мультиплексора что обеспечивает фиксирование ре тата Конец проверки или Брак триггерах 21 и 22 и выдачу сообщ на выходную шину связи с ЭВМ. На дикацию можно передавать данные, ступающие с выходов коммутатора и выходного коммутатора 12.

Для выдачи данных на индикацию необходимо в счетчик 6 логических номеров занести начальный логичес номер контакта объекта контроля, счетчик 8 длины векторов - код дл вектора.

В программный регистр 14 от вх ной шины связи с ЭВМ заносится на чальный адрес микропрограммы выда результата контроля.

В буферный регистр 1 заносится код выбираемого регистра, который переключает необходимое направлен коммутатора 34 результата.

Код с выхода блока 7 памяти вы рает необходимый информационный р ряд при помощи выходного коммутат 12. .По микрокоманде блока 9 микро программного управления в регистр набора заносится информация с вых да выходного коммутатора 12.

Затем содержимое счетчика 6 ло ческих номеров увеличивается на е ницу, а содержимое счетчика 8 дли

цу больший адреса, на котором проис- 50 векторов уменьшается на единицу.

ходит занесение значения переменной цикла в один из группы 4 счетчиков.

Если содержимое счетчика равно нулю, при помощи шифратора 48 к содержимому адресного регистра 47 добавляется единица. I

При организации вложенных динамических циклов используется несколько

10

15

25

20

.Q -

30

35

45

счетчиков из группы 4. Количество вложений определяется количеством счетчиков в группе.

Процесс формирования теста продолжается до тех пор, пока содержимое адресного регистра 47 не станет равно коду регистра 49 конечного адреса тестового набора.

Сигнал с выхода схемы 50 сравнения поступает на управляющий вход мультиплексора 16, что обеспечивает перевод адресного регистра 47 в режим хранения информации, а новая тестовая последовательность не формируется. Результаты контроля с выходов разрядного блока 32 сравнения через элемент 11ПИ 33 поступают на управляющий вход мультиплексора 16, что обеспечивает фиксирование результата Конец проверки или Брак в триггерах 21 и 22 и выдачу сообщения на выходную шину связи с ЭВМ. На индикацию можно передавать данные, поступающие с выходов коммутатора 34 и выходного коммутатора 12.

Для выдачи данных на индикацию необходимо в счетчик 6 логических номеров занести начальный логический номер контакта объекта контроля, а в счетчик 8 длины векторов - код длины вектора.

В программный регистр 14 от входной шины связи с ЭВМ заносится начальный адрес микропрограммы выдачи результата контроля.

В буферный регистр 1 заносится код выбираемого регистра, который переключает необходимое направление коммутатора 34 результата.

Код с выхода блока 7 памяти выбирает необходимый информационный разряд при помощи выходного коммутатора 12. .По микрокоманде блока 9 микропрограммного управления в регистр 11 набора заносится информация с выхода выходного коммутатора 12.

Затем содержимое счетчика 6 логи- ческих номеров увеличивается на единицу, а содержимое счетчика 8 длины

50 векторов уменьшается на единицу.

что обеспечивает коммутацию информации нового логического номера. Процесс заполнения регистра 11 набора продолжается до тех пор, пока содер- жимое счетчика 8 длины векторов не станет равным нулю.

Информация с выходов регистра 11 набора вьщается на выходную шину связи с ЭВМ, что позволяет локализовать неисправность объекта контроля.

Формула из.обретения

Устройство для тестового контроля Цифровых блоков по авт.св. № 1251084 |этличающееся тем, что, с елью повышения оперативности конт- Ьоля, оно дополнительно содержит бло Памяти кодов управления адресацией, руппу счетчиков, группу регистров |кодов управления режима записи, при- keM адресньш вход блока памяти кодов управления адресацией соединен с вы- кодом поля адреса буферного регистра нфopмaциoнныe входы блока памяти содов управления адресацией соедине- йы с выходами поля кодов управления ресацией буферного блока п амяти, ресные входы которого соединены с выходами поля адреса блока микропро- jr paMMHoro управления, вход чтения- Записи блока памяти кодов управления ресацией соединен с выходом поля | правления блока микропрограммного управления, выходы поля кодов опера- |;ии блока памяти кодов управления ресацией соединены с входами запи

от ej cSffotJ laifffii/

К5.Ю Ю K5,,S,10 Фиг. 2

си-чтения соответствующих регистров кодов управления записью группы и управляющими входами мультиплексора блока микропрограммного управления, а также входом разрешения и блокировки счетчиков группы, выходы поля кода рещения блока памяти кодов управления соединены с информационными входами счетчиков группы и с информационными входами адресного мультиплексора блока микропрограммного .управления, выходы заема счетчиков группы соединены с управляющими входами адресного мультиплексора блока микропрограммного управления, синхро- входы счетчиков группы и синхровходы регистров кодов управления записью группы соединены с выходами поля стробирующих сигналов блока микропрограммного управления, .информационные входы регистров кодов управления записью группы соединены с выходами поля управления блока микропрограммного управления, входы разрешения регистров кодов управления записью группы соединены с выходами поля режимов работы блока микропрограммного управления.

к контро/iupyefiofty i/i/p/joffofiy S/to/fy . Фиг. 3

Qm9

ОтЗ

ОТЗ

ВызоУ

OmS

ги

втЗ

boyfyama In

X

37

i

кю

38

0

f(fO

WJ

V

3ff

Я10

1

J

Фиг. 5

О т 8. связи

ОтЗ

От От 18

О т го

К 3.2,25.26 Фие.6

Н16

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-01-07—Подача