1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для диагностики цифровых блоков,,

Цель изобретения - расширения класса решаемых задач за счет обеспечения процесса формирования тестов параллельно процессу контроля.

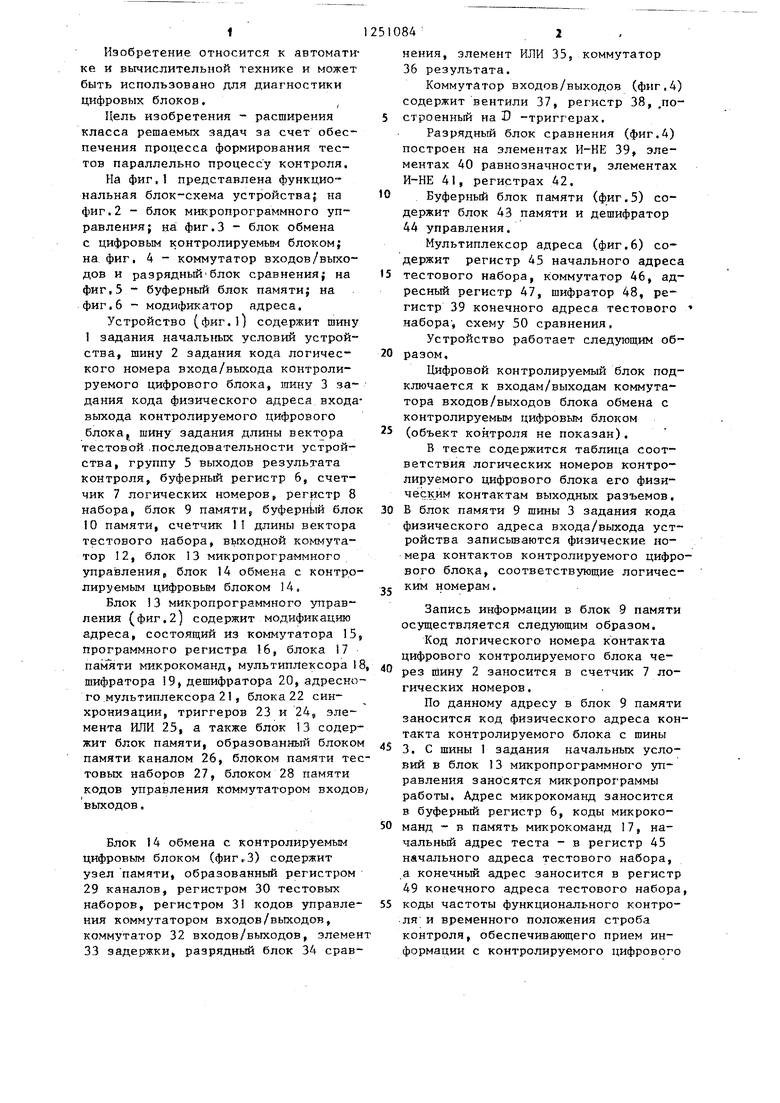

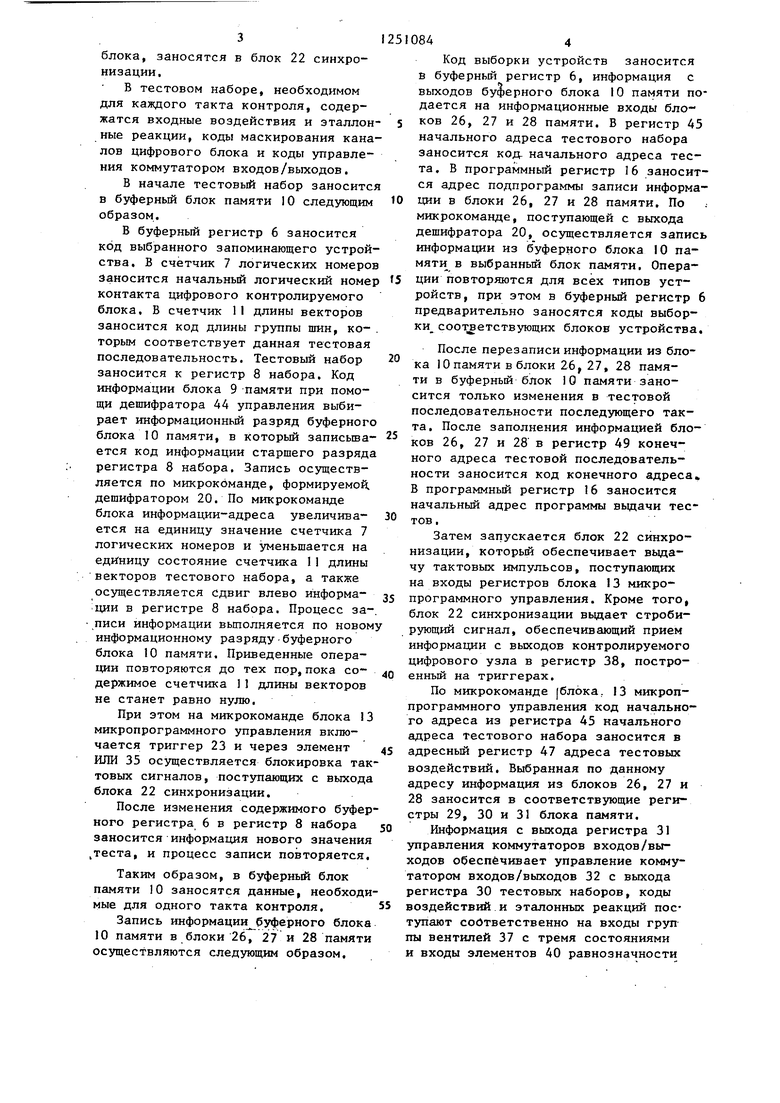

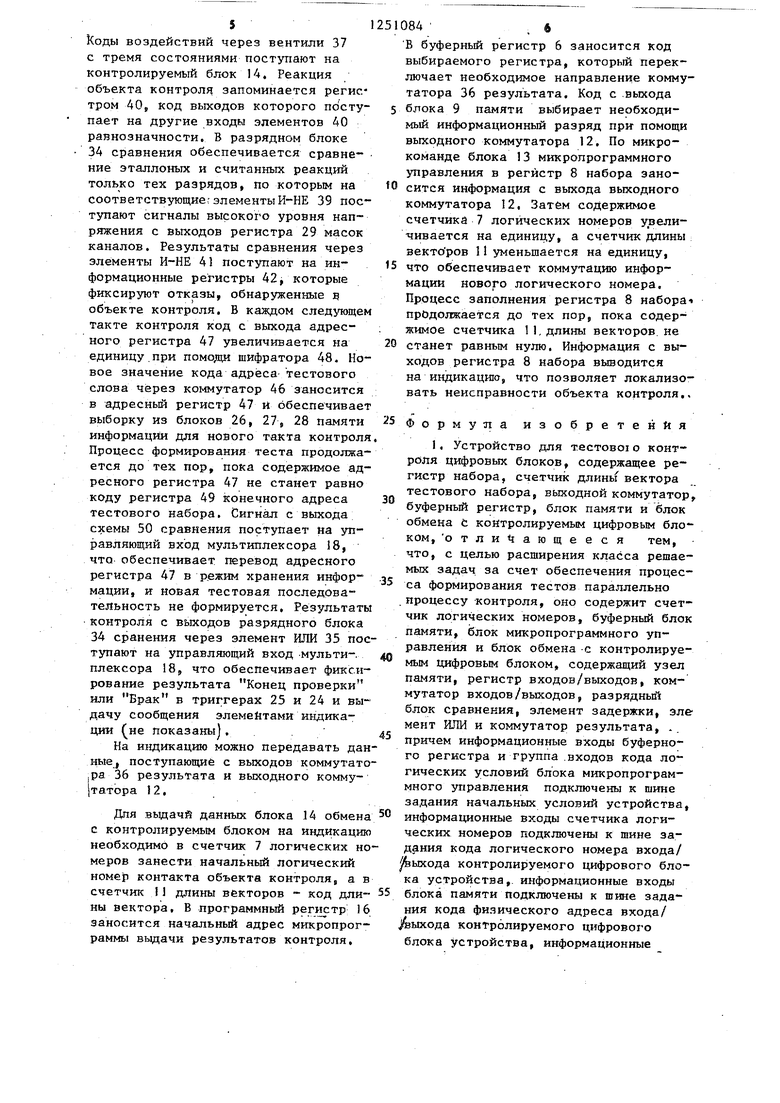

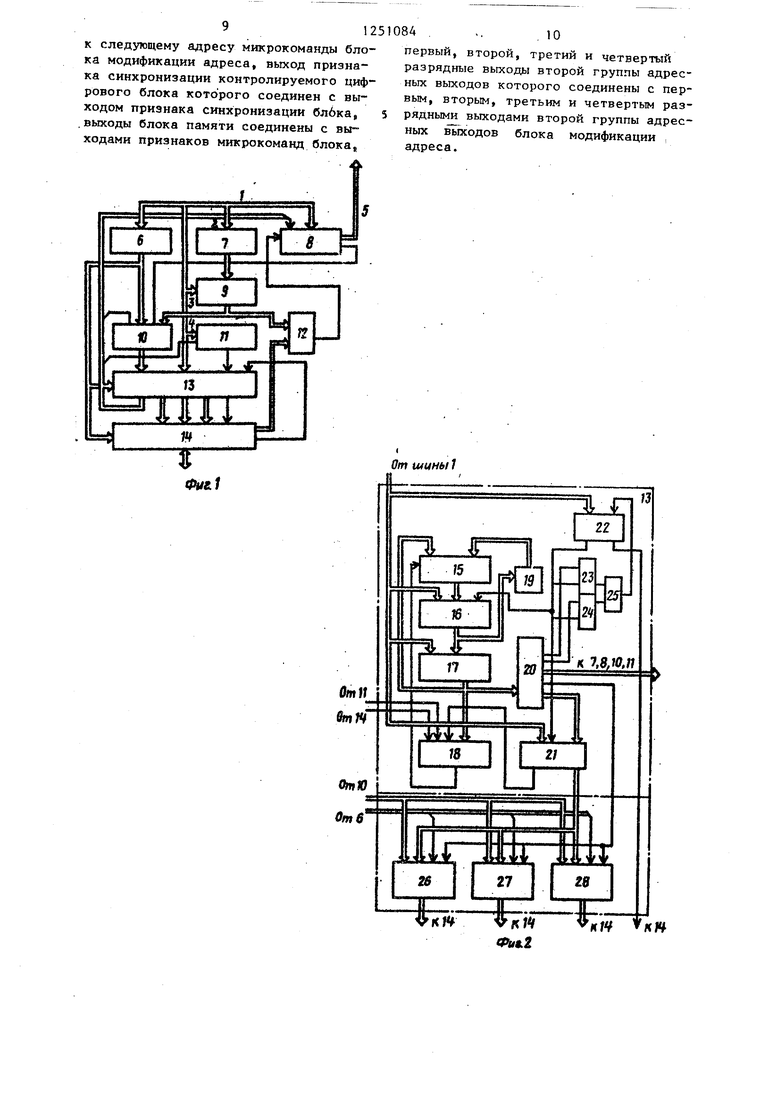

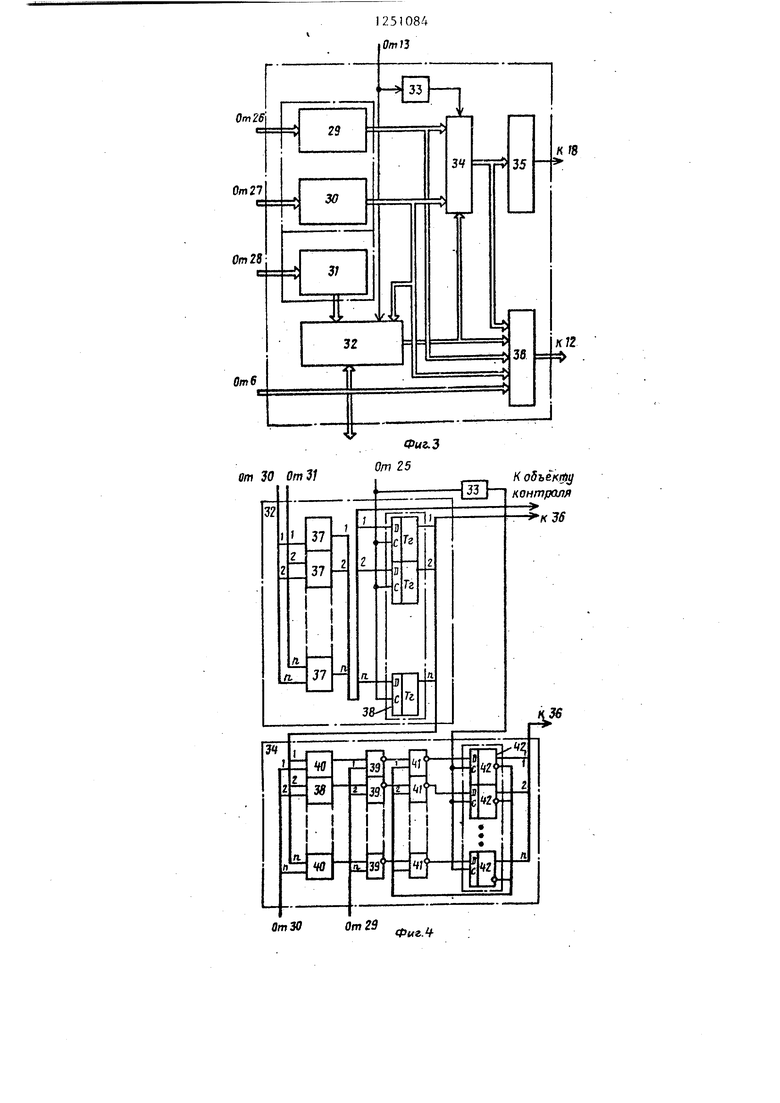

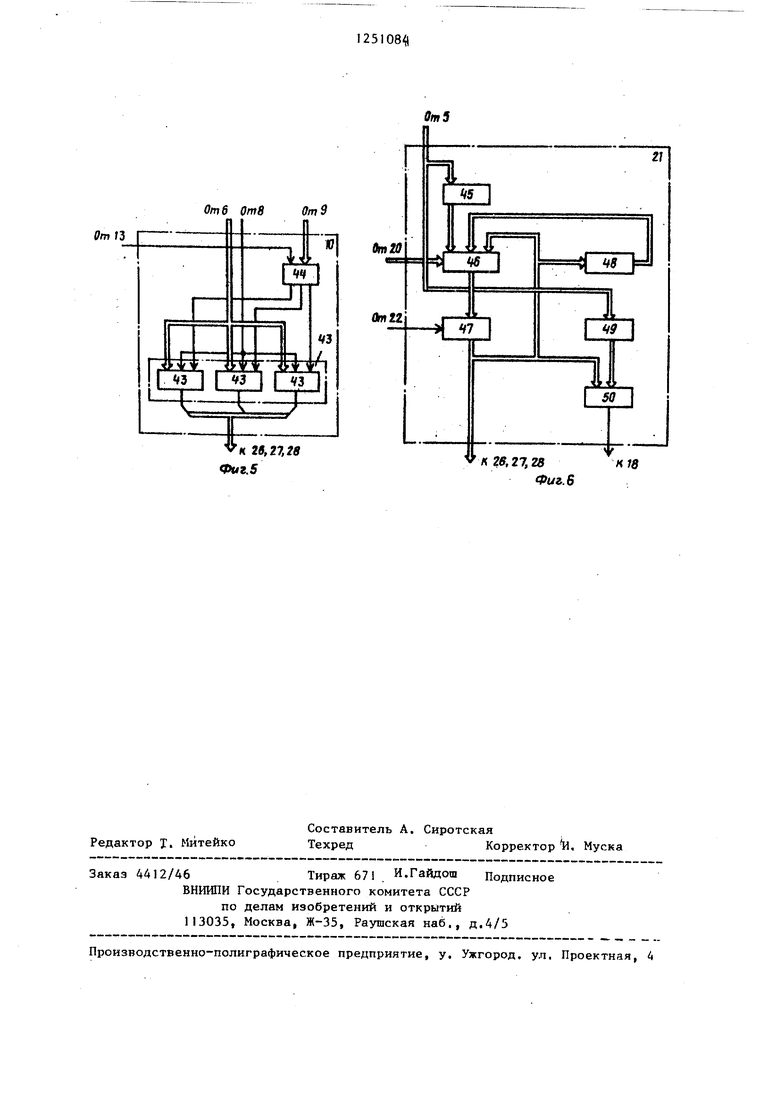

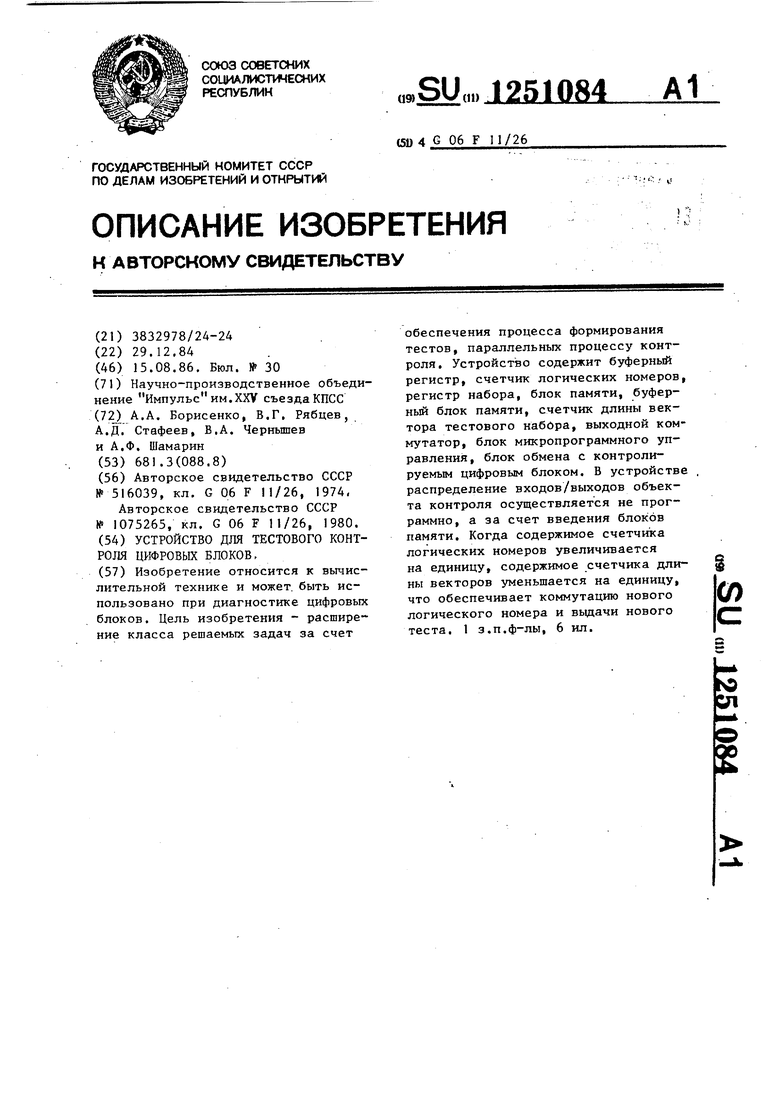

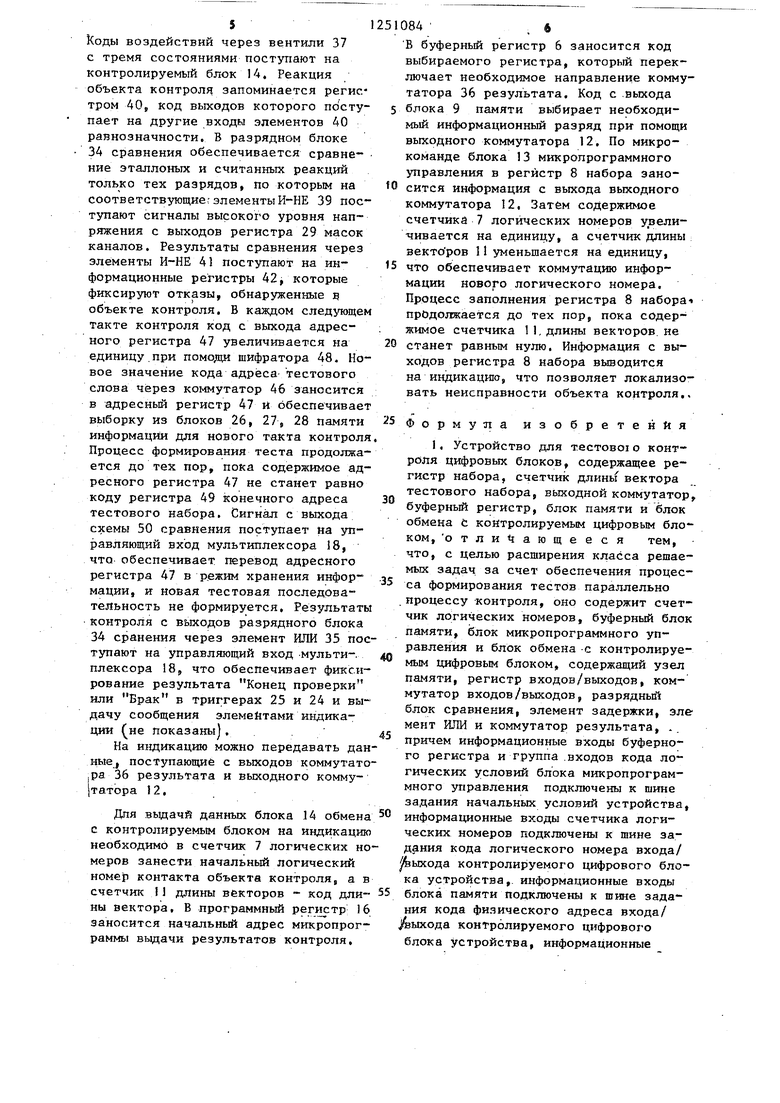

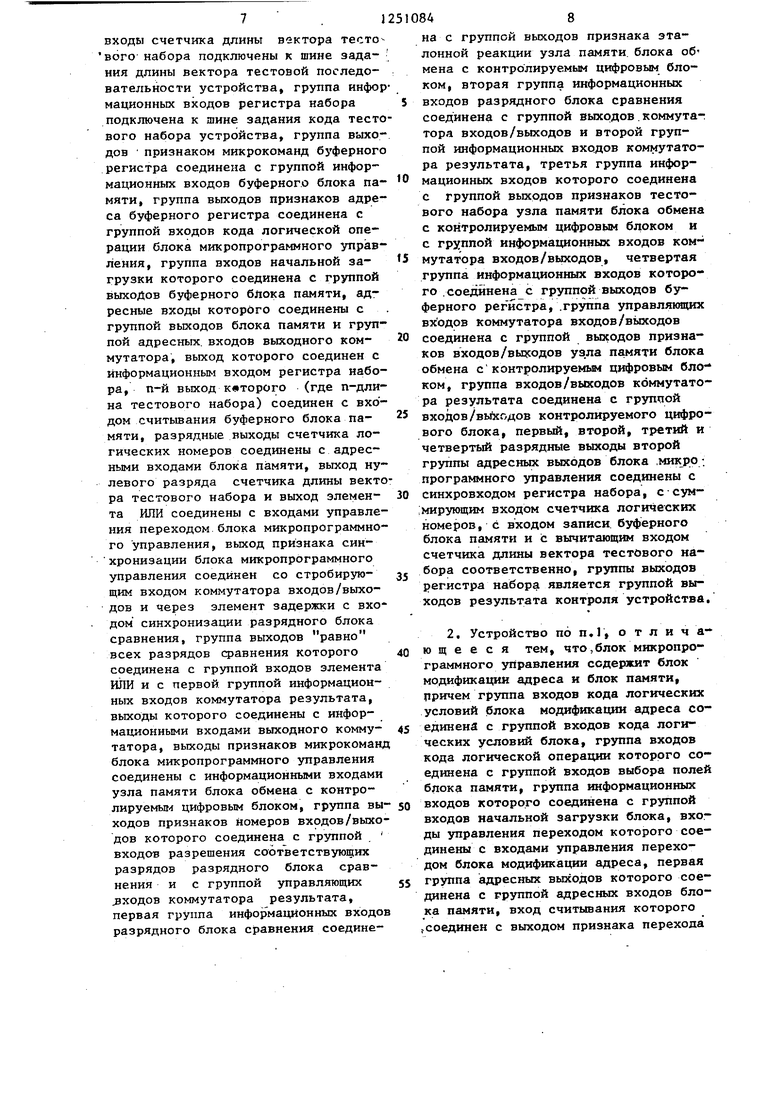

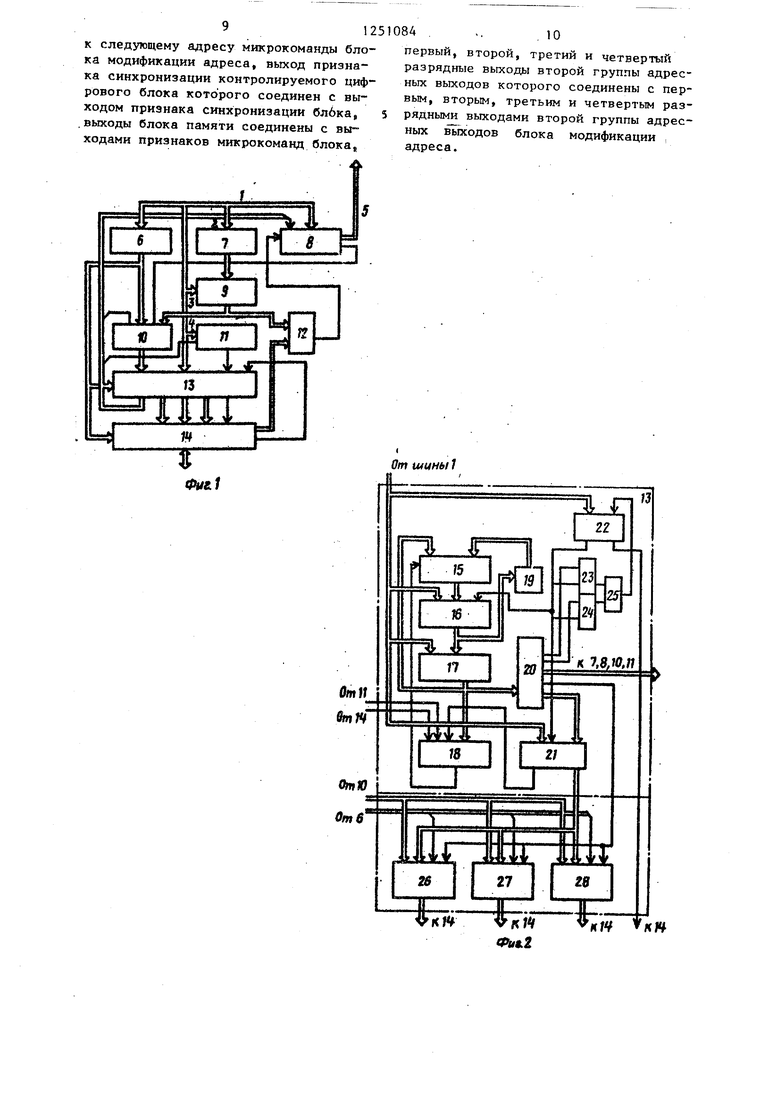

На фиг,1 представлена функциональная блок-схема устройства} на фиг.2 - блок микропрограммного управления; на: фиг.З - блок обмена с цифровым контролируемым блоком; на фиг. 4 - коммутатор входов/выходов и разрядный блок сравнения; на фиг.5 - буферный блок памяти; на фиг.6 - модификатор адреса.

Устройство (фиг,О содержит шину 1 задания началы ых условий устройства, шину 2 задания кода логического номера входа/выхода контролируемого цифрового блока, шину 3 задания кода физического адреса входа выхода контролируемого цифрового блокаJ шину задания длины вектора тестовой .последовательности устройства, группу 5 выходов результата контроля, буферный регистр 6, счетчик 7 логических номеров, регистр 8 набора, блок 9 памяти буферн11Й бло 10 памяти, счетчик И длины вектора тестового набора, вьгходной коммутатор 12, блок 13 микропрограммного упра1вления, блок 14 обмена с контролируемым цифровьм блоком 14,

Блок 13 микропрограммного управления (фиг.2) содержит модификацию адреса, состоящий из коммутатора 15 программного регистра 16, блока 17 памяти микрокоманд, мультиплексора шифратора 19, дешифратора 20, адресного мультиплексора 21, блока 22 синхронизации, триггеров 23 и 24, элемента ИЛИ 25, а также блок 13 содержит блок памяти, образованный блоко памяти каналом 26, блоком памяти тетовых наборов 27, блоком 28 памяти кодов управления коммутатором входо выходов,

Блок 14 обмена с контролируемым цифровым блоком (фиГгЗ) содержит узел памяти, образованньй регистром 29 каналов, регистром 30 тестовых наборов, регистром 3 кодов управления коммутатором входов/выходов, коммутатор 32 входов/вь ходов, элемент 33 задержки, разрядный блок 34 срав

нения, элемент ИЛИ 35, коммутатор 36 результата.

Коммутатор входов/выходов (фиг,4) содержит вентили 37, регистр 38, ,по- строенный на -триггерах.

Разрядный блок сравнения (фиг.4) построен на элементах И-НЕ 39, элементах 40 равнозначности, элементах ИНЕ 41, регистрах 42.

Буферный блок памяти (фиг.З) содержит блок 43 памяти и дешифратор 44 управления.

Мультиплексор адреса (фиг.6) содержит регистр 45 начального адреса тестового набора, коммутатор 46, адресный регистр 47, шифратор 48, регистр 39 конечного адреса тестового набора , схему 50 сравнения,

Устройство работает следующим образом.

Цифровой контролируемый блок подключается к входам/выходам коммутатора входов/выходов блока обмена с контролируемьм цифровым блоком (объект контроля не показан).

В тесте содержится таблица соответствия логических номеров контролируемого цифрового блока его физическим контактам выходных разъемов. В блок памяти 9 шины 3 задания кода физического адреса входа/выхода устройства записываются физические номера контактов контролируемого цифрового блока, соответствующие логическим номерам.

Запись информации в блок 9 памяти осуществляется следующим образом.

Код логического номера контакта цифрового контролируемого блока через шину 2 заносится в счетчик 7 логических номеров.

По данному адресу в блок 9 памяти заносится код физического адреса контакта контролируемого блока с шины 3. С шины 1 задания начальных условий в блок 13 микропрограммного управления заносятся микропрограммы работы. Адрес микрокоманд заносится в буферный регистр 6, коды микрокоманд - в память микрокоманд 17, на- чальньй адрес теста - в регистр 45 начального адреса тестового набора, .а конечный адрес заносится в регистр 49 конечного адреса тестового набора, коды частоты функционального контроля и временного положения строба контроля, обеспечивающего прием информации с контролируемого цифрового

10

f5

20

блока, заносятся в блок 22 синхронизации.

В тестовом наборе, необходимом для каждого такта контроля, содержатся входные воздействия и эталлон- ные реакции, коды маскирования каналов цифрового блока и коды управления коммутатором входов/выходов.

В начале тестовый набор заносится в буферный блок памяти IО следующим образом,

В буферный регистр 6 заносится код выбранного запоминающего устройства. В счетчик 7 логических номеров заносится начальный логический номер контакта цифрового контролируемого блока. В счетчик II длины векторов заносится код длины группы шин, ко- . торым соответствует данная тестовая последовательность. Тестовый набор заносится к регистр 8 набора. Код информации блока 9 памяти при помощи дешифратора 44 управления выбирает информационный разряд буферного блока 10 памяти, в который записьша- 25 ется код информации старшего разряда регистра 8 набора. Запись осуществляется по микрокоманде, формируемой дешифратором 20. По микрокоманде блока информации-адреса увеличивается на единицу значение счетчика 7 логических номеров и уменьшается на единицу состояние счетчика 11 длины векторов тестового набора, а также осуществляется сдвиг влево информа- ции в регистре 8 набора. Процесс за- писи информации вьтолняется по новому информационному разряду-буферного блока 10 памяти. Приведенные операции повторяются до тех пор,пока содержимое счетчика 11 длины векторов не станет равно нулю.

При этом на микрокоманде блока I3 микропрограммного управления включается триггер 23 и через элемент ИЛИ 35 осуществляется блокировка тактовых сигналов, поступающих с выхода блока 22 синхронизации.

После изменения содержимого буферного регистра 6 в регистр 8 набора 50 заносится информация нового значения теста, и процесс записи повторяется.

Таким образом, в буферный блок памяти 10 заносятся данные, необходимые для одного такта контроля. 55

Запись информации буферного блока 10 памяти в блоки 26, 27 и 28 памяти осуществляются следующим образом.

30

35

40

45

10

f5

20

25

0

5

510844

Код выборки устройств заносится в буферный регистр 6, информация с выходов буферного блока 10 памяти подается на информационные входы блоков 26, 27 и 28 памяти. В регистр 45 начального адреса тестового набора заносится КОД- начального адреса теста, В программный регистр 16 заносится адрес подпрограммы записи информации в блоки 26, 27 и 28 памяти. По микрокоманде, поступающей с выхода дешифратора 20, осуществляется запись информации из буферного блока IО памяти в выбранный блок памяти. Операции повторяются для всех типов устройств, при этом в буферный регистр 6 предварительно заносятся коды выбор- ки соответствующих блоков устройства.

После перезаписи информации из блока Юпамяти в блоки 26, 27, 28 памяти в буферный блок 10 памяти заносится только изменения в тестовой последовательности последующего такта. После заполнения информацией блоков 26, 27 и 28 в регистр 49 конечного адреса тестовой последовательности заносится код конечного адреса В программный регистр 16 заносится начальный адрес программы выдачи тестов .

Затем запускается блок 22 синхронизации, который обеспечивает вьща- чу тактовых импульсов, поступающих на входы регистров блока 13 микропрограммного управления. Кроме того, блок 22 синхронизации выдает строби- рующий сигнал, обеспечивающий прием информации с выходов контролируемого цифрового узла в регистр 38, построенный на триггерах.

По микрокоманде блока. 13 микроп- программного управления код начального адреса из регистра 45 начального адреса тестового набора заносится в адресный регистр 47 адреса тестовых воздействий. Выбранная по данному адресу информация из блоков 26, 27 и 28 заносится в соответствующие регистры 29, 30 и 31 блока памяти.

Информация с выхода регистра 31 управления коммутаторов входов/выходов обеспечивает управление коммутатором входов/выходов 32 с выхода регистра 30 тестовых наборов, коды воздействий и эталонных реакций поступают соответственно на входы груп пы вентилей 37 с тремя состояниями и входы элементов 40 равнозначности

30

35

0

5

51

Коды воздействий через вентили 37 с тремя состояниями поступают на контролируемый блок 1 А. Реакция объекта контроле запоминается регис тром 40, код выходов которого по сту- пает на другие входы элементов АО равнозначности. В разрядном блоке ЗА сравнения обеспечивается сравне- ние эталлоных и считанных реакций только тех разрядов, по которым на соответствующнег элементы И-НЕ 39 поступают сигналы высокого уровня напряжения с выходов регистра 29 масок каналов. Результаты сравнения через элементы И-НЕ 41 поступают на ин- формационные регистры 42, которые фиксируют отказы, обнаруженные я объекте контроля, В каждом следующем такте контроля код с выхода адрес- ного регистра 47 увеличивается на единицу.при помоги шифратора 48. Новое значение кода адреса тестового слова через коммутатор 46 заносится в адресный регистр 47 и обеспечивает выборку из блоков 26, 27, 28 памяти информации для нового такта контроля Процесс формирования теста продолжается до тех пор, пока содержимое адресного регистра 47 не станет равно коду регистра 49 конечного адреса тестового набора. Сигнал с выхода схемы 50 сравнения поступает на управляющий вход мультиплексора 18, что обеспечивает перевод адресного регистра 47 в р.ежим хранения инфор- мации, и новая тестовая последовательность не формируется. Результаты контроля с выходов разрядного блока ЗА сранения через элемент ИЛИ 35 поступают на управляющий вход-мульти-. плексора 18 что обеспечивает фиксирование результата Конец проверки или Брак в триггерах 25 и 24 и выдачу сообщения элемейтами индикации не показаны). .

На ивдикацию можно передавать данные, поступающие с выходов коммутатора 36 результата и выходного коммутатора 12,

Для вьздачй данных блока 14 обмена с контролируемым блоком на индикацию необходимо в счетчик 7 логических номеров занести начальный логический номер контакта объекта контроля, а в счетчик I длины векторов - код дли- ны вектора, В программный регистр 16 заносится начальный адрес микропрограммы выдачи результатов контроля.

084 .6

В буферный регистр 6 заносится код выбираемого регистра, который переключает необходимое направление коммутатора 36 результата. Код с .выхода блока 9 памяти выбирает необходимый информационный разряд при помощи выходного коммутатора 12, По микрокоманде блока 13 микропрограммного управления в регистр В набора заносится информация с выхода выходного коммутатора 12, Затем содержимое счетчика 7 логических номеров увеличивается на единицу, а счетчик длины векто ров 11 уменьшается на единицу, что обеспечивает коммутацию информации нового логического номера. Процесс заполнения регистра 8 набора- продолжается до тех пор, пока содержимое счетчика I1, длины векторов, не станет равным нулю. Информация с выходов регистра 8 набора выводится на индикацию, что позволяет локализовать неисправности объекта контроля,.

Формула изобретения

1. Устройство для тестово о контроля цифровых блоков, содержащее регистр набора, счетчик длиньГ вектора тестового набора, выходной коммутатор буферньй регистр, блок памяти и блок обмена С контролируемым цифровым блоком, отли 1ающееся тем, что, с целью расширения класса решаемых задач за счет обеспечения процесса формирования тестев параллельно

. процессу контроля, оно содержит счетчик логических номеров, буферный блок памяти, блок микропрограммного управления и блОк обмена -с контролируемым цифровым блоком, содержащий узел памяти, регистр входов/выходов, коммутатор входов/выходов, разрядньй блок сравнения, элемент задержки, эле мент ИЛИ и коммутатор результата, .. причем информационные входы буферного регистра и группа .входов кода логических условий блока микропрограммного управления подключены к шине задания начальных условий устройства, информахщонные входы счетчика логических номеров подключены к шине задания кода логического номера входа/

ыхода контролируемого цифрового блока устройства,- информационные входы блока памяти подключены к шине задания кода физического адреса входа/

.ыхода контролируемого цифрового блока устройства, информационные

входы счетчика длины вектора тесто вого набора подключены к шине зада- имя длины вектора тестовой последо- нательноети устройства, группа информационных входов регистра набора подключена к шине задания кода тестового набора устройства, группа выходов признаком микрокоманд буферного регистра соединена с группой информационных входов буферного блока па- мяти, группа выходов признаков адреса буферного регистра соединена с группой входов кода логической операции блока микропрограммного управления, группа входов начальной за- грузки которого соединена с группой выходов буферного бйока памяти, адресные входы которого соединены с группой выходов блока памяти и группой адресных, входов выходного ком- мутатора, выход которого соединен с информационным входом регистра набора, п-й выход к«торого (где п-дли- на тестового набора) соединен с входом считьшания буферного блока па- мяти, разрядные выходы счетчика логических номеров соединены с адресными входами блока памяти, выход нулевого разряда счетчика длины вектора тестового набора и выход элемен- та ИЛИ соединены с входами управления переходом блока микропрограммного управления, выход признака синхронизации блока микропрограммного управления соединен со стробирзто- щим входом коммутатора входов/выходов и через элемент задержки с входом синхронизации разрядного блока сравнения, группа выходов равно всех разрядов равнения которого соединена с группой входов элемента ИЛИ и с первой группой информационных входов коммутатора результата, выходы которого соединены с информационными входами выходного комму- татора, выходы признаков микрокоманд блока микропрограммного управления соединены с информационными входами узла памяти блока обмена с контролируемым цифровым блоком, группа вы- ходов признаков Номеров входов/выходов которого соединена с группой входов разрешения соответствующих разрядов разрядного блока сравнения и с группой управляющих уходов коммутатора результата, первая группа информационных входов разрядного блока сравнения соединена с группой выходов признака эталонной реакции узла памяти блока об мена с контролируемым цифровым блоком, вторая группа информационных входов разрядного блока сравнения соединена с группой выходов.коммутаг тора входов/выходов и второй группой информационных входов коммутатора результата, третья группа инфор- мациоиных входов которого соединена с группой выходов признаков тестового набора узла памяти блока обмена с контролируемым цифровым блоком и с группой информационных входов коммутатора входон/выходов, четвертая группа информационных входов которого .соединена с группой выходов буферного регистра, .группа управлякацих вх одрв коммутатора входов/выходов соединена с группой выходов признаков входов/выходов узла памяти блока обмена с контролируемым цифровым блоком, группа входов/выходов коммутатора результата соединена с группой входов/выводов контролируемого цифрового блока, первый, второй, третий и четвертый разрядные выходы второй группы адресных выходов блока .микро -. программного управления соединены с синхровходом регистра набора, с сум- ;мирующнм входом счетчика логических номеров, с входом записи буферного блока памяти и с вычитающим входом счетчика длины вектора тестового набора соответственно, группы выходов регистра набора является группой выходов результата контроля устройства,

2. Устройство п6п,Г отлич а- ю щ е е с я тем, что,блок микропрограммного управления содержит блок модификации адреса и блок памяти, причем группа входов кода логических условий блока модификащш адреса соединена с группой входов кода логических условий блока, группа входов кода логической операции которого соединена с группой входов выбора полей блока памяти, группа информационных входов которо.го соединена с группой входов начальной загрузки блока, входы управления переходом которого соединены с входами управления переходом блока модификации адреса, первая группа адресных выходов которого соединена с группой адресных входов блока памяти, вход считывания которого ,соединен с выходом признака перехода

к следующему адресу микрокоманды блока модификации адреса, выход признака синхронизации контролируемого цифрового блока которого соединен с выходом признака синхронизации блбка, .выходы блока памяти соединены с выходами признаков микрокоманд блока,

первый, второй, третий и четвертый разрядные выходы второй группы адресных выходов которого соединены с первым, вторым, третьим и четвертым разрядными выходами второй группы адресных вьЬсодов блока модификации адреса.

От шины 1

Фие.1

Qtn} ОтЩ

fci WW

к If

кП

От 26

Ст27

От 28

От В

От 13

К 18

Фиг.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

Изобретение относится к вычислительной технике и может, быть использовано при диагностике цифровых блоков. Цель изобретения - расшире ние класса решаемых задач за счет обеспечения процесса формирования тестов, параллельных процессу контроля. Устройство содержит буферный регистр, счетчик логических номеров, регистр набора, блок памяти, буферный блок памяти, счетчик длины вектора тестового набора, выходной коммутатор, блок микропрограммного управления, блок обмена с контролируемым цифровым блоком. В устройстве , распределение входов/выходов объекта контроля осуществляется не программно, а за счет введения блоков памяти. Когда содержимое счетчика логических номеров увеличивается на единицу, содержимое счетчика длины векторов уменьшается на единицу, что обеспечивает коммутацию нового логического номера и вьщачи нового теста. 1 з.п.ф-лы, 6 ил. % W с

От 30От 29

ФигЛ

От 6 ОтВ От 9

РтГЗ

и гв,г7,м Фиг.5

От2в

OmU

К 26,27,28

К 18

Фиг. 6

Редактор Т. Митейко

Составитель А, Сиротская

ТехредКорректор И, Муска

Заказ 4412/46Тираж 671 И.Гайдош Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/3

Производственно-полиграфическое предприятие, у, Ужгород, ул. Проектная, 4

| Многоканальное устройство для тестового контроля | 1974 |

|

SU516039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1984-12-29—Подача