ставляет собой цепочку из Т последовательно соединенных регистров.. Масштабы имеют следующий вид:

е

, f-0,1,...,L+1, (1)

m и L связаны соотношением , т„РМ,., -1 у

K-t

где М.,.П п, ;

Р - натуральное число, удовлетворяющее условию 2p-:-k-2; m.m, ,.., модули остаточной системы

счисления.

Дешифратор 26 предназначен Ш1я выделения подмножества значений {-m+lj m+2,...,m-l} входной переменной ZeD, заданной своим остаточным кодом , Z), где m - фиксирован1

m

2mo, . (,...,k);

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих специализированньк систем различf)

ного назначения, работающих на базе модулярной арифметики.

Цель изобретения - расширение области применения за счет формирования знака числа.10

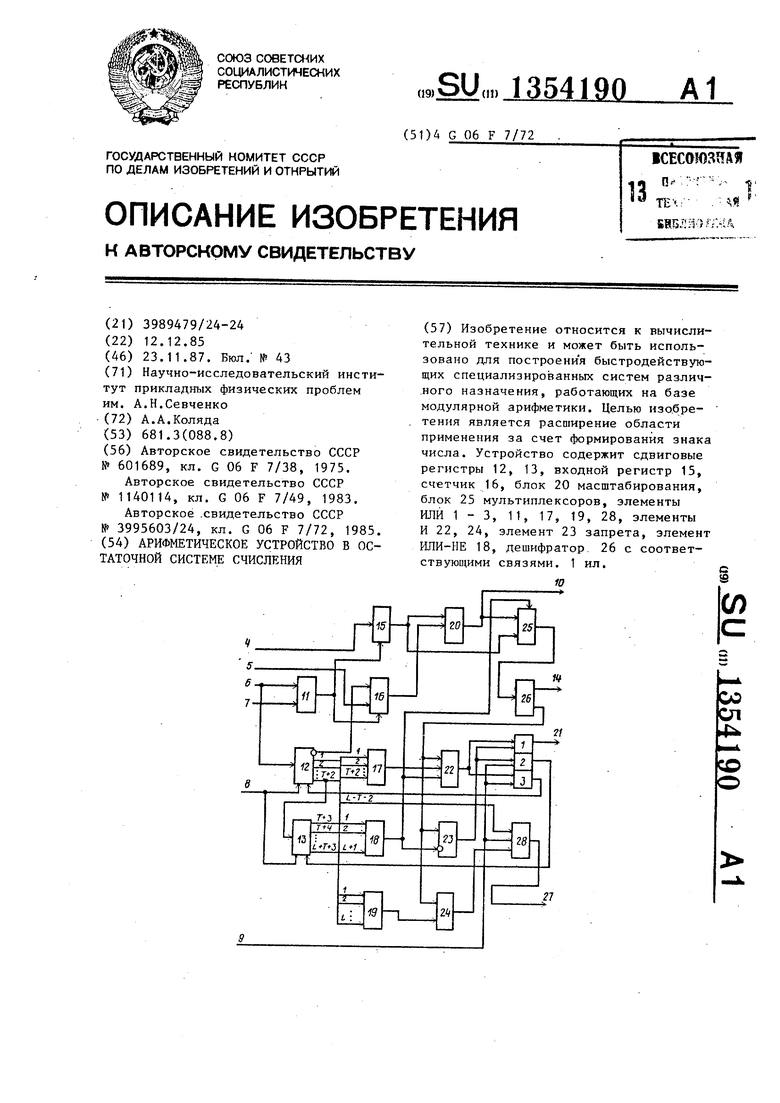

На чертеже представлена схема арифметического устройства в остаточной системе счисления.

Арифметическое устройство содержит элементы ИЛИ 1-3, вход 4 операнда 15 устройства, вход 5 номера масштаба устройства, вход 6 операции формирования знака устройства, вход 7 операции масштабирования устройства, так- (Z,,Z

товый вход 8 устройства, установочный 20 натуральное число такое, вход 9 устройства, выход 10 результата устройства, элемент ИЛИ 11, сдвиговые регистры 12 и 13, выход 14 знака устройства, входной регистр 15, счетчик 16, элемент ИЛИ 17, Э1гемент ИЛИ-НЕ 28, элемент ИПИ 19, блок 20 масштабирования, выход 21 окончания формирования знака устройства, элемент И 22, элемент 23 запрета, элемент И 24, блок 25 мультиплексоров, дешифратор 26, выход 27 начала формирования знака устройства, элемент ИЛИ 28. Элементы ИЛИ 17, ИЛИ-НЕ 18 и ИЛИ 19 имеют соответственно (Т+2), (L+1) и L входов.

Разрядности сдвиговых регистров 12 и 13, осуществляющих сдвиг своих содержимых на один бит влево, составляют (Т+2) и (L+1) двоичных разрядов соответственно.

. Блок 20 масштабирования представляет собой известное устройство, осуществляющее деление входного числа X из диапазона ,

РМ, -1J системы счисления на некото- 45 рьй положительньй масштаб 6р, число которых ограничено, но не меньше, - чем L. Результатом операции масштаби рования является оценка X (ближайшее

что через

|Х|, обозначаемся наименьший неотри- цательньй в)1чет сравнимьй с величиной X по модулю d. На первом и втором 25 выходах формируются соответственно сигналы

1, если ,-т+2,...,-1}

g

(2)

О, в остальных случаях

30 и

г

40

jr цело число) дроби --. В предлагаемом

е

.арифметическом устройстве используется блок масштабирования конвейерного типа, быстродействие которого составляет Т+3 тактов при пропускной спо- собности одна операция масштабирования в один такт.

Элемент задержки, входящий в сос- тав блока 20 масштабирования, пред1, если Zef-m+l,-т+2,...,т-1}

(3)О ,в остальных случаях. Из (2) и (3) следует, что дешиф- 35 ратор 26 является дешифратором второго рода.

Арифметическое устройство в остаточной системе счисления работает следующим образом.

,Цля приведения в исходное состояние на установочньй вход 9 устройства подается сигнал, в результате чего на выходах элементов ИЛИ 2, 3 и 28 - -1 формируются следующие выражения:

У (4)

bV,4.vr;(5)

,vV3 , (6) где U - сигнал, подаваемьй с второго выхода дешифратора 26 на первые входы элементов 22 - 24, получаюш.их соответственно величины аС), , Лф и йфз ;

9, ,V2,

Уз - выходные переменные соответственно элементов ИЛИ 17, РШИ-НЕ 18 и ИЛИ 19, определя50

55

емые по формулам

T4I

V,,Vcr,,,;

(7)

ставляет собой цепочку из Т последовательно соединенных регистров.. Масштабы имеют следующий вид:

е

, f-0,1,...,L+1, (1)

m и L связаны соотношением , т„РМ,., -1 у

K-t

где М.,.П п, ;

Р - натуральное число, удовлетворяющее условию 2p-:-k-2; m.m, ,.., модули остаточной системы

счисления.

Дешифратор 26 предназначен Ш1я выделения подмножества значений {-m+lj m+2,...,m-l} входной переменной ZeD, заданной своим остаточным кодом , Z), где m - фиксирован1

(Z,,Z

m

2mo, . (,...,k);

натуральное число такое,

что через

|Х|, обозначаемся наименьший неотри- цательньй в)1чет сравнимьй с величиной X по модулю d. На первом и втором выходах формируются соответственно сигналы

1, если ,-т+2,...,-1}

g

(2)

натуральное число такое

О, в остальных случаях

20

30 и

г

емые по формулам

T4I

V,,Vcr,,,;

(7)

-.о.|

tt, q,v(yc5 j,).

где . и G.

1,г

- содержимые 1-го и j-ro разрядов сдвиговых регистров 12 и 13 соответственно (,1,..., Т+1; . ,1,-. ...,L),

формирутртся сигналы jf, , у и , принимающие единичное значение. Сигналы У,1- и и 1 с выходов элементов ИЛИ 2 и 3 подаются соответственно на вхоРассмотрим как в арифметическом устройстве реализуется операция определения знака числа. На вход 6 устройства подается единйчньга сигнал. Ь „

которьш поступает в младший разряд

сдвигового регистра 12 и через первый вход элемента ИЛИ 11 на входы приема кода регистра 15 и счетчика 16, ив 10 них через входы 4 и 5 устройства записываются соответственно остаточный код числа А, анализируемого на знак, и номер масштаба (формула (1)). На следующем такте блок 20

ды сброса регистров 12 и 13, вслед- 15 масштабирования начинает формирование ствие чего они обнуляются, а сигнал оценки А дроби. Элементы ИЛИ 17, ИЛИ- с выхода элемента ИЛИ 28 указы- 18 и ИЛИ 19, по текущим значениям вает на то, что во входной регистр 15 разрядов сдвиговых регистров 12 и 13 и счетчик 16 можно загружать исходные получают соответственно величиныV,, данные для очередной операции масш- 20 Vi з. которые поступают на соот- табирования или определения знака числа.

Для вьтолнения операции масштаби-. рования числа XED на некоторьй масштаб S{ необходимо через входы 4 и 5 25 такте то на выход блока 25 устройства на информационные входы мультиплексоров проходит код, подава- регистра 15 и счетчика 16 подать со- мый на второй информационный вход ответственно остаточньй код числа X выхода регистра 15 (остаточный код

числа А). Анализируя выходной код 30 дешифратор 26 вырабатьшает сигналы ЗиЛ, второй из которых с второго выхода дешифратора 26 поступает на

ветствующие.входы логических элементов 22 - 24. Величина ( подается также на управляющий вход блока 25 мультиплексоров, а так как на данном

и номер масштаба, а на вход 7 устройства - единичный сигнал, которьй - через второй вход элемента ИЛИ 11 поступает на входы приема кода регистра

15 и счетчика 16, что приводит к записи в них поданной на входы информации. На слёдуклцем такте код числа X с выхода-регистра 15 поступает на информационньй вход блока 20 масштабирования, а номер 1 масштаба с выхопервые входы логических элементов 22 - 24, в результате .ч его на их выходах формируются соответственно величины l(f,(fj 9 Vj ийфз используе мые для получения элементами ИЛИ 2 и 3 и элементом ИЛИ 28 сигналов у, , )f и , а также сигнала Vt V

да счетчика 16 подается на вход номе-.

ра масштаба блока 20, которьй в тече- 40 вырабатываемого на выходе элемента

вне очередных Т+3 тактов, считая . :

текущий, определяет искомую оценку X. Еслид 1, то знак числа получен

на выходе 14 устройства уже на первом

На каждом такте работы устройства по сигналу, подаваемому с тактового

такте операции, на что указьшает еди50

входа 8 устройства на входы управле- 45 ничное значение сигнала 6 на выходе ния сдвигом сдвиговых регистров 12 21 устройства. В этом случае по сигналам J, 1 иу2,1 сдвиговые регистры 12 и 13 обнуляются, а выход 27 устройства по сигналу устанавливается в единичное состояние. В случае, когда на первом такте U 0 операция определения знака числа А является многотактной, на каждом такте инверсное значение младшего разряда регистра 12 подается на счетньй вход счетчика 16, и так как содержимые сдвиговых регистров ежетактно сдвигаи 13, их содержимые сдвигаются на один разряд влево. Выдвинутое значение старшего разряда регистра 12 за писывается в младший разряд регистра 13.

Операция масштабирования занимает (Т+3) такта,.по истечении которых результат снимается с выхода 10 уст- gg ройства. Уже на первом такте выполняемой операции масштабирования в регистр 15 и счетчик 16 могут быть загружены новые данные.

ются на один разряд влево, то на всех тактах операции определения знака

Рассмотрим как в арифметическом устройстве реализуется операция определения знака числа. На вход 6 устройства подается единйчньга сигнал. Ь „

которьш поступает в младший разряд

сдвигового регистра 12 и через первый вход элемента ИЛИ 11 на входы приема кода регистра 15 и счетчика 16, ив 10 них через входы 4 и 5 устройства записываются соответственно остаточный код числа А, анализируемого на знак, и номер масштаба (формула (1)). На следующем такте блок 20

масштабирования начинает формирование оценки А дроби. Элементы ИЛИ 17, ИЛИ- 18 и ИЛИ 19, по текущим значениям разрядов сдвиговых регистров 12 и 13 получают соответственно величиныV,, Vi з. которые поступают на соот-

такте то на выход блока 25 мультиплексоров проходит код, подава- мый на второй информационный вход выхода регистра 15 (остаточный код

ветствующие.входы логических элементов 22 - 24. Величина ( подается также на управляющий вход блока 25 мультиплексоров, а так как на данном

первые входы логических элементов 22 - 24, в результате .ч его на их выходах формируются соответственно величины l(f,(fj 9 Vj ийфз используемые для получения элементами ИЛИ 2 и 3 и элементом ИЛИ 28 сигналов у, , )f и , а также сигнала Vt V

такте операции, на что указьшает единичное значение сигнала 6 на выходе 21 устройства. В этом случае по сигналам J, 1 иу2,1 сдвиговые регистры 12 и 13 обнуляются, а выход 27 устройства по сигналу устанавливается в единичное состояние. В случае, когда на первом такте U 0 операция определения знака числа А является многотактной, на каждом такте инверсное значение младшего разряда регистра 12 подается на счетньй вход счетчика 16, и так как содержимые сдвиговых регистров ежетактно сдвигаются на один разряд влево, то на всех тактах операции определения знака

а . 1

числа А за исключением первого содержимого счетчика 16 увеличивается на единицу. Благодаря этому на (Р+2)-м такте операции блок 20 масштабирования начинает формирование оценки А. для ,1,...,L-1. После (Т+2)-го такте содержимое регистра 13 становится ненулевым, вследствие чего , цодаваемая с выхода элемента 11Ш-1-ИЕ 18, на управляющий вход блока 25 мультиплексоров принимает нулевое значение, поэтому на выход блока 25 мультиплексоров, а, следовательно, и на вх од дешифратора 26 последова- тельно от такта к такту начинают поступать остаточные коды оценок А ,

л л ло

А ; А , А,... . Описанные действия повторяются до тех пор, пока на втором выходе дешифратора 26 не сформи- рован единичньй сигнал , что приводит к появлению на выходе 21 устройства признака конца операции, а также к обнулению сдвиговых регистро 12 и 13 и появлению сигнала на выхо- де 27 устройства. Знак числа А снимается с выхода 14 знака устройства. Если время вьтолнения операции формирования знака превышает L тактов, то на (L+1)-M такте (Ъ-Т-2)-й разряд сдвигового регистра 13 содержит единицу, вследствие чего на выходе элемента ИЛИ 28, а следовательно, и на выходе 27 устройства появляется единичньй сигнал, указывая на то, что начиная с данного момента времен в арифметическом устройстве может быть инициирована новая операция.

Формула изобретения

Арифметическое устройство в остаточной системе счисления, содержащее два сдвиговых регистра, счетчик, входной регистр, блок масштабирования и блок мультиплексоров, причем вход операнда устройства соединен с информационным входом входного регистра, тактовый вход устройства соединен С входами разрешения сдвига первого и второго сдвиговых регистров, выход блока масштабирования соединен с первым информационным входом блока мультиплексоров и является выходом результата устройства,.о т л и ч а - ю щ е е с я .тем, что, с целью рас-- ширения области применения за счет формирования знака числа, оно содержит депшфратор., элемент запрета, эле

Q д

п 5 д

5

0

5

0

9U6

мент ИЛИ-НЕ, два элемента И и семь элементов Ш1И, причем выход первого элемента ИЛИ является выходом окончания формирования знака устройства, выходы второго и третьего элементов ИЛИ соединены соответственно с входами обнуления второго и первого сдвиговых регистров-, вход номера масштаба устройства соединен с информационным входом счетчика, выход которого соединен с входом номера масштаба блока масштабирования, информационньй вход которого объединен с вторым информационным входом блока мультиплексоров и подключен к выходу входного регистра, вход разрешения приема кот торого объединен с входом разрешения приема счетчика и подключен к выходу четвертого элемента ИЛIi, первьй и вт-орой входы которого соединены соответственно с входами операции формирования знака и операции масштабирования устройства, первый вход четвертого элемента ИЛИ соединен с входом младшего разряда первого сдвигового регистра, инверсный выход младшего разряда которого соединен со счетным входом счетчика, прямые выходы разрядов первого сдвигового регистра соединены соответственно с входами пятого элемента ИЛИ, прямой выход старшего разряда первого сдвигового регистра соединен с входом младшего разряда второго сдвигового регистра, выходы разрядов которого соединены соответственно с входами элемента ИЛИ-НЕ, выход которого соединен с управляющим входом блока мультиплексоров, выход которого соединен с входом дешифратора, первый выход которого является ВЫХОДОМ знака устройства, второй вькод дешифр-атора соединен с первым входом первого элемента И, с информационным входом элемента запрета и с первым входом второго элемента И, второй вход которого соединен с выходом шестого элемента l-L Di, входы которого соединены соответственно с прямыми выходами разрядов первого сдвигового регистра и с выходами разрядов с нулевого по (Ь-Т-З)-й второго сдвигового регистра (L - число масштабов, Т - наименьшее число, не меньше logjK, К - число модулей системы счисления), выход (L-T-2)-ro разряда которого соединен с первым входом седьмого элемента ИЛИ, выход которого является выходом начала формирования

135A19Q

знака устройства, выходы пятого эле-первым входом второго элемента ИЛИ,

мента ИЛИ и элемента ИЛИ-НЕ соединенывторой вход которого соединен с вто-

соответственно с вторым и третьимрым входом третьего элемента ИЛИ,

входами первого элемента И, выход ко-с вторым входом седьмого элемента ИЛИ

торого соединен с первыми входамии соединен с установочным входом устпервого и третьего элементов ИЛИ, вы-ройства, выход второго элемента И

ход элемента запрета соединен с вто-соединен с третьим входом седьмого

рым входом первого элемента ИЛИ и сэлемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для деления чисел в системе остаточных классов | 1985 |

|

SU1287152A1 |

| Устройство для масштабирования числа в интервально-модулярном коде | 1986 |

|

SU1305678A1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

Изобретение относится к вычислительной технике и может быть использовано для построени я быстродействующих специализированных систем различ- .ного назначения, работающих на базе модулярной арифметики. Целью изо.бре- тення является расширение области применения за счет формирования знака числа. Устройство содержит сдвиговые регистры 12, 13, входной регистр 15, счетчик 16, блок 20 масштабирования, блок 25 мультиплексоров, элементы ИЛИ 1 - 3, 11, 17, 19, 28, элементы И 22, 24, элемент 23 запрета, элемент ИЛИ-НЕ 18, дешифратор. 26 с соответствующими связями. 1 ил. да i (Л

| Арифметическое устройство | 1975 |

|

SU601689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для масштабирования чисел в остаточной системе счисления | 1983 |

|

SU1140114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское .свидетельство СССР № 3995603/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-23—Публикация

1985-12-12—Подача