Изобретение относится к вычислительной технике и предназначено для использования в цифровых устройствах, функционирующих в непозиционных кодах и реализующих различные немодуль- ные операции такие как деление, умножение дробей, масштабирование, перевод чисел в двоичную систему счисления.

Целб изобретения - уменьшение объема оборудования.

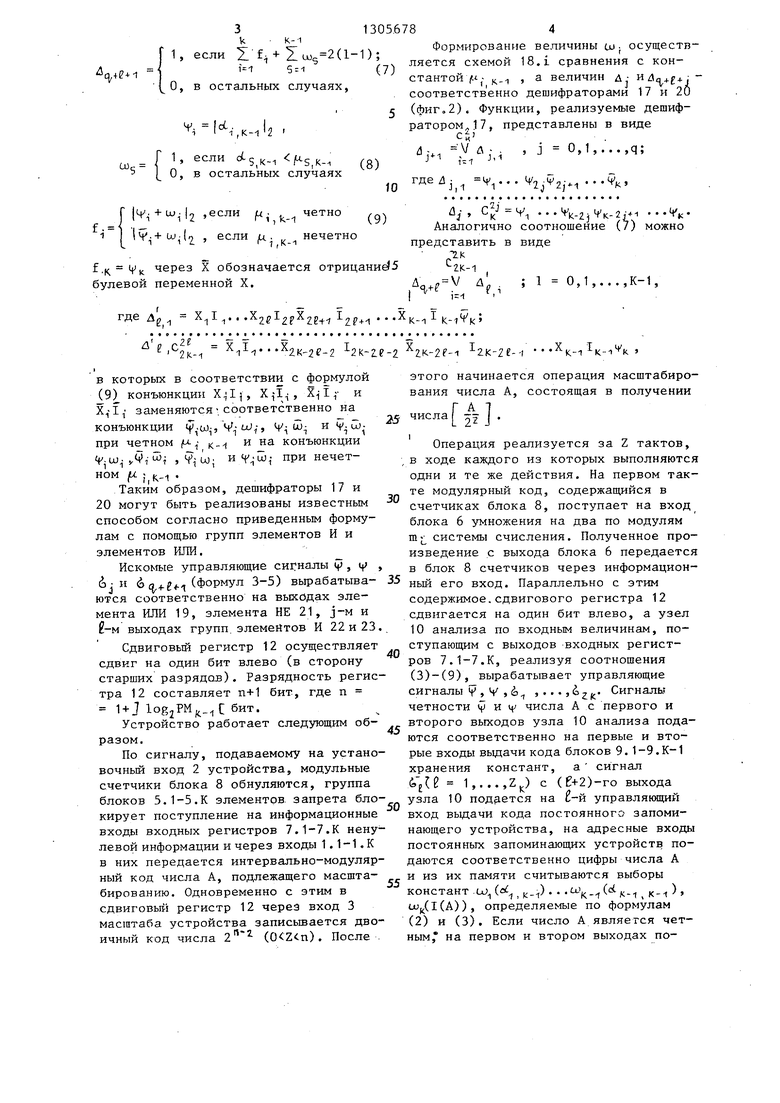

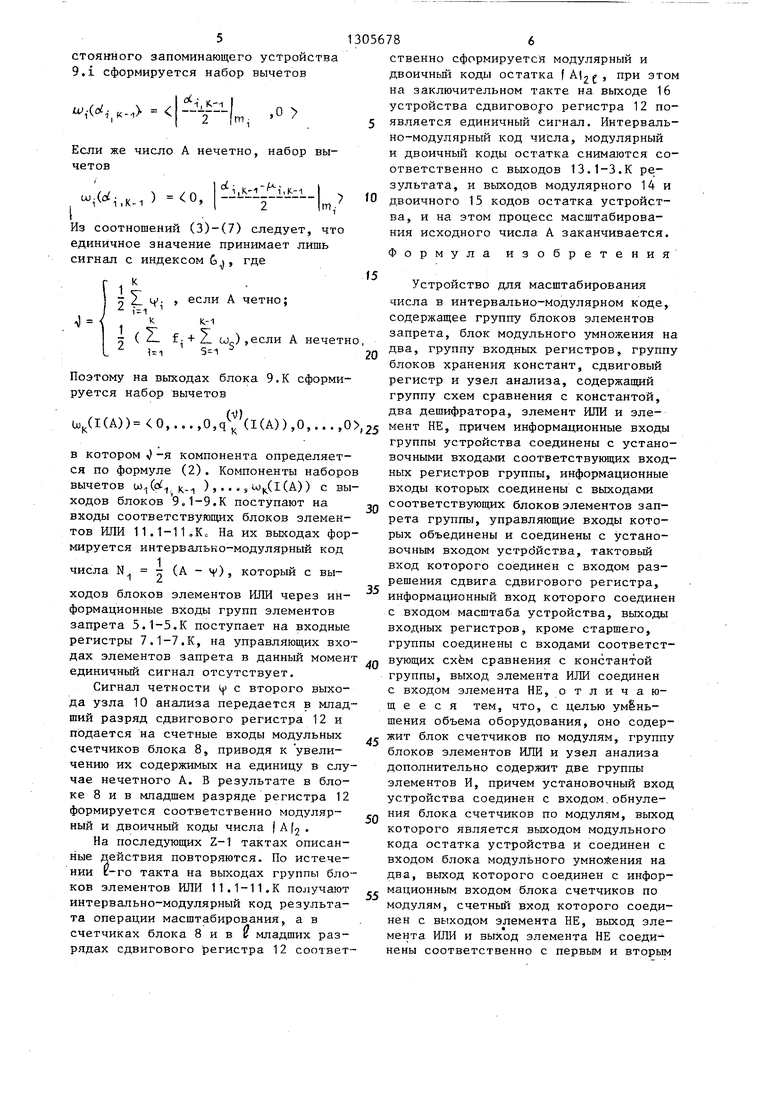

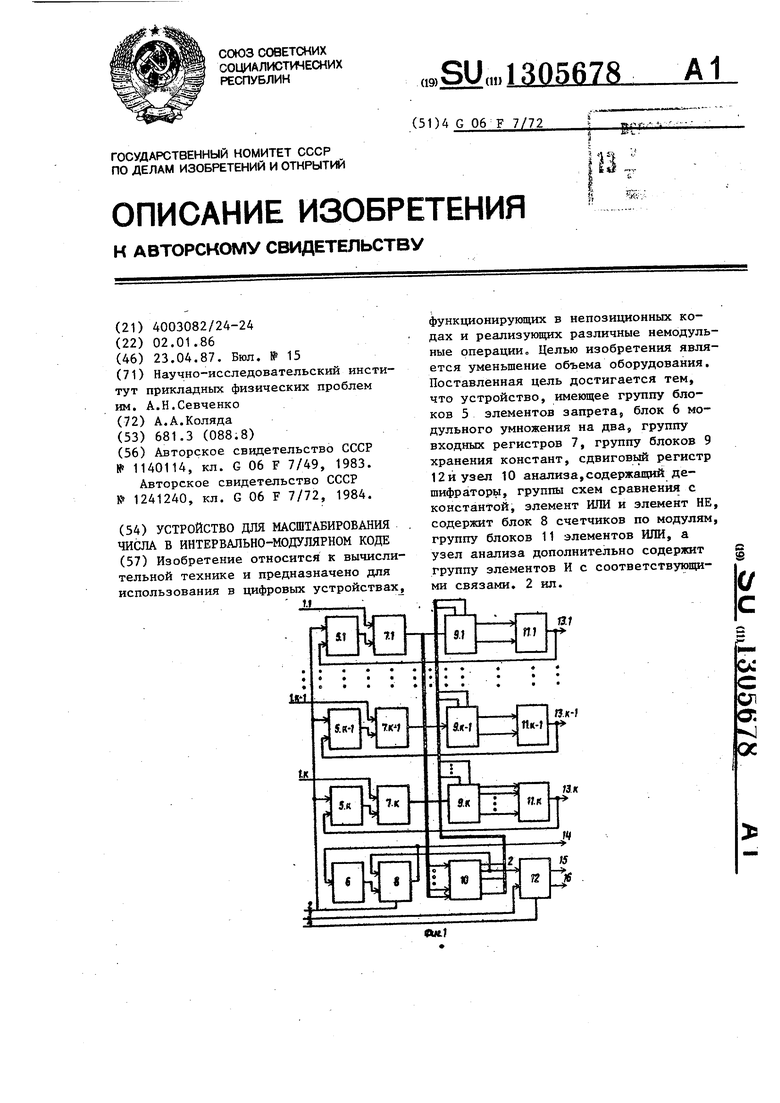

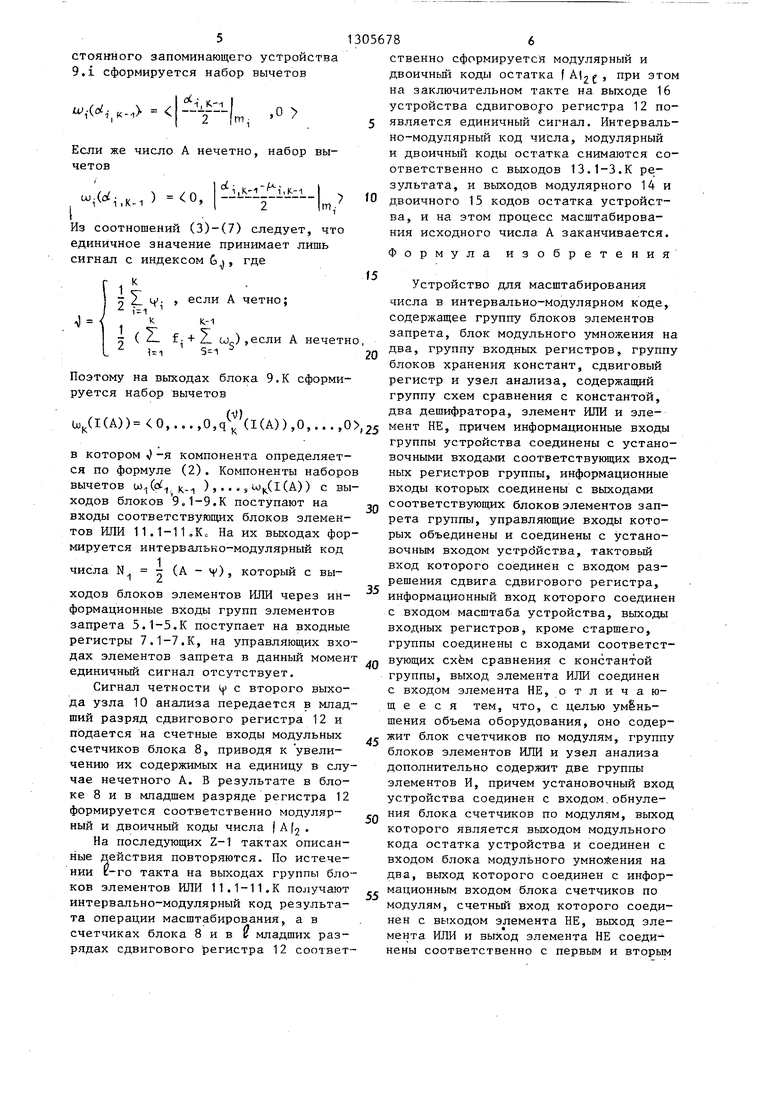

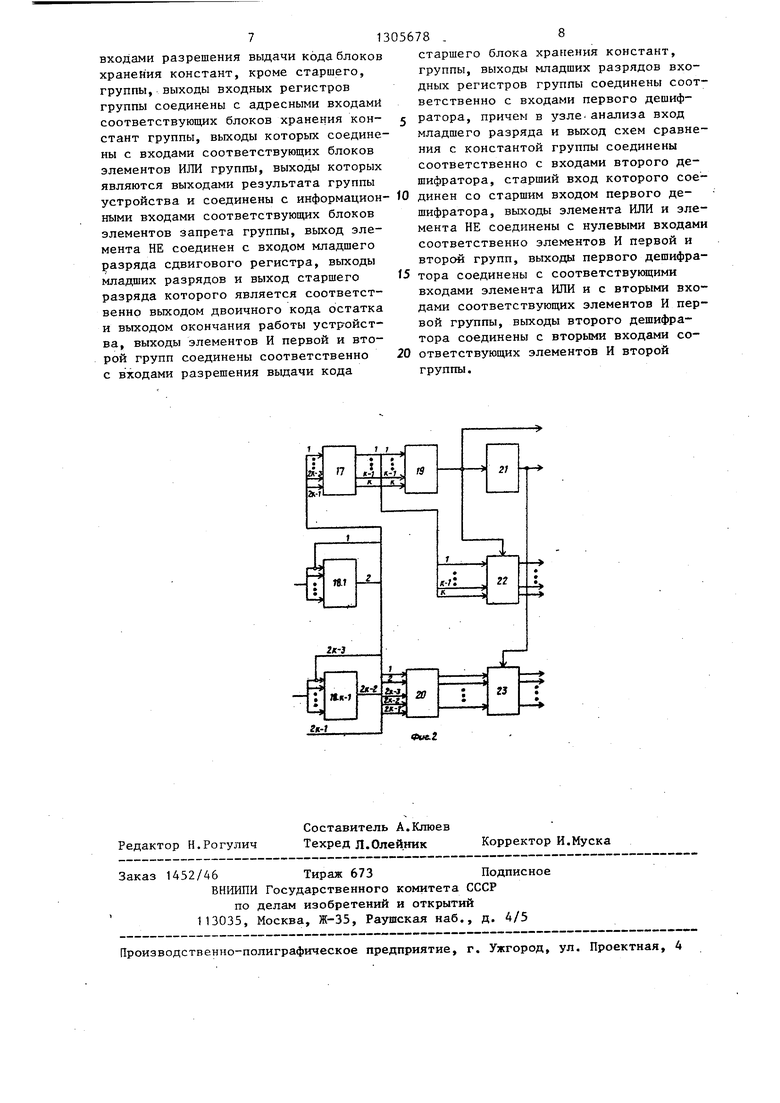

На фиг.1 представлена структурная схема устройства для масштабирования числа в интервально-модулярном коде; на фиг.2 - структура узла анализа. Устройство для масштабирования числа в интервально-модулярном коде содержит группу информационных входов 1,1-1.К (К - число модулей системы счисления), установочный вход 2, вход 3 масштаба, тактовый вход 4 уст- ройства, группу блоков 5.1-5.К элементов запрета, блок 6 модульного умножения на два, группу входных регистров 7.1-7.К, блок 8 счетчиков по модулям, группу блоков 9.1-9.К хранения констант, узел 10 анализа, группу блоков 11.1-11.К элементов ИЛИ, сдвиговый регистр 12, группу выходов 13.1-13.К результата

(х,- - (bDfx.

К-1 (mj

t + 1

при 1,2,,..,q+1; i - К;

((1)) . при ,...Z,; ,

где

i,

К-1

m. - 1(1) nil, i-й модуль системы счисления;

соответственно i-я и К-я цифры интерваль- но-модулярного представления 1 числа; четный и т,7/2Р+К-2, где Р -:фиксировансС;

М.

-л

i,K-i ,K-i I i.K-i f i -i m;

40

К-1

Мк-1

45

., -, . Г1К-1 М,., М,, ----Узел 10 анализа служит для формирования по входным величинам , ,.

и |I(A)12, поступающим соответ- ное натуральное число. ртвенно на 1-й и К-й входы, сигналов ; Интервально-модулярный код (o. , V У , 6, ,( определяемых следующими выражениями

CV-h-t

2 К--1 К--1 1(А.)) произвольного числа А из диапазона

п Г-рм -РМ -1 1 к-1 J

системы счисления определяется соотношением

К-1

1,;., 1(А)м,.,.

в котором

устройства, выходы 14 и 13 соответственно модулярного и двоичного кодов остатка, выход 16 окончания работы устройства.

Узел 10 анализа (фиг.2) содержит первый дешифратор 17, группу схем 18.1-18.К-1 сравнения с константой, элемент ИЛИ 19, второй дешифратор 20, элемент НЕ 21, первую и вторую группы элементов И 22 к 23.

Количество двоичных разрядов в входном регистре 7.i, элементов запрета в блоке 5.1 и элементов ИЛИ в блоке 11.1 (i 1-К) равно Jlog тД, гдеЗС - ближайшее целое не меньшее содержимого скобок.

Элементы ИЛИ блока 11.1 имеют Z

входов

2, i 1 К+

при 1 К;

K+q+1,при , q - целая часть г .

30

j

В блок 9.1 хранения констант по адресу Х€ 0,1... ,т ,- ll записьшает- ся набор констант

W .(X .) (X .) ,.. . ,qf (Х,.),(1)

компоненты которого определяются со- .отношением

при ,2,...; 1 7 К;

(2)

сС;

М.

-л

i,K-i ,K-i I i.K-i f i -i m;

К-1

Мк-1

., -, . Г1К-1 М,., М,, ----Узел 10 анализа служит для формирования по входным величинам , ,.

и |I(A)12, поступающим соответ- ртвенно на 1-й и К-й входы, сигналов V У , 6, ,( определяемых следующими выражениями

V (All

6j УЛ ,

у л,. ;

j 1 Ч 1;

+ i4 + -i

(3) (4)

1,...,К. (5)

Aj 1

1, если II у. 2(j-1);

(6)

О, в остальных случаях.

+-1

31305.678

k

1, если Z (1-1);

K-l

Z ijj 5:1

(7)

0, в остальных случаях,

ля ст со 5 (ф

.,K-J2

I

Формирование величины to j осуществляется схемой 18.1 сравнения с константой .-, , а величин д- иЛа..;- соответств енно дешифраторами 17 и 20 (фиг.2). Функции, реализуемые дешиф

1, О,

если 5. s,K-. в остальных случаях

четно нечетно

через X обозначается отрицани 5 булевой переменной X.

(8)

и.

, .. .Vj... .2у+1 , Аналогично соотношение (7) можно

виде

1 0,1,...,K-1,

где д

f

2,1

- . . ..

c

2 2IC-1

. . .X2f,,2e-2

в которых в соответствии с формулой (9) конъюнкции , Х, 1, Х 11 и , заменяются - соответственно на

конъюнкции , , V- Ш и четном (LX. и на конъюнкции «f.uj. ,,-U); и ,- при нечет 0 1 i,(; i

Таким образом, дешифраторы 17 и

20 могут быть реализованы известным способом согласно приведенным формулам с помощью групп элементов И и элементов РШИ,

Искомые управляющие V , v

этого начинается операция вания числа А, состоящая

25

числа

L 22 J

30

Операция реализуется з в ходе каждого из которых одни и те же действия. На те модулярный код, содерж счетчиках блока 8, поступ блока 6 умножения на два mj системы счисления. Пол изведение с выхода блока в блок 8 счетчиков через

ен j и aq. (формул 3-5) вырабатыва- 35 ньш его вход. Параллельно

ются соответственно на выходах элемента ИЛИ 19, элемента НЕ 21, j-M и -м выходах групп, элементов И 22 и 23

Сдвиговый регистр 12 осуществляет сдвиг на один бит влево (в сторону старших разрядов). Разрядность регистра 12 составляет п+1 бит, где п 1 + J бит.

Устройство работает следующим образом.

По сигналу, подаваемому на установочный вход 2 устройства, модульные счетчики блока 8 обнуляются, группа блоков 5.1-5.К элементов запрета блокирует поступление на информационные входы входных регистров 7.1-7.К ненулевой информации и через входы 1.1-1 .К в них передается интервально-модуляр- ный код числа А, подлежащего масштабированию. Одновременно с этим в СДВИГОВЫЙ регистр 12 через вход 3 масштаба устройства записьшается двоичный код числа 2 (.n). После

40

45

50

55

содержимое.сдвигового рег сдвигается на один бит вл 10 анализа по входным вел ступающим с выходов входны ров 7.1-7.К, реализуя соот (3)-(9), вырабатывает упра сигналы V , V , (i ,...,2й четности V и V числа А с п второго выходов узла 10 ан ются соответственно на пер рые входы вьщачи кода блоков хранения констант, а си 1,...,Z) с (Е+2)-г узла 10 подается на t-й уп вход выдачи кода постоянно нающего устройства, на адр постоянных запоминающих ус даются соответственно цифр и из их памяти считываются констант .и; (: .,). . .ы. ( UJ(I(A)), определяемые по (2) и (3). Если число А яв ным на первом и втором вы

ак-ге-г гк-2Р-1 гк-ге--)

этого начинается операция масштабирования числа А, состоящая в получении

25

числа

L 22 J

Операция реализуется за Z тактов, в ходе каждого из которых выполняются одни и те же действия. На первом такте модулярный код, содержащийся в счетчиках блока 8, поступает на вход блока 6 умножения на два по модулям mj системы счисления. Полученное произведение с выхода блока 6 передается в блок 8 счетчиков через информационньш его вход. Параллельно

с этим

0

5

0

5

содержимое.сдвигового регистра 12 сдвигается на один бит влево, а узел 10 анализа по входным величинам, поступающим с выходов входных регистров 7.1-7.К, реализуя соотношения (3)-(9), вырабатывает управляющие сигналы V , V , (i ,...,2й Сигналы четности V и V числа А с первого и второго выходов узла 10 анализа подаются соответственно на первые и вторые входы вьщачи кода блоков 9. 1-9.К-1 хранения констант, а сигнал 1,...,Z) с (Е+2)-го выхода узла 10 подается на t-й управляющий вход выдачи кода постоянного запоминающего устройства, на адресные входы постоянных запоминающих устройств подаются соответственно цифры числа А и из их памяти считываются выборы констант .и; (: .,). . .ы. (ci . ., ) , UJ(I(A)), определяемые по формулам (2) и (3). Если число А является четным на первом и втором выходах постоянного запоминающего устройства 9.1 сформируется набор вычетов

и,-(о. к-,

Ч , К.-1

т,

,0

Если же число А нечетно, набор вычетов

.K-i 0

JL.

m.

Из соотношений (3)-(7) следует, что единичное значение принимает лишь сигнал с индексом &., где

к

9 Ц если А четно; , i -i

) { Т

- ( Z f: + 2L и,),если А нечет

Z 1 /- - J

Поэтому на вьпсодах блока 9.К сформируется набор вычетов

L(I(A)) О,... ,0,(I(A)) ,0,.. . ,0

в котором i) -я компонента определяется по формуле (2). Компоненты наборов вычетов ы(о ц. ),..., WH(I(A)) с выходов блоков 9,1-9.К поступают на входы соответствующих блоков элементов ИЛИ 11.1-11.Кс На их выходах формируется интервально-модулярный код

числа N. - (А - у), который с выходов блоков элементов ИЛИ через информационные входы групп элементов запрета 5.1-5.К поступает на входные регистры 7.1-7.К, на управляющих входах элементов запрета в данный момент единичный сигнал отсутствует.

Сигнал четности Ц) с второго выхода узла 10 анализа передается в младший разряд сдвигового регистра 12 и подается на счетные входы модульных счетчиков блока 8, приводя к увеличению их содержимых на единицу в случае нечетного А. В результате в блоке 8 и в младшем разряде регистра 12 формируется соответственно модулярный и двоичный коды числа | А fj .

На последующих Z-1 тактах описанные действия повторяются. По истечении К-го такта на выходах группы блоков элементов ИЛИ 11.1-11.К получают интервально-модулярный код результата операции масштабирования, а в счетчиках блока 8 и в t младших разрядах сдвигового регистра 12 соответO

5

0

5

30

35

40

45

50

55

ственно сформируется модулярный и двоичньо коды остатка f при этом на заключительном такте на выходе 16 устройства сдвигового регистра 12 появляется единичный сигнал. Интервально-модулярный код числа, модулярный и двоичный коды остатка снимаются соответственно с выходов 13.1-3.К результата, и выходов модулярного 14 и двоичного 15 кодов остатка устройства, и на этом процесс масштабирования исходного числа А заканчивается.

Формула изобретения

Устройство для масштабирования числа в интервально-модулярном коде, содержащее группу блоков элементов запрета, блок модульного умножения на два, группу входных регистров, группу блоков хранения констант, сдвиговый регистр и узел анализа, содержащий группу схем сравнения с константой, два дешифратора, элемент ИЛИ и элемент НЕ, прич€1М информационные входы группы устройства соединены с установочными входа ги соответствующих входных регистров группы, информационные входы которых соединены с выходами соответствующих блоков элементов запрета группы, управляющие входы которых объединены и соединены с установочным входом устройства, тактовый вход которого соединён с входом разрешения сдвига сдвигового регистра, информационный вход которого соединен с входом масштаба устройства, выходы входных регистров, кроме старшего, группы соединены с входами соответствующих схем сравнения с константой группы, выход элемента ИЛИ соединен с входом элемента НЕ, о т л и ч а ю- щ е е с я тем, что, с целью уменьшения обьема оборудования, оно содержит блок счетчиков по модулям, группу блоков элементов ИЛИ и узел анализа дополнительно содержит две группы элементов И, причем установочный вход устройства соединен с входом.обнуления блока счетчиков по модулям, выход которого является выходом модульного кода остатка устройства и соединен с входом блока модульного умножения на два, выход которого соединен с информационным входом блока счетчиков по модулям, счетньп вход которого соединен с выходом элемента НЕ, выход элемента ИЛИ и выход элемента НЕ соединены соответственно с первым и вторым

входами разрешения выдачи кода блоков хранения констант, кроме старшего, группы, выходы входных регистров группы соединены с адресными входами соответствующих блоков хранения констант группы, выходы которых соединены с входами соответствующих блоков элементов ИЛИ группы, выходы которых являются выходами результата группы устройства и соединены с информационными входами соответствующих блоков элементов запрета группы, выход элемента НЕ соединен с входом младшего разряда сдвигового регистра, выходы младших разрядов и выход старшего разряда которого является соответственно выходом двоичного кода остатка и выходом окончания работы устройства, выходы элементов И первой и второй групп соединены соответственно с входами разрешения вьщачи кода

Редактор Н.Рогулич

Составитель А.Клюев Техред Л.Олей.ник

Заказ 1452/46 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

старшего блока хранения констант, группы, выходы младших разрядов входных регистров группы соединены соответственно с входами первого дешифратора, причем в узле- анализа вход младшего разряда и выход схем сравнения с константой группы соединены соответственно с входами второго дешифратора, старший вход которого соединен со старшим входом первого дешифратора, выходы элемента ИЛИ и элемента НЕ соединены с нулевыми входами соответственно элементов И первой и второй групп, выходы первого дешифратора соединены с соответствукнцими входами элемента ИЛИ и с вторыми входами соответствующих элементов И первой группы, выходы второго дешифратора соединены с вторыми входами соответствующих элементов И второй группы.

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для нормализации чисел в модулярном коде | 1984 |

|

SU1242942A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

Изобретение относится к вычислительной технике и предназначено для использования в цифровых устройствах, функционирующих в непозиционных кодах и реализующих различные немодульные операции Целью изобретения является уменьшение объема оборудования. Поставленная цель достигается тем, что устройство, имеющее группу блоков 5 элементов запрета, блок 6 модульного умножения на два, группу входных регистров 7, группу блоков 9 хранения констант, сдвиговый регистр 12йузел 10 анализа,содержащий дешифраторы, группы схем сравнения с константой, элемент ИЛИ и элемент НЕ, содержит блок 8 счетчиков по модулям, группу блоков 11 элементов ИЛИ, а узел анализа дополнительно содержит группу элементов И с соответствующими связами. 2 ил. I (/ С ч h ( f Сл: с О1 ОС

| Устройство для масштабирования чисел в остаточной системе счисления | 1983 |

|

SU1140114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел в интервально-модулярном коде | 1984 |

|

SU1241240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1986-01-02—Подача