Изобретение относится к функциональным аналого-цифровым преобразователям и предназначено для использования в приборостроении, управляющих и инфо рмацион- но-измерительных системах.

Целью изобретения является расширение области применения за счет обеспечения формирования логарифмической зависимоц- ти выходных сигналов.

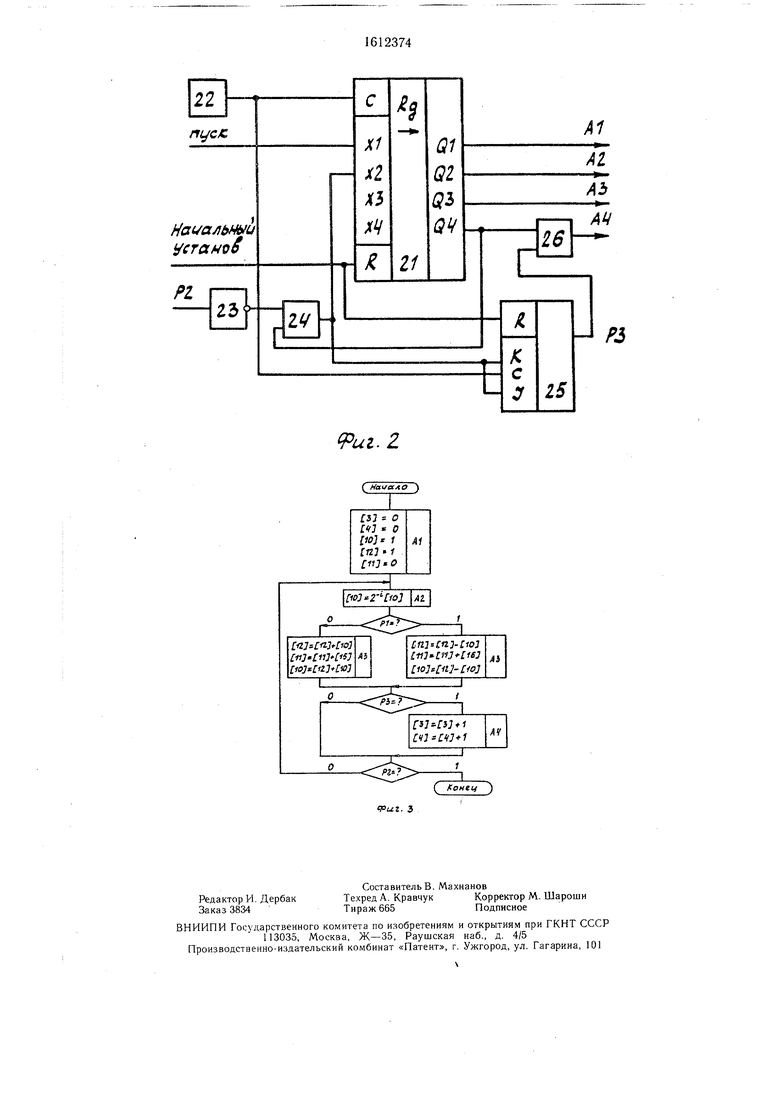

На фиг. 1 представлена схема преобразователя; на фиг. 2 - схема устройства управления; на фиг. 3 - блок-схема алгоритма логарифмического преобразования.

Преобразователь содержит компаратор 1, цифроаналоговый преобразователь 2, счетчики 3 и 4, мультиплексоры 5-7, сумматоры 8 и 9, регистры 10-12, блок 13 инверторов, матричный сдвигатель 14, постоянные запоминающие устройства 15 и 16 дешифратор 17, элемент ИЛИ 18, триггер 19 и устройство 20 управления.

Устройство 20 управления содержит сдвиговый регистр 21, генератор 22 тактов, инвертор 23, элемент И 24, JK-триггер 25 и элемент И 26.

Преобразователь работает следующим образом.

Сигналом начальной установки (н. у.) обнуляется сдвиговый регистр 21 и IК.-триггер 25 устройства управления. Начальная установка нужна только при первичном запуске устройства после включения питания. В конце каждого цикла преобразования в сдвиговом регистре 21 формируется нулевой код. Процедура кодирования начинается по сигналу «Пуск, по которому в младший разряд сдвигового регистра 21 заносится единица, что приводит к началу работы по кодированию входного напряжения. Вычисление значения логарифмической функции осуществляется интеративно.

Для нахождения функции логарифма от входного сигнала X, представленного в форме напряжения, находят представление аргумента в следующем виде:

X 7

Л J-.

:i;

S(l+5,- 2-) где ё/ - переменная, принимающая значения «-|-1 или «-1, i - 1, 1, 2, 2, ..., п-1, п-1. Установление соответствия между входным сигналом X и рядом значений g,- позволяет установить соответствие и между логарифмами:

1пХ (.Г1. (l+li 2-)

(2

Таким образом, в устройстве используется алгоритм Волдера с двойными интерацион- ными щагами. Однако, при классической, цифровой реализации алгоритма Волдера начальное значение аргумента не сохраняется, а участвует в преобразовании. В предлагаемом преобразователе используется множитеЯьное свойство цифроаналоговых преобразователей, реализуемое подачей аналогового сигнала на вход опорного напряжения. Опорное напряжение Е подается на второй вход компаратора. Математически такое изменение алгоритма выражается- в лишнем умножении, но при реализации путем перестановки местами напряжений X и Е (если исходить из известной схемы линейного аналого-цифрового преобразователя) это лищнее умножение не влечет дополнительных аппаратных затрат.

Значение |, непосредственно в преобразователе не реализуется. Вместо него на выходе компаратора 1 формируется признак Р1,

принимающий значения «О и «1 и обеспечивающий в преобразователе действия, эквивалентные смене знака у |,. Алгоритм итерационного подбора кода логарифма приведен на фиг. 3. Знак текущего |, выбирается в соответствии с уравнением (1) из

0 выражения следующего вида:

sign|, -JnUll+l 2-)-1,

KsT

гдek 1, 1, 2, 2, ..., i-1, i-1.

Представляется знак |, сигналом на выходе компаратора 1.

Из выражения (2) следует, что искомое значение логарифма может быть вычислено как сумма табличных логарифмов In (1 ) или 1п() в зависимости от знака |/.

Q Значения табличных логарифмов записано в постоянных запоминающих устройствах 15 и 16, а процедура вычисления суммы S,+i представляется в следующем виде:

S, S,-+ln(l+|r2 ). Управляющие сигналы А1, А2, A3 и А4,

5 обеспечивающие вычисления в соответствии с блок-схемой (фиг. 3), вырабатываются устройством 20 управления. Управляюц1ий сигнал А1 вырабатывается однократно и слу- .жит для начальной установки элементов логарифмического преобразователя. Управ0 ляющие сигналы А2, A3 и А4 обеспечивают итерационное поразрядное вычисление функции логарифма и вырабатываются в циклическом режиме. Двойные итерационные шаги обеспечиваются триггером 25, включенным

р- по схеме счетного триггера.

Благодаря наличию в устройстве управления 1К-триггера 25 сигнал с выхода Q4 сдвигового регистра 21 поступает на выход устройства А4 через элемент И 26 в зависимости от признака РЗ, которым является

Q выход 1К-триггера 25. Признак РЗ, как следует из блок-схемы (фиг. 3), обеспечивает повторное выполнение итерации, т. е. итерации с той же константой, что обеспечивается сохранением кода в счетчике 4 при повторной итерации. Завершение преобразова5 ния обеспечивает признак Р2, который соответствует установке на Счетчике 4 кода п-й итерации. Эта итерация уже не должна выполняться, так как все искомые цифры результата получены. Начальная установка триггера 25 в нулевое состояние обеспечивает увеличение кода счетчика 4 при повторной итерации. Признак Р2 вырабатывается дешифратором 17.

сумматора, выход которого соединен с информационным входом первого регистра, выход которого соединен с вторым входом второго сумматора, выход второго счетчика сое- динен с входами первого и второго постоянных запоминающих устройств и входом дешифратора, выход которого является шиной признака готовности результата преобразования и соединен с вторым входом устройства управления, выходы первого и второго 10 постоянных запоминающих устройств соединены соответственно с первым и вторым инфорационными входами третьего мультиплексора, входы начальной установки первого, второго и третьего регистров, пер1. Аналого-цифровой преобразователь,вого и второго счетчиков объединены н соединены с первым выходом устройства упТаким образом, предлагаемый преобразователь выполняет поразрядное логарифми- «lecKoe аналого-цифровое преобразование без снижения точности по сравнению с линейным аналого-цифровым преобразованием.

Формула изобретения

25

содержащий компаратор, первый вход которого соединен с выходом цифроаналогового преобразователя, первый регистр, выход которого является выходной шиной, и устройство управления, первый вход которого является шиной пуска, отличающийся тем, что, с целью расширения области применения за счет обеспечения формирования логарифмической зависимости выходных сигналов, в него введены два счетчика, три мультиплексора, два сумматора, второй и третий регистры, блок инверторов, матричный сдви- гатель, два постоянных Запоминающих устройства, дешифратор, элемент ИЛИ и триггер, причем выход второго регистра соединен с первым информационным входом первого сумматора, первым информационным ,. входом первого мультиплексора и цифровым входом цифроаналогового преобразователя, аналоговый вход которого является входной шиной, информац.ионный вход второго регистра соединен с выходом первого сумматора, второй информационный вход которого соединен с выходом второго муль- типлексора, выход третьего регистра соединен с первым информационным входом второго мультиплексора, информационным входом матричного сдвигателя и входом блока инверторов, выход которого соединен с вторым информационным входом второго мультиплексора, выход матричного сдвигателя соединен с вторым информационным входом первого мультиплексора, выход которого соединен с информационным входом третьего

равления, второй выход которого соединен со счетным входом первого счетчика, первым установочным входом триггера и первым входом элемента ИЛИ, третий выход уст- 20 ройства управления соединен с входами синхронизации первого и второго регистров, вторым установочным входом триггера и вторым входом элемента ИЛИ, выход триггера соединен с входом управления первого мультиплексора, выход элемента ИЛИ соединен с входом синхронизации третьего регистра, счетный вход второго счетчика соединен с четвертым выходом устройства управления, третий вход которого является шиной начальной установки.

2. Преобразователь по п. 1, отличающийся тем, что устройство управления выполнено на сдвиговом регистре, генераторе тактов, 1К-триггере, двух элементах И и инверторе, вход которого является вторым входом устройства управления, первым входом которого является вход младшего разряда сдвигового регистра, вход сдвига которого соединен с выходом генератора тактов, вход сброса объединен с R-входом триггера и является третьим входом устройства

управления, первым, вторым и третьим вы- 40 ходами которого являются соответственно первый, второй и третий выходы сдвигового регистра, начиная с младшего разряда, четвертый выход сдвигового регистра соединен с первыми входами первого и второго элементов И, второй вход первого

регистра, вход числа сдвигов матричного 45.элемента И соединен с выходом 1К-тригсдвигателя соединен с выходом первого счетчика, второй вход компаратора соединен с источником опорного напряжения, выход компаратора соединен с входом переноса в младший разряд первого сумматогера, а выход является четвертым выходом устройства управления, второй вход второго элемента И соединен с выходом инвертора, а выход соединен с входом разряда сдвигового регистра, следующего за

i vy 114, 1 pel, Ч-Jit. д. j iv/m.ci и о a.

pa и входами управления второго и третьего° младшим его разрядом, и с I- и К-входами

мультиплексоров, выход третьего мультиплек-1К-триггера, С-вход которого соединен с высора соединен с первым входом второгоходом генератора тактов.

динены с первым выходом устройства уп5

,.

равления, второй выход которого соединен со счетным входом первого счетчика, первым установочным входом триггера и первым входом элемента ИЛИ, третий выход уст- 0 ройства управления соединен с входами синхронизации первого и второго регистров, вторым установочным входом триггера и вторым входом элемента ИЛИ, выход триггера соединен с входом управления первого мультиплексора, выход элемента ИЛИ соединен с входом синхронизации третьего регистра, счетный вход второго счетчика соединен с четвертым выходом устройства управления, третий вход которого является шиной начальной установки.

2. Преобразователь по п. 1, отличающийся тем, что устройство управления выполнено на сдвиговом регистре, генераторе тактов, 1К-триггере, двух элементах И и инверторе, вход которого является вторым входом устройства управления, первым входом которого является вход младшего разряда сдвигового регистра, вход сдвига которого соединен с выходом генератора тактов, вход сброса объединен с R-входом триггера и является третьим входом устройства

управления, первым, вторым и третьим вы- 0 ходами которого являются соответственно первый, второй и третий выходы сдвигового регистра, начиная с младшего разряда, четвертый выход сдвигового регистра соединен с первыми входами первого и второго элементов И, второй вход первого

5.элемента И соединен с выходом 1К-тригэлемента И соединен с выходом 1К-триггера, а выход является четвертым выходом устройства управления, второй вход второго элемента И соединен с выходом инвертора, а выход соединен с входом разряда сдвигового регистра, следующего за

-ч i vy 114, 1 pel, Ч-Jit. д. j iv/m.ci и о a.

младшим его разрядом, и с I- и К-входами

/тусх;

Hai a/JMbiu

УГГД /VP/

Q1 Q2 Q3 Q

A1

At

Ab

26

АЦ

21

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1520659A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для коррекции положения изображения объекта | 1989 |

|

SU1785015A1 |

Аналого-цифровой преобразователь предназначен для использования в качестве логарифмического преобразователя для ввода аналоговой информации в микро- и мини-ЭВМ и может найти применение в приборостроении, управляющих и информационно-измерительных системах. Цель изобретения - расширение области применения аналогоцифровых преобразователей. Для этого в устройство, содержащее компаратор 1, цифроаналоговый преобразователь 2, выход которого соединен с первым входом компаратора 1, первый регистр 11 и устройство управления 20 введены счетчики 3, 4, мультиплексоры 5 - 7, сумматоры 8, 9, регистры 10 , 12, блок инверторов 13, матричный сдвигатель 14, постоянные запоминающие устройства 15, 16, дешифратор 17, элемент ИЛИ 18, триггер 19, причем вход устройства соединен с аналоговым входом цифроаналогового преобразователя 2, цифровой вход которого соединен с выходом регистра 12, первым входом сумматора 9 и первым входом мультиплексора 5, информационный вход регистра 12 соединен с выходом сумматора 9, второй вход которого соединен с выходом мультиплексора 7, первый вход мультиплексора 7 соединен с выходом регистра 10, второй вход мультиплексора 7 соединен с выходом цепочки инверторов 13, вход которой вместе с входом матричного сдвигателя 14 соединен с выходом регистра 10, выход матричного сдвигателя 14 соединен с вторым входом мультиплексора 5, выход мультиплексора 5 соединен с входом регистра 10. 1 з.п. ф-лы, 3 ил.

PI

гъ

It/

ui.Z

Ai

/y

t

/C

С

J

(НаиехлО )

| Анисимов А | |||

| В | |||

| и др | |||

| Аналоговые к гибридные вычислительные машины, 1984, с | |||

| Переносный кухонный очаг | 1919 |

|

SU180A1 |

| Гнатек Ю | |||

| Р | |||

| Справочник по ЦА и АЦ преобразователям | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

| рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-12-07—Публикация

1988-12-26—Подача