Изобретение относится к электротехнику, в частности к стабилизированным преобразователям с переменным выходным напряжением или током различной формы.

Целью изобретения является расширение функциональных возможностей и повышение точности устройства формирования сигнала обратной связи в стабилизированных преобразовате- лях с переменным выходным напряжением или током.

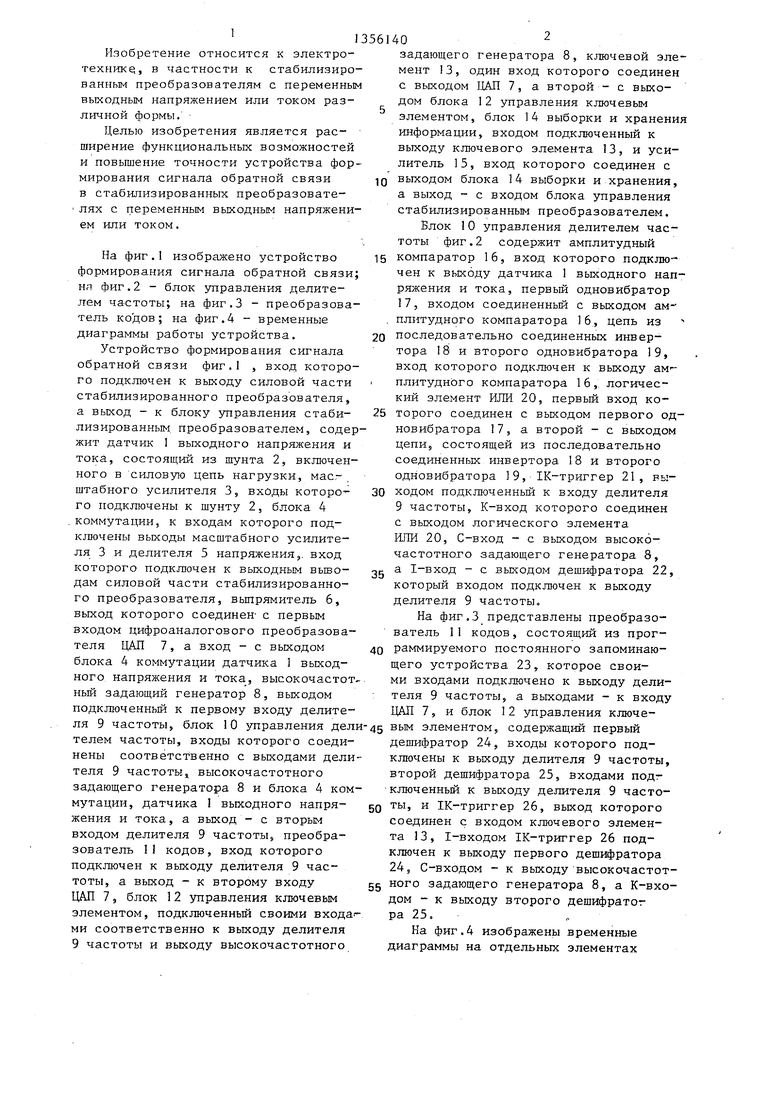

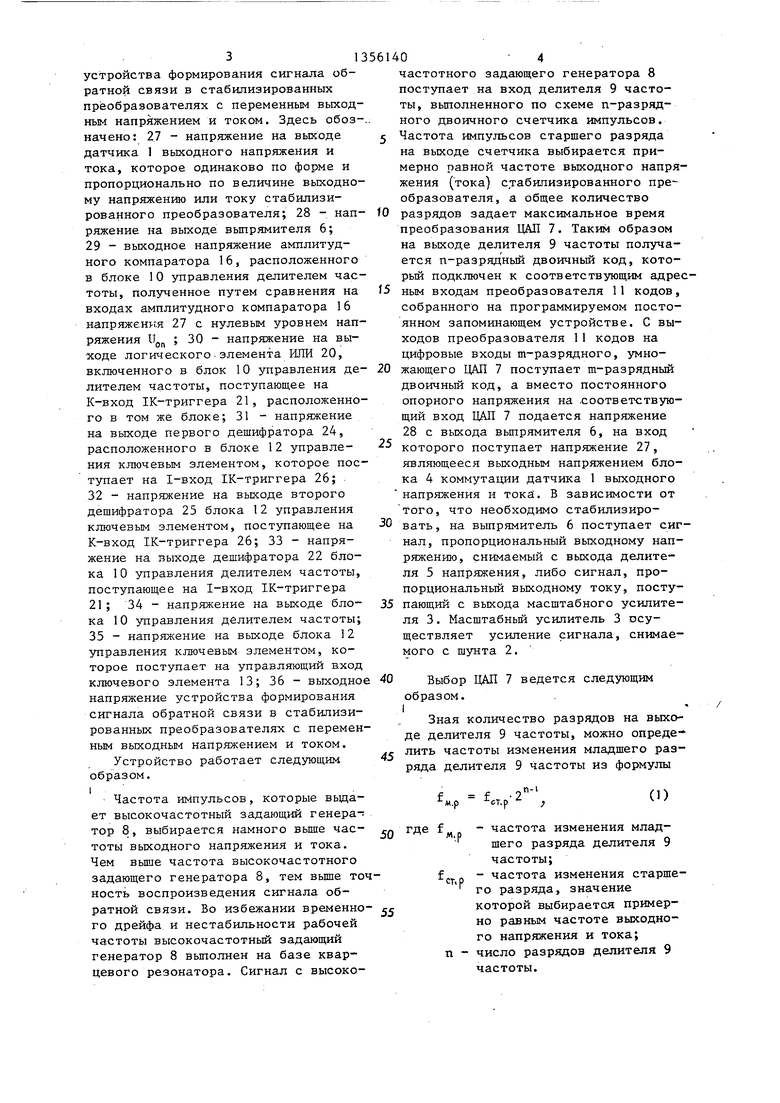

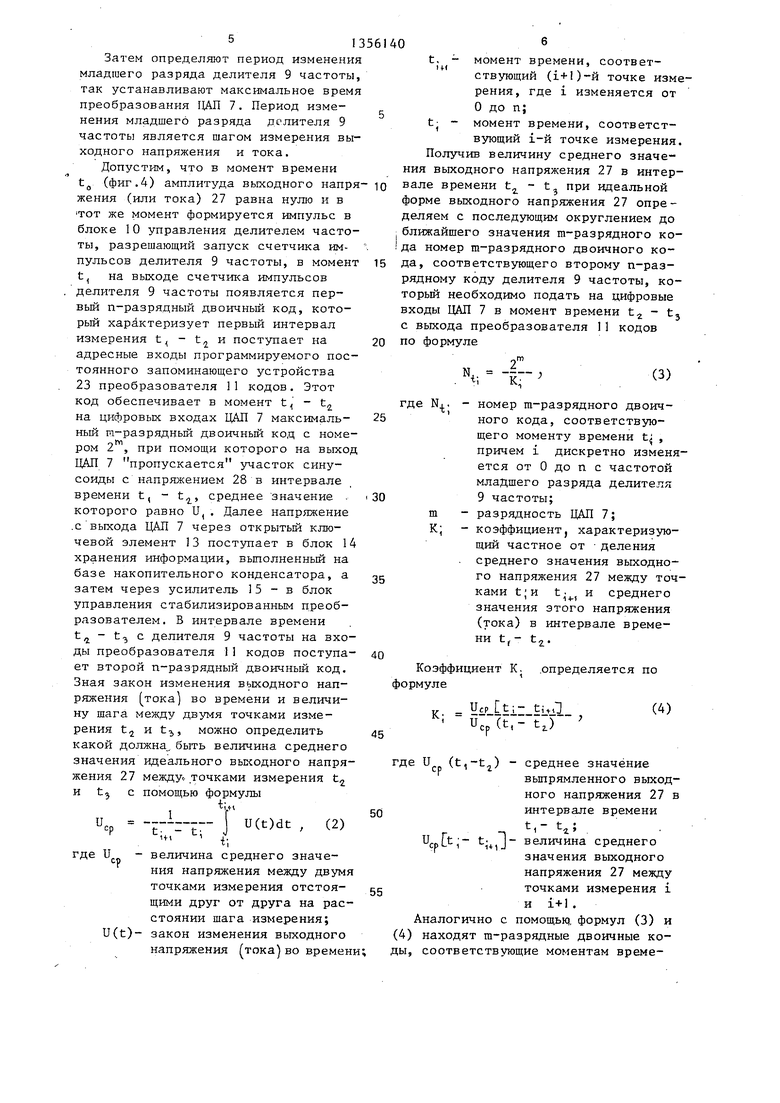

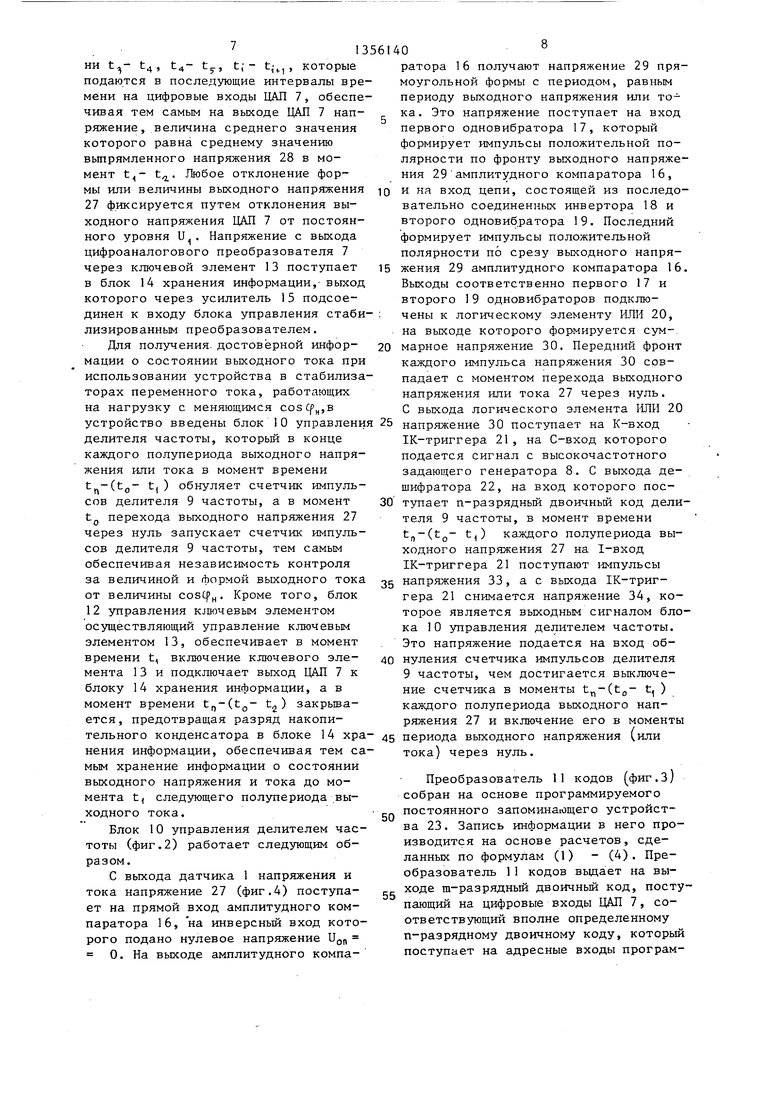

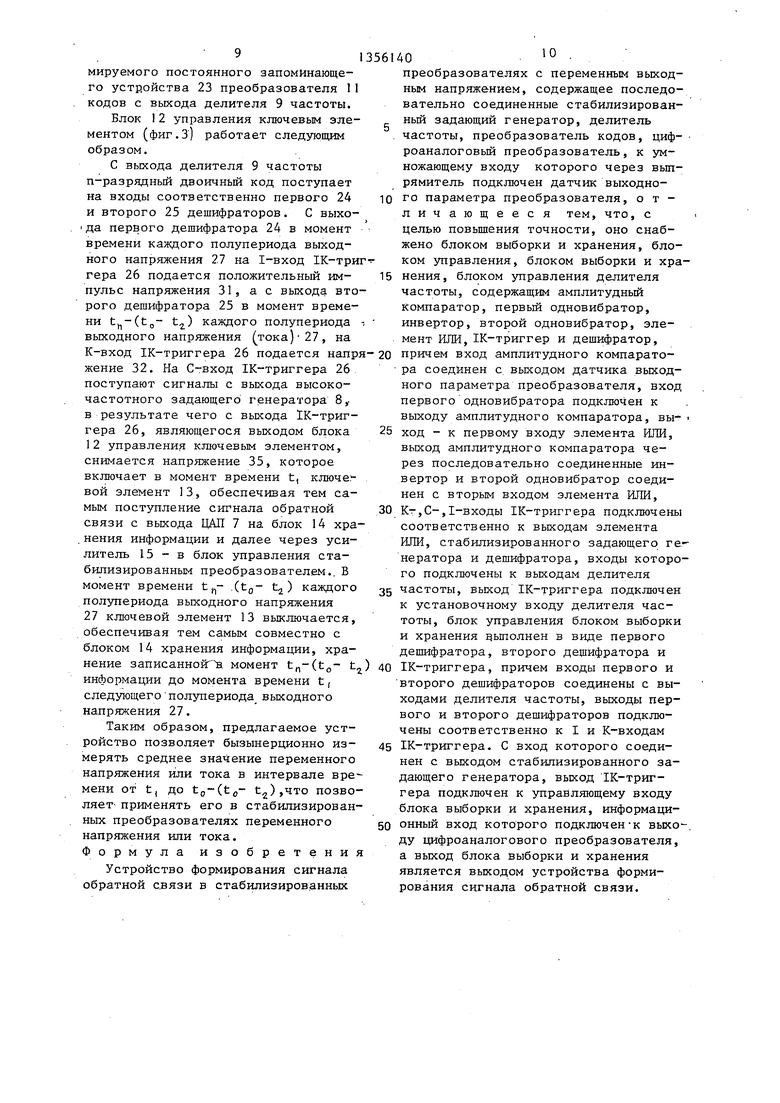

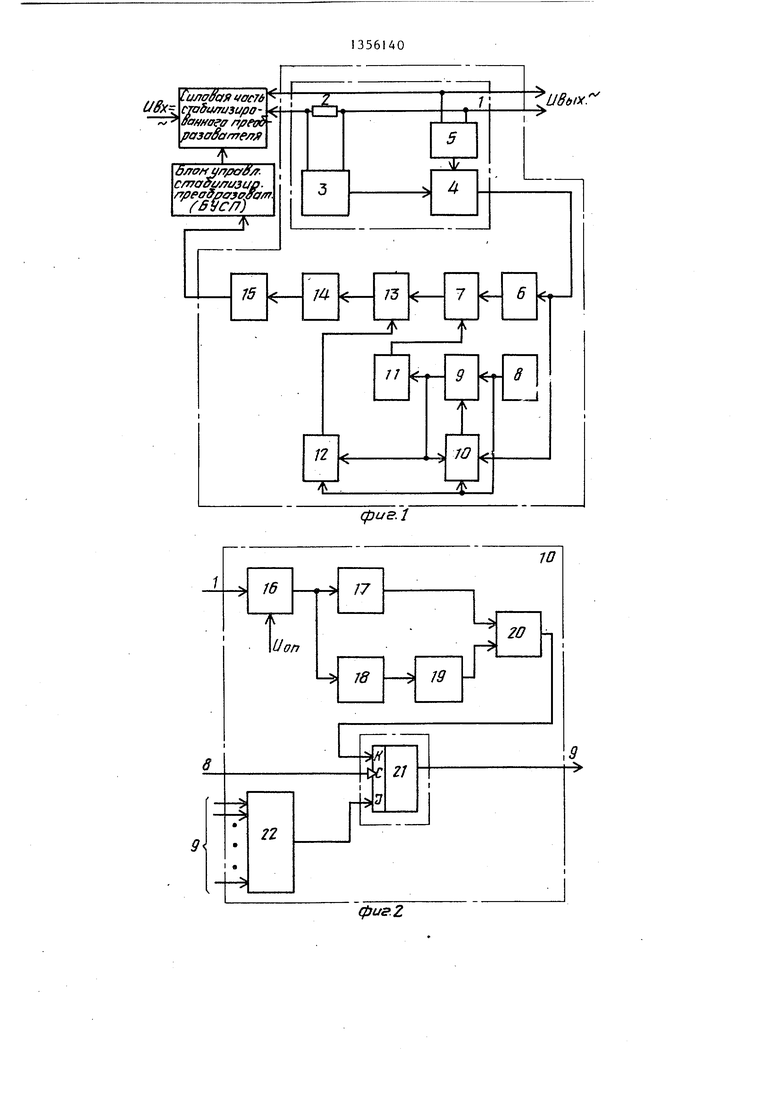

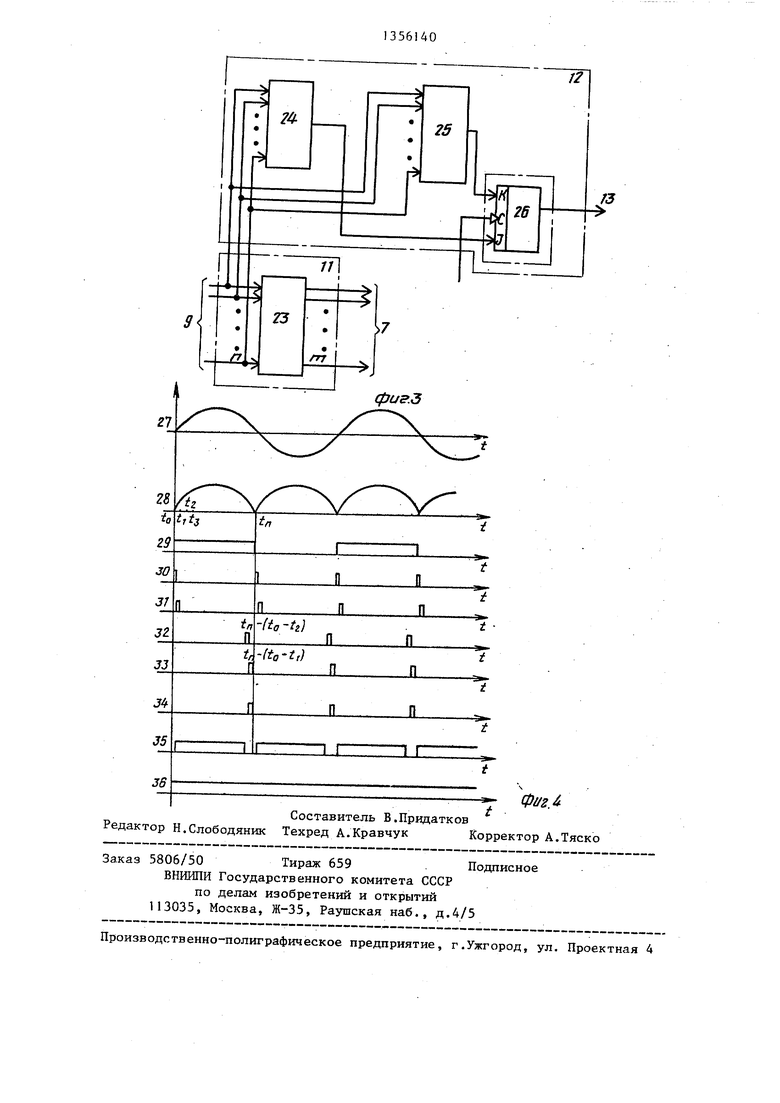

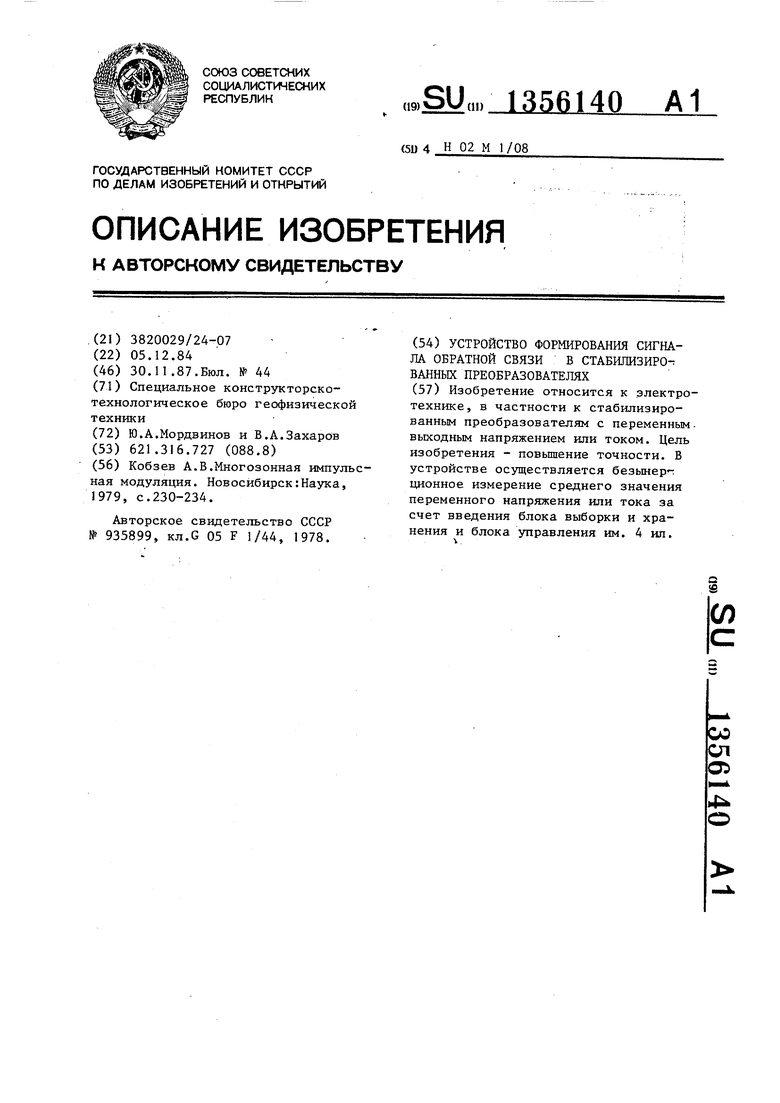

На фиг.I изображено устройство формирования сигнала обратной связи; нл фиг.2 - блок управления делителем частоты; на фиг.З - преобразователь кодов; на фиг.4 временные диаграммы работы устройства.

Устройство формирования сигнала обратной связи фиг.1 , вход которого подключен к выходу силовой части стабилизированного преобразователя, а выход - к блоку управления стабилизированным преобразователем, содержит датчик 1 выходного напряжения и тока, состоящий из шунта 2, включенного в силовую цепь нагрузки, мае-, штабного усилителя 3, входы которО го подключены к шунту 2, блока 4 коммутации, к входам которого подключены выходы масштабного усилителя 3 и делителя 5 напряжения,, вход которого подключен к выходным выводам силовой части стабилизированного преобразователя, выпрямитель 6, выход которого соединен- с первым входом цифроаналогового преобразователя ЦАП 7, а вход - с выходом блока 4 коммутации датчика I выходного напряжения и тока, высокочастотный задающий генератор 8, выходом подключенный к первому входу делителя 9 частоты, блок 10 управления дели-45 вьм элементом, содержащий первый телем частоты, входы которого соеди- дешифратор 24, входы которого под- нены соответственно с выходами делителя 9 4acTOTb j высокочастотного задающего генератора 8 и блока 4 комключ ены к выходу делителя 9 частоты второй дешифратора 25, входами под- ключенньй к выходу делителя 9 часто

мутации, датчика 1 выходного напряжения и тока, а выход - с вторым входом делителя 9 частоты, преобразователь 11 кодов, вход которого подключен к выходу делителя 9 частоты, а выход - к второму входу ЦАП 7, блок 12 управления ключевым элементом, подключенный своими вход ми соответственно к выходу делителя 9 частоты и выходу высокочастотного

задающего генератора 8, ключевой элемент 13, один вход которого соединен с выходом Ц/Ш 7, а второй - с выходом блока 12 управления ключевым элементом, блок 14 выборки и хранения информации, входом подключенный к выходу ключевого элемента 13, и усилитель 15, вход которого соединен с

выходом блока 14 выборки и хранения, а выход - с входом блока управления стабилизированным преобразователем.

Блок 10 управления делителем частоты фиг.2 содержит амплитудный

компаратор 16, вход которого подключен к выходу датчика 1 выходного напряжения и тока, первый одновибратор 17, входом соединенньй с выходом ам- плитудного компаратора 16, цепь из

последовательно соединенных инвертора 18 и второго одновибратора 19, вход которого подключен к выходу ам-- плитудного компаратора 16,, логический элемент ИЛИ 20, первый вход которого соединен с выходом первого одновибратора 17, а второй - с выходом цепи, состоящей из последовательно соединенных инвертора 18 и второго одновибратора 19, 1К-триггер 21, выходом подключенный к входу делителя 9 частоты, К-вход которого соединен с выходом логического элемента ИЛИ 20, С-вход с выходом высокочастотного задающего генератора 8,

а 1-вход - с выходом дешифратора 22, который входом подключен к выходу делителя 9 частоты.

На фиг.З представлены преобразователь 11 кодов, состоящий из программируемого постоянного запоминаюего устройства 23, которое своии входами подключено к выходу делителя 9 частоты, а выходами - к входу ЦАП 7, и блок 12 управления ключевьм элементом, содержащий первый дешифратор 24, входы которого под-

ключ ены к выходу делителя 9 частоты, второй дешифратора 25, входами под- ключенньй к выходу делителя 9 часто50

ты, и 1К-триггер 26, выход которого

соединен с входом ключевого элемента 13, 1-входом 1К-триггер 26 подключен к выходу первого дешифратора 24, С-входом - к выходу высокочастот- 25 ного задающего генератора 8, а К-вхо- дом - к выходу второго дешифратог ра 25.„

На фиг.4 изображены временные диаграммы на отдельных элементах

31

устройства формирования сигнала обратной связи в стабилизированных преобразователях с переменным выходным напряжением и током. Здесь обозначено: 27 - напряжение на выходе датчика 1 выходного напряжения и тока, которое одинаково по форме и пропорционально по величине выходному напряжению или току стабилизированного преобразователя; 28 - нап- ряжение на выходе выпрямителя 6; 29 - выходное напряжение амплитудного компаратора 16, расположенного в блоке 10 управления делителем частоты, полученное путем сравнения на входах амплитудного компаратора 16 напряжения 27 с нулевым уровнем напряжения UQI, ; 30 - напряжение на выходе логическогоэлемента ИЛИ 20, включенного в блок 10 управления де лителем частоты, поступающее на К-вход 1К-триггера 21, расположенного в том же блоке; 31 - напряжение на выходе первого дешифратора 24, расположенного в блоке 12 управле- ния ключевым элементом, которое поступает на 1-вход 1К-триггера 26; 32 - напряисение на выходе второго дешифратора 25 блока 12 управления ключевым элементом, поступающее на R-вход 1К-триггера 26; 33 - напряжение на выходе дешифратора 22 блока 10 управления делителем частоты, поступающее на 1-вход 1К-триггера 21; 34 - напряжение на выходе бло- ка 10 управления делителем частоты; 35 - напряжение на выходе блока 12 зшравления ключевым элементом, которое поступает на управляющий вход ключевого элемента 13; 36 - выходно напряжение устройства формирования сигнала обратной связи в стабилизированных преобразователях с переменным вькодным напряжением и током.

Устройство работает следующим образом.

I

Частота импульсов, которые вьщает высокочастотный задающий генератор 8, выбирается намного вьшге час- тоты выходного напряжения и тока. Чем вьше частота высокочастотного задающего генератора 8, тем вьшзе тоность воспроизведения сигнала обратной связи. Во избежании временно го дрейфа и нестабильности рабочей частоты высокочастотный задающий генератор 8 выполнен на базе кварцевого резонатора. Сигнал с высоко

0 4

частотного задающего генератора 8 поступает на вход делителя 9 частоты, выполненного по схеме п-разряд- ного двоичного счетчика импульсов. Частота импульсов старшего разряда на выходе счетчика выбирается примерно равной частоте выходного напряжения (тока) стабилизированного пре образователя, а общее количество разрядов задает максимальное время преобразования ЦАП 7. Таким образом на выходе делителя 9 частоты получается п-разрядный двоичный код, который подключен к соответствующим адресным входам преобразователя П кодов, собранного на программируемом постоянном запоминающем устройстве. С выходов преобразователя 11 кодов на цифровые входы т-разрядного, умножающего ЦАП 7 поступает т-разрядный двоичный код, а вместо постоянного опорного напряжения на .соответствующий вход ЦАП 7 подается напряжение 28 с выхода выпрямителя 6, на вход которого поступает напряжение 27, являющееся выходным напряжением блока 4 коммутации датчика 1 выходного

напряжения и тока. В зависимости от того, что необходимо стабилизировать, на выпрямитель 6 поступает сигнал, пропорциональный выходному напряжению, снимаемый с выхода делителя 5 напряжения, либо сигнал, пропорциональный выходному току, поступающий с выхода масштабного усилителя 3. Масштабньй усилитель 3 осуществляет усиление сигнала, снимаемого с шунта 2.

Выбор ЦАП 7 ведется следующим

образом. I

Зная количество разрядов на выходе делителя 9 частоты, можно определить частоты изменения младшего разряда делителя 9 частоты из формулы

-м.р

fcT.p-2

n-i

(О

де f - частота изменения младшего разряда делителя 9 частоты;

f (... р - частота изменения старше- го разряда, значение

которой выбирается примерно равным ча стоте выходного напряжения и тока; п - число разрядов делителя 9 частоты.

513

Затем определяют период изменения младшего разряда делителя 9 частоты, так устанавливают максимальное время преобразования ЦАП 7. Период изменения младшего разряда делителя 9 частоты является шагом измерения выходного напряжения и тока.

Допустим, что в момент времени tg (фиг,4) амплитуда выходного напря- жения (или тока) 27 равна нулю и в ТОТ же момент формируется импульс в блоке 10 управления делителем частоты, разрешающий запуск счетчика импульсов делителя 9 частоты, в момент t

., на выходе счетчика импульсов делителя 9 частоты появляется первый п-разрядный двоичный код, который характеризует первый интервал

измерения

t, t и поступает на

адресные входы программируемого постоянного запоминающего устройства 23 преобразователя 11 кодов. Этот код обеспечивает в момент t - t на цифровых входах ЦАП 7 максимальный т-разрядный двоичньй код с номепГЛ

ром 2 , при помощи которого на выход ЦАП 7 пропускается участок синусоиды с напряжением 28 в интервале времени t, - t, среднее значение . которого равно U,, Далее напряжение .с выхода ЦДЛ 7 через открытый ключевой элемент 13 поступает в блок 14 хранения информации, вьтолненный на базе накопительного конденсатора, а затем через усилитель 15 - в блок управления стабилизированным преобразователем. В интервале времени t - t с делителя 9 частоты на входы преобразователя 11 кодов поступает второй п-разрядный двоичный код. Зная закон изменения вькодного напряжения тока во времени и величину шага между двумя точками измерения tj и t, можно определить какой должна,, быть величина среднего значения идеального выходного напряжения 27 между точками измерения ty

tj

Р де и

с помош;ью формулы

I г --

н, /.

t l

(2)

Р

величина среднего значения напряжения между двумя точками измерения отстоя- ш;ими друг от друга на расстоянии шага измерения; U(t)- закон изменения выходного

напряжения тока)во времени;

6

5

0

t, it(

момент времени, соответствующий (1+1)-й точке измерения, где i изменяется от О до п;

t - момент времени, соответствующий 1-й точке измерения. Получив величину среднего значения выходного напряжения 27 в интервале времени t - t при идеальной форме выходного напряжения 27 определяем с последующим округлением до ближайшего значения т-разрядного кода номер т-разрядного двоичного кода, соответствующего второму п-раз- рядному коду делителя 9 частоты, который необходимо подать на цифровые входы ЦАП 7 в момент времени t - tj с выхода преобразователя 11 кодов по формуле

i; -к

(3)

5

где N.

0

m к;

5

номер т-разрядного двоичного кода, соответствую- ш;его моменту времени t , причем i дискретно изменяется от О до п с частотой младшего разряда делителя 9 частоты; разрядность ЦАП 7; коэффициент, характеризующий частное от деления среднего значения выходного напряжения 27 между точками t;и и среднего значения зтого напряжения (тока) в интервале времени

tr40

Коэффициент К. формуле

.определяется по

0

5

5

„ ycpjt;- tu,

- и:„а7- tj

(4)

где и

ср

ср (t,-t,)

среднее значение вьптрямленного выходного напряжения 27 в интервале времени

ti- 45 . Uj-ft - t.j J- величина среднего

значения выходного напряжения 27 между точками измерения i и 1+ .

Аналогично с помош,ьк, формул (3) и (4) находят т-разрядные двоичные коды, соответствующие моментам времени

Ц-4

t4- tj., t; - t ,, , которые подаются в последующие интервалы времени на цифровые входы ЦАП 7, обеспечивая тем самьм на выходе ДАЛ 7 напряжение, величина среднего значения которого равна среднему значению вьтрямленного напряжения 28 в момент. Любое отклонение формы или величины выходного напряжения 27 фиксируется путем отклонения выходного напряжения ЦАП 7 от постоянного уровня и. Напряжение с выхода цифроаналогового преобразователя 7 через ключевой элемент 13 поступает в блок 14 хранения информации,- выход которого через усилитель 15 подсоединен к входу блока управления стабилизированным преобразователем.

Для получения, достоверной информации о состоянии выходного тока при использовании устройства в стабилизаторах переменного тока, работающих на нагрузку с меняющимся созС,в

10 и на вход цепи, состоящей из после вательно соединенных инвертора 18 второго одновиб.ратора 19. Последни формирует импульсы положительной полярности по срезу выходного напр

15 жения 29 амплитудного компаратора Выходы соответственно первого 17 и второго 19 одновибраторов подклю чены к логическому элементу 1-ШИ 20 на выходе которого формируется сум

20 марное напряжение 30. Передний фро каждого импульса напр51жения 30 сов падает с моментом перехода выходно напряжения или тока 27 через нуль. С выхода логического элемента 1-ШИ

устройство введены блок 1 О управления 25 напряжение 30 поступает на К-вход

делителя частоты, которьи в конце каждого полупериода выходного напряжения или тока в момент времени (tg- t, ) обнуляет счетчик импульсов делителя 9 частоты, а в момент tg перехода выходного напряжения 27 через нуль запускает счетчик импульсов делителя 9 частоты, тем самым обеспечивая независимость контроля за величиной и формой выходного тока от величины coscp. Кроме того, блок 12 управления ключевым элементом осуществляющий управление ключевым элементом 13, обеспечивает в момент времени t, включение ключевого элемента 13 и подключает выход ПАП 7 к блоку 14 хранения информации, а в момент времени закрьша- ется, предотвращая разряд накопи1К-триггера 21, на С-вход которого подается сигнал с высокочастотного задающего генератора 8. С выхода д шифратора 22, на вход которого пос

30 тупает п-разрядньш двоичный код де теля 9 частоты, в момент времени t|,-(tQ- t,) каждого полупериода в ходного напряжения 27 на 1-вход 1К-триггера 21 поступают импульсы

35 напряжения 33, а с выхода 1К-триг- гера 21 снимается напряжение 34, к торое является выходным сигналом б ка 10 управления делителем частоты Это напряжение подается на вход об

40 нуления счетчика импульсов делител 9 частоты, чем достигается выключ ние счетчика в моменты t, каждого полупериода выходного нап ряжения 27 и включение его в момен

тельного конденсатора в блоке 14 хра- 45 периода выходного напряжения (или нения информации, обеспечивая тем са- тока) через нуль, мым хранение информации о состоянии

и

выходного напряжения и тока до момента t, следующего полупериода выходного тока.

Блок 10 управления делителем частоты (фиг.2) работает следующим образом.

С выхода датчика 1 напряжения и тока напряжение 27 (фиг.4) поступает на прямой вход амплитудного компаратора 16, на инверсный вход которого подано нулевое напряжение 0. На выходе амплитудного компа50

55

Преобразователь 11 кодов (фиг. собран на основе программируемого постоянного запоминающего устройс ва 23. Запись информации в него п изводится на основе расчетов, сде ланных по формулам (1) - (4). Пр образователь 11 кодов вьщает на в ходе т-разрядный двоичньш код, по пающий на цифровые входы ЦАП 7, с ответствующий вполне определенном п-разрядному двоичному коду, кото поступает на адресные входы прогр

ратора 16 получают напряжение 29 прямоугольной формы с периодом, равным периоду выходного напряжения или тока. Это напряжение поступает на вход первого одновибратора 17, который формирует импульсы положительной полярности по фронту выходного напряжения 29 амплитудного компаратора 16,

и на вход цепи, состоящей из последовательно соединенных инвертора 18 и второго одновиб.ратора 19. Последний формирует импульсы положительной полярности по срезу выходного напряжения 29 амплитудного компаратора 16. Выходы соответственно первого 17 и второго 19 одновибраторов подключены к логическому элементу 1-ШИ 20, на выходе которого формируется суммарное напряжение 30. Передний фронт каждого импульса напр51жения 30 совпадает с моментом перехода выходного напряжения или тока 27 через нуль. С выхода логического элемента 1-ШИ 20

1К-триггера 21, на С-вход которого подается сигнал с высокочастотного задающего генератора 8. С выхода дешифратора 22, на вход которого поступает п-разрядньш двоичный код делителя 9 частоты, в момент времени t|,-(tQ- t,) каждого полупериода выходного напряжения 27 на 1-вход 1К-триггера 21 поступают импульсы

напряжения 33, а с выхода 1К-триг- гера 21 снимается напряжение 34, которое является выходным сигналом блока 10 управления делителем частоты. Это напряжение подается на вход обнуления счетчика импульсов делителя 9 частоты, чем достигается выключение счетчика в моменты t, ) каждого полупериода выходного напряжения 27 и включение его в моменты

периода выходного напряжения (или тока) через нуль,

ериода выходного напряжения (или тока) через нуль,

Преобразователь 11 кодов (фиг.З) собран на основе программируемого постоянного запоминающего устройства 23. Запись информации в него производится на основе расчетов, сделанных по формулам (1) - (4). Преобразователь 11 кодов вьщает на выходе т-разрядный двоичньш код, поступающий на цифровые входы ЦАП 7, соответствующий вполне определенному п-разрядному двоичному коду, который поступает на адресные входы програм91

мируемого постоянного запоминающего устройства 23 преобразователя 1I кодов с выхода делителя 9 частоты.

Блок 12 управления ключевым элементом (фиг.З работает следующим образом.

С выхода делителя 9 частоты п-разрядный двоичный код поступает на входы соответственно первого 24 и второго 25 дешифраторов. С выхо- I да первого дешифратора 24 в момент времени каждого полупериода выходного напряжения 27 на 1-вход IK-триг гера 26 подается положительный им- пульс напряжения 31, ас выхода второго дешифратора 25 в момент времени t)-(to- t) каждого полупериода выходного напряжения (тока)-27, на К-вход 1К-триггера 26 подается напря жение 32. На С-вход 1К-триггера 26 поступают сигналы с выхода высокочастотного задающего генератора 8,. в результате чего с выхода 1К-триг- гера 26, являющегося выходом блока 12 управления ключевым элементом, снимается напряжение 35, которое включает в момент времени t, ключе. - вой элемент 13, обеспечивая тем самым поступление сигнала обратной связи с выхода ЦАП 7 на блок 14 хра- .нения информации и далее через усилитель 15 - в блок управления ста- бипизированньм преобразователем., В момент времени t - .(tg- Ц ) каждого полупериода выходного напряжения 27 ключевой элемент 13 выключается, обеспечивая тем самым совместно с блоком 14 хранения информации, хранение записанной: момент tf,-(t,- ц информации до момента времени t, следующего полупериода выходного напряжения 27.

Таким образом, предлагаемое устройство позволяет бызынерционно из- мерять среднее значение переменного напряжения или тока в интервале времени от t, до to-(t(,- t2),4To позволяет- применять его в стабилизированных преобразователях переменного напряжения или тока. Формула изобретения

Устройство формирования сигнала обратной связи в стабилизированных

40

10

преобразователях с переменным выходным напряжением, содержащее последовательно соединенные стабилизированный задающий генератор, делитель частоты, преобразователь кодов, циф- роаналоговый преобразователь, к умножающему входу которого через вьт- рямитель подключен датчик выходного параметра преобразователя, отличающееся тем, что, с I целью повьш1ения точности, оно снабжено блоком выборки и хранения, блоком управления, блоком выборки и хранения, блоком управления делителя частоты, содержащим амплитудный Компаратор, первый одновибратор, инвертор, второй одновибратор, эле- мент ИЛИ, 1К-триггер и дешифратор, причем вход амплитудного компаратора соединен с. выходом датчика выходного параметра преобразователя, вход первого одновибратора подключен к выходу амплитудного компаратора, вы- ход - к первому входу элемента ИЛИ, вькод амплитудного компаратора через последовательно соединенные инвертор и второй одновибратор соединен с вторым входом элемента ИЛИ, К-,С-,1-входы 1К-триггера подключены соответственно к выходам элемента ИЛИ, стабилизированного задающего ге-- нератора и дешифратора, входы которого подключены к выходам делителя частоты, выход 1К-триггера подключен к установочному входу делителя частоты, блок управления блоком выборки и хранения выполнен в виде первого дешифратора, второго дешифратора и 1К-триггера, причем входы первого и

второго дешифраторов соединены с выходами делителя частоты, выходы первого и второго дешифраторов подключены соответственно к I и К-входам 1К-триггера. С вход которого соединен с выходом стабилизированного задающего генератора, выход 1К-триг- гера подключен к управляющему входу блока выборки и хранения, информационный вход которого подключен К вько-. ду цифроаналогового преобразователя, а выход блока выборки и хранения является выходом устройства формирования сигнала обратной связи.

(pus.l

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор спектрометрических импульсов | 1986 |

|

SU1325671A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАЧАЛЬНЫХ МОМЕНТОВ ЛЮБОГО ПОРЯДКА | 1991 |

|

RU2041496C1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой веберметр | 1986 |

|

SU1368832A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

Изобретение относится к электротехнике, в частности к стабилизированным преобразователям с переменным, выходным напряжением или током. Цель изобретения - повьппение точности. В устройстве осуществляется безьшер г ционное измерение среднего значения переменного напряжения или тока за счет введения блока выборки и хранения и блока управления им. 4 ил. V 00 СП О5 4 О

фиг.г

| Кобзев А.В.Многозонная импульсная модуляция | |||

| Новосибирск:Наука, 1979, с.230-234 | |||

| Стабилизатор переменного напряжения | 1979 |

|

SU935899A1 |

Авторы

Даты

1987-11-30—Публикация

1984-12-05—Подача