Изобретение относится к радиотехнике и может быть использовано для формирования амплитудно-модулирован- ных сигналов с подавленной несущей частотой при построении радиопередатчиков с однополосной модуляцией и в измерительной технике при постр : ен-як образцовых мер переменного напр.тже- ния.

Цель изобретения - расширение диапазона рабочих частот.

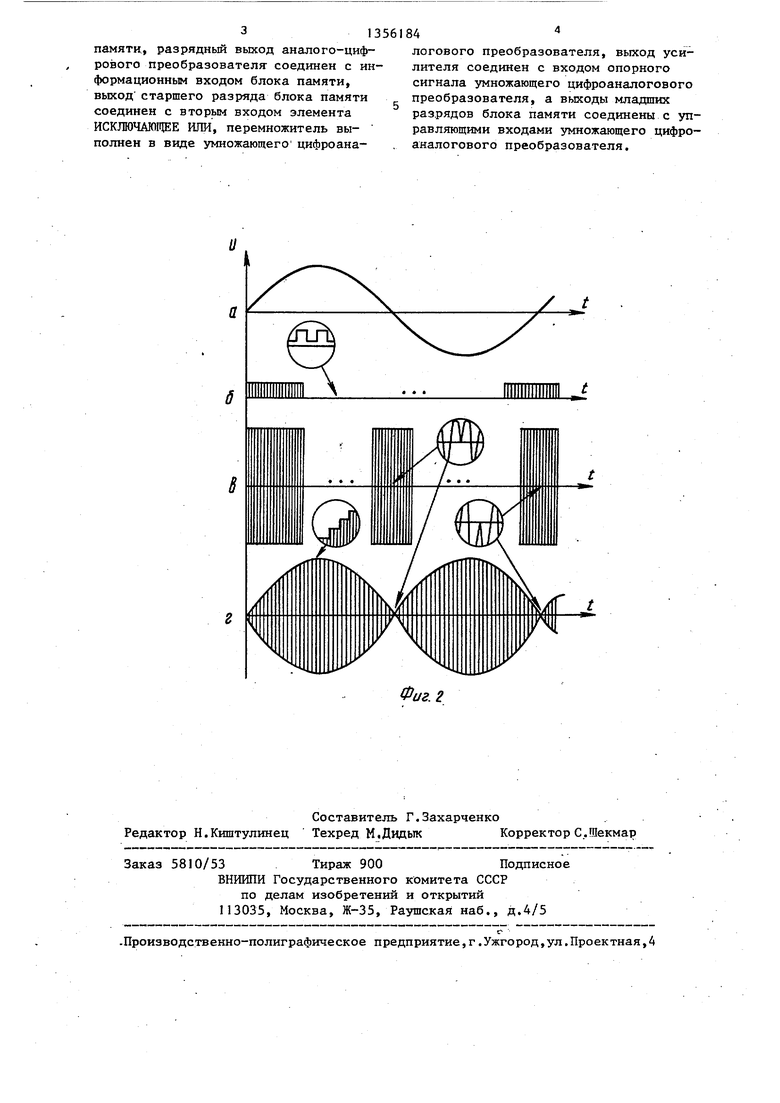

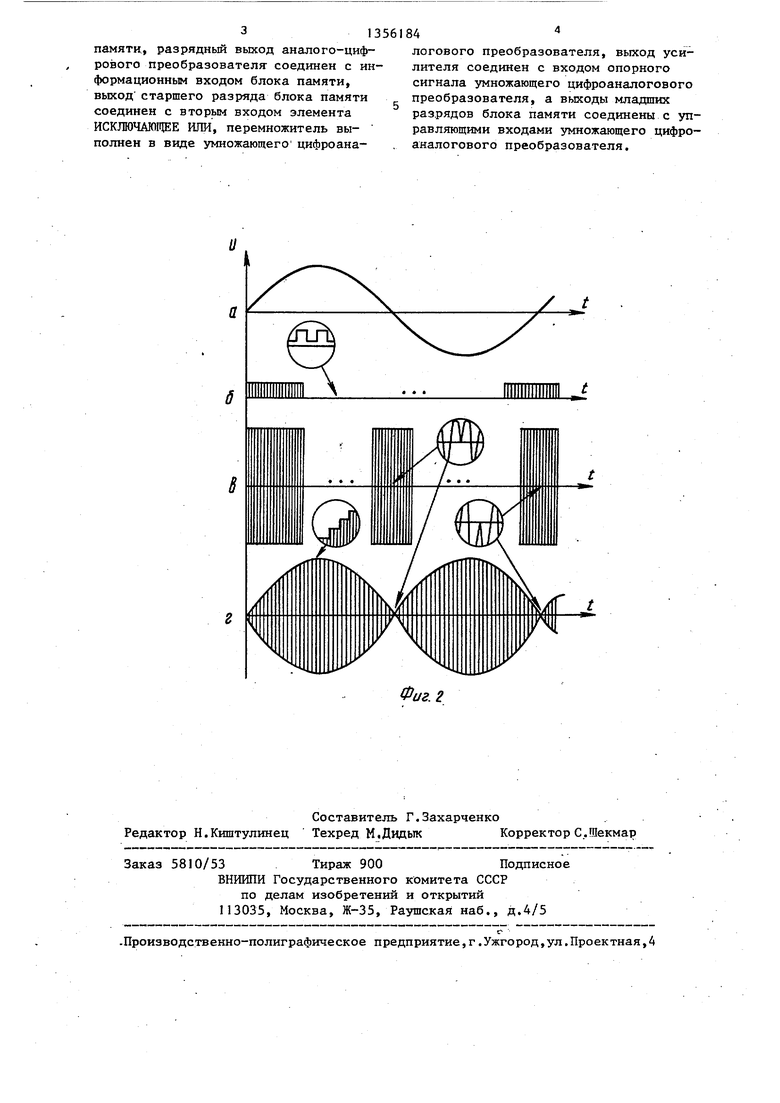

На фиг.1 представлена структурная электрическая схема предлагаемого балансного модулятора; на фиг.2 - временные диаграммы его работы.

Балансный модулятор содержит источник 1 модулирующих сигналов, аналого-цифровой преобразователь (АЦП) 2, блок 3 памяти,перемножитель в виде . умножающего цифроаналогового преобразователя (ЦАЦ) 4, источник 5 модулируемых сигналов, счетчик 6 импульсов, элемент ИСКЛЮЧАЩЕЕ РШИ 7, усилитель 8.

Балансный модулятор работает сле- :дующим образом.

; Низкочастотное модулирующее колебание предварительно преобразуется в цифровую форму, т.е. дискретизиру- ется по времени и квантуется по амплитуде, причем частота дискретиза- хщи может быть, согласно теореме Ко- тельникова, только в два раза вьщ1е верхней частоты спектра модулирующего колебания. Перемножение - изменение амплитуды модулируемого сигнала (несущей частоты) по закону изменения модулирующего сигнала - производится умножающим ЦАЛ 4. Подавление несущей частоты определяется аддитивной частотно-зависимой составляющей погрещности умножающего ЦАП 4 т.е. пролазом несущей на выход при цифровом коде управления ГЩТ 4, состоящем из О во всех разрядах.

Источник 1 модулирующих сигналов формирует сигнал с верхней частотой F (фиг.2а), источник 5 модулируемых сигналов - импульсы с частотой f (фиг.26). С приходом очередного импульса с выхода счетчика импульсов 6 АЦП 2 начинает процесс преобразования сигнала источника 1 в цифровой код. По окончании процесса преобразования на выходе сигнала готовности информации АЦП 2 формируется импульс готовности информации (конца преобразования) . Этим импульсом информация

с выхода А1Щ 2 записьгаается в блок 3 памяти. Соответственно записанному в блоке 3 памяти модулю (абсолютной величине) кода изменяется коэффициент передачи умножающего ЦАП 4. Старший (знаковый) разряд преобразованного кода блока 3 памяти устанавливает состояние элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Если старший разряд блока 3 памяти находится в состоянии О (положительная полярность сигнала источника 1), то выходной сигнал элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 совпадает по фазе с сигналом источника 5. В противном случае, если старший разряд блока 3 памяти находится в состоянии 1 (отрицательная полярность сигнала источника 1), элемент ИСКЛЮЧАИЦЕЕ ИЛ1-1 7 инвертирует сигнал источника 5, т.е. сдвигает его на 180 . Фазоманипулированный таким образом сигнал после усилителя 8 (фиг.2в) поступает на вход опорного сигнала

умножающего ЦАП 4. В соответствии с установленным коэффициентом передачи умножающего ЦАП 4 этот сигнал поступает на выход балансного модулятора. Таким образом, на выходе балансного

модулятора формируется колебание, амплитуда которого пропорциональна величине сигнала источника 1, а фаза зависит от полярности этого сигнала (фиг.2г), в котором отсутствует несущее колебание.

Формула изобретения

Балансньш модулятор, содержащий

40 источник модулируемого сигнала, источник модулирующих сигналов, блок памяти и перемножитель, отличающийся тем, что, с целью расширения диапазона рабочих частот,

45 в него введены аналого-цифровой преобразователь, информационный вход которого соединен с выходом источника модулирующих сигналов, счетчик им- пульсов, вход которого соединен с вы

gQ ходом источника модулируемых сигналов, а выход - с входом запуска аналого-цифрового преобразователя, последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого

g соединен с вькодом источника модулируемых сигналов, и усилитель, при . этом выход сигнала готовности информации аналого-цифрового преобразователя со единен с входом записи блока

313561

памяти, разрядный выход аналого-цифрового преобразователя соединен с информационным входом блока памяти, выход старшего разряда блока памяти соединен с вторьм входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, перемножитель вы- полнен в виде умножающего цифроана84

логового преобразователя, выход усилителя соединен с входом опорного сигнала умножающего цифроаналогового преобразователя, а выходы младших разрядов блока памяти соединены с управляющими входами умножающего цифро- аналогового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Широкополосная система связи | 1985 |

|

SU1401625A1 |

| СВЧ-амплифазометр | 1986 |

|

SU1350627A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280698A1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| Устройство для измерения диаграммы направленности антенны | 1981 |

|

SU1163284A1 |

| СПОСОБЫ И УСТРОЙСТВА ПОВЫШЕНИЯ ИНДЕКСА УГЛОВОЙ МОДУЛЯЦИИ | 2012 |

|

RU2493646C2 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Система связи с относительной фазовой и фазоимпульсной модуляцией | 1987 |

|

SU1559421A1 |

| Преобразователь угла поворота вала с контролем выходного кода | 1986 |

|

SU1334373A2 |

Изобретение относится к радиотехнике и обеспечивает расширение диапазона рабочих частот. Балансный модулятор содержит источник 1 моду- лрфующих сигналов, А1Щ 2, блок памяти (БП) 3, перемножитель в виде умножающего ЦАП 4,, источник 5 модулируемых сигналов, счетчик импульсов 6, злемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, усилитель 8. Счетчик импульсов 6 задает интервал преобразования сигнала источника 1 в цифровой код. Преобразованная А1Щ 2 информация записбшается в БП 3. В соответствии с модулем записанного кода изменяется коэф.передачи умножающего ЦАП 4. Старший (знаковый) разряд кода устанавливает состояние элемента ИСКЛЮЧАЩЕЕ ИЛИ 7. При положит.полярности сигнала источника 1 старший разряд кода нулевой, что обеспечивает совпадение по фазе выходного сигнала элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 с сигналом источника 5.При отриц. полярности сигнала источника i 1 осуществляется сдвиг сигнала источника 5 по фазе на 180. Фазоманипулирован- ный сигнал преобразуется в умножающем ПДП 4 в соответствии с установленным коэф. передачи. Амплитуда выходного сигнала балансного модулятора пропорциональна сигналу источника 1, а фаза зависит от полярности этого сигнала, в котором отсутствует несущее колебание. 2 ил. (Л а и. бык со сл 05 ЭО 4

/ t

Фиг. 2

| Балансный модулятор | 1981 |

|

SU1019581A1 |

Авторы

Даты

1987-11-30—Публикация

1985-10-03—Подача