00 СП

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сейсмических, гидроакустических и других сигналов.

Цель изобретения - упрощение устройства за счет упрощения блока формирования адресов -записи.

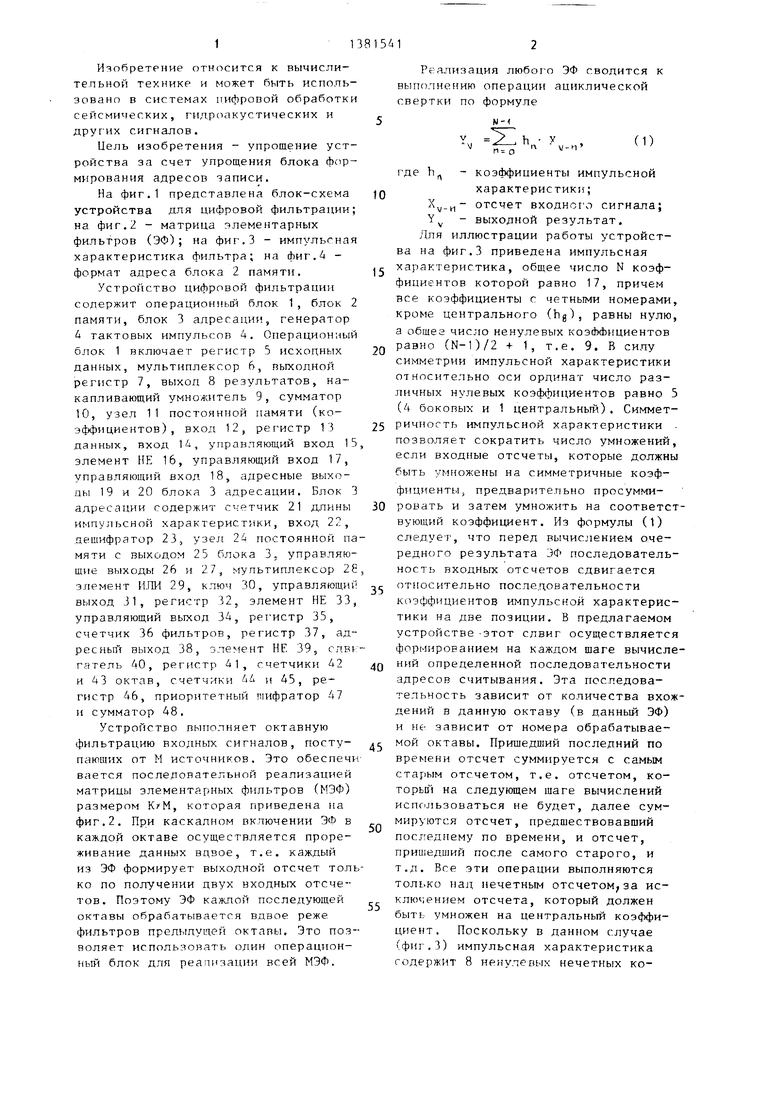

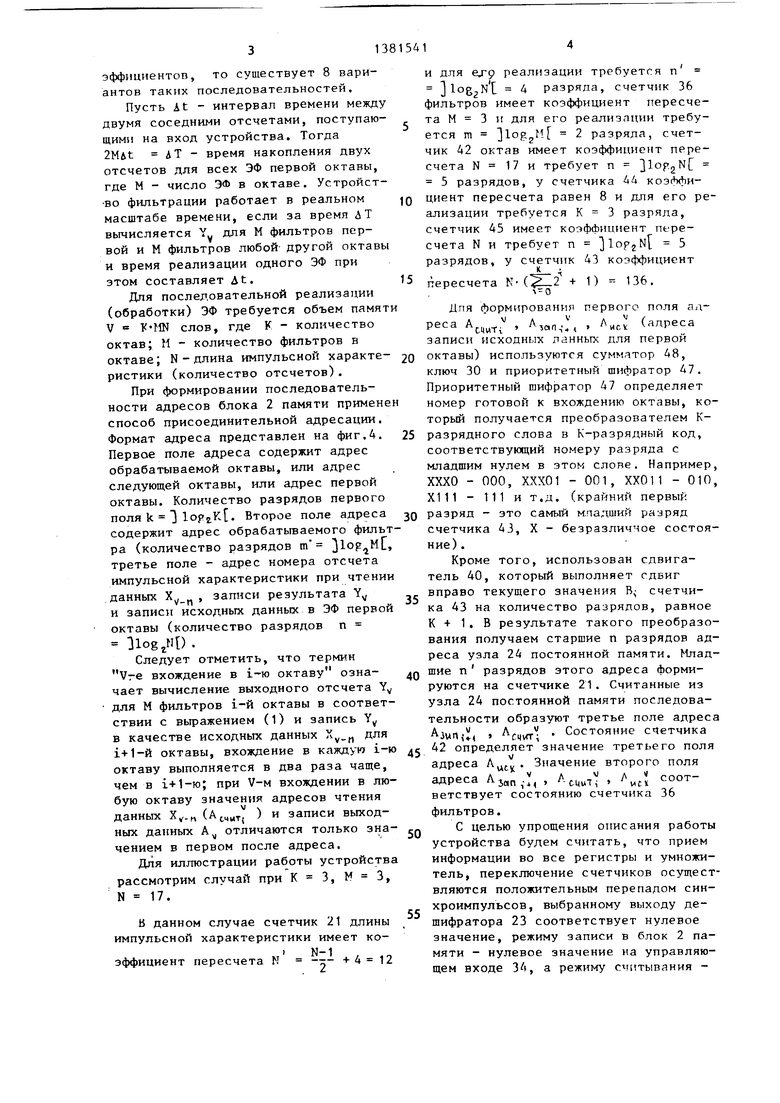

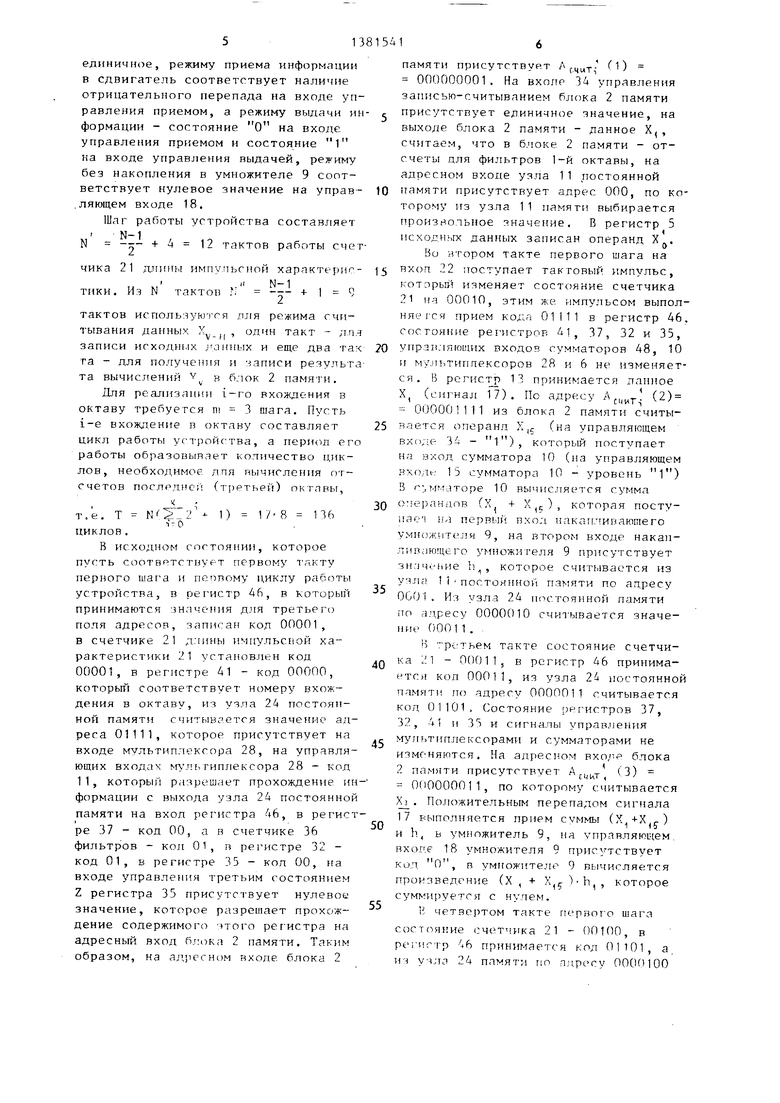

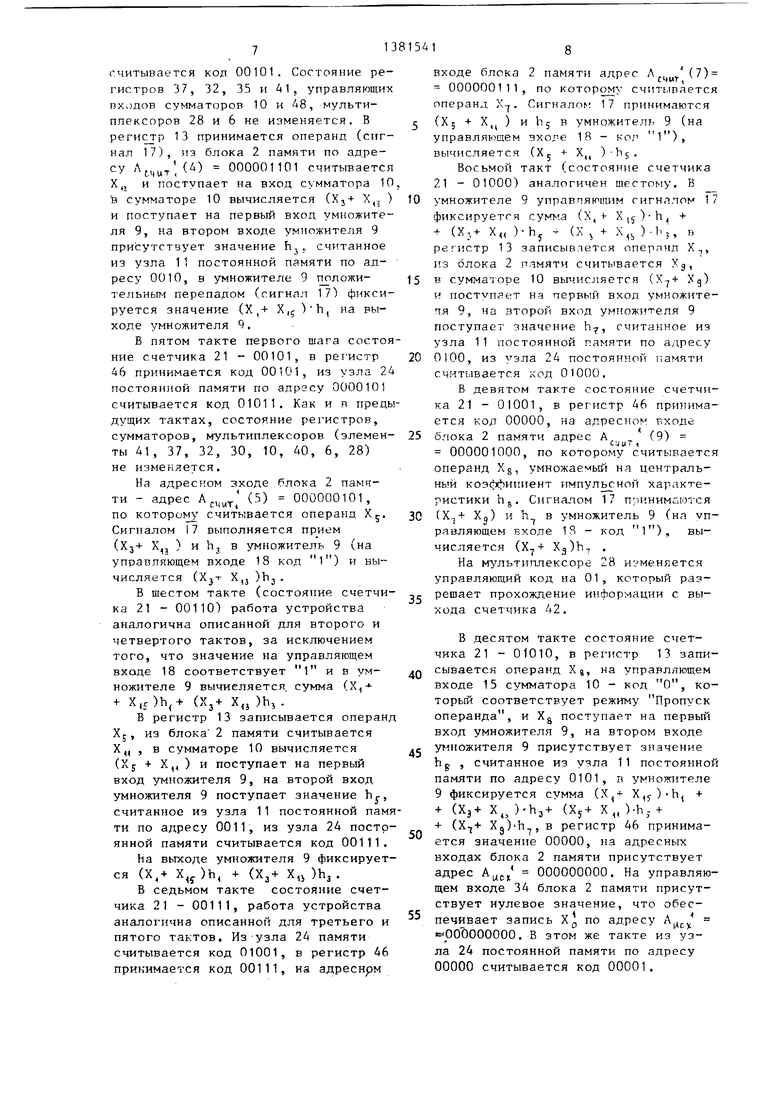

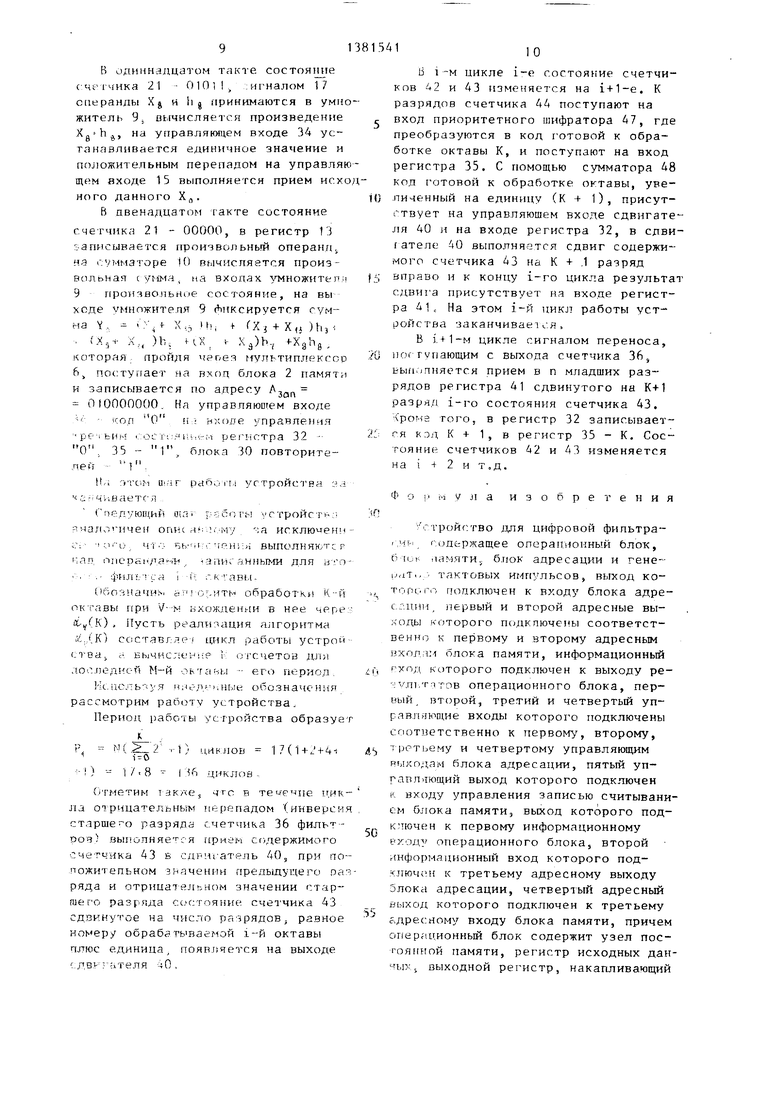

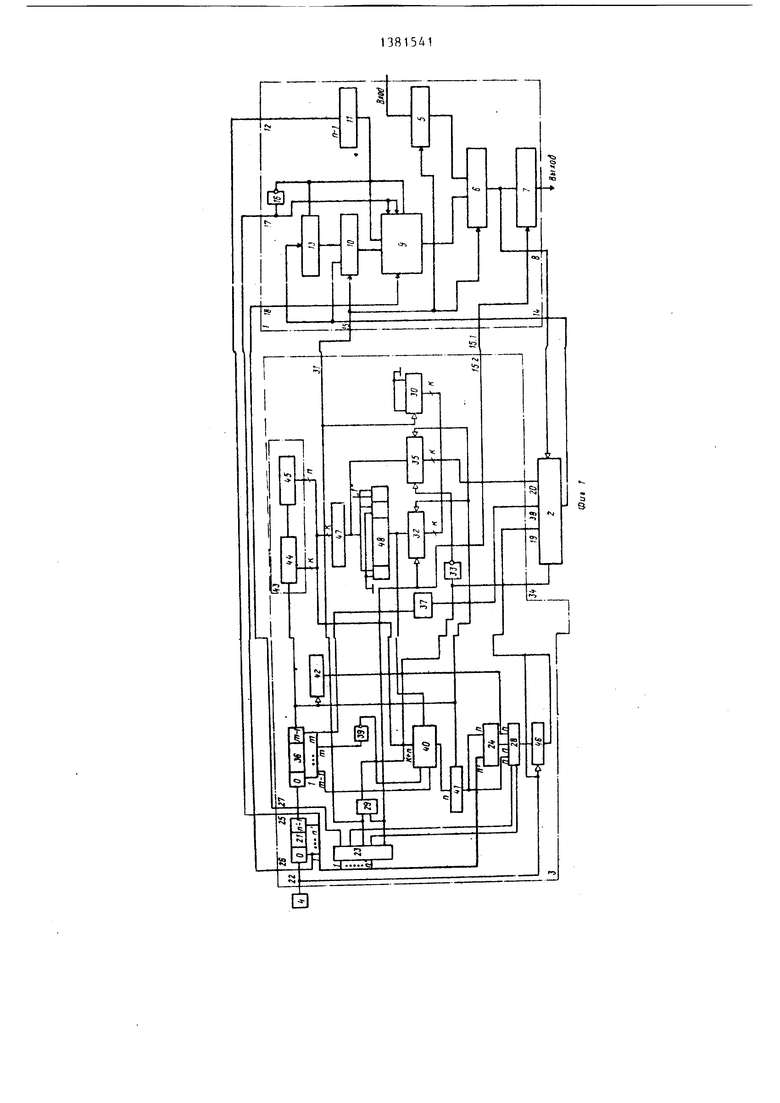

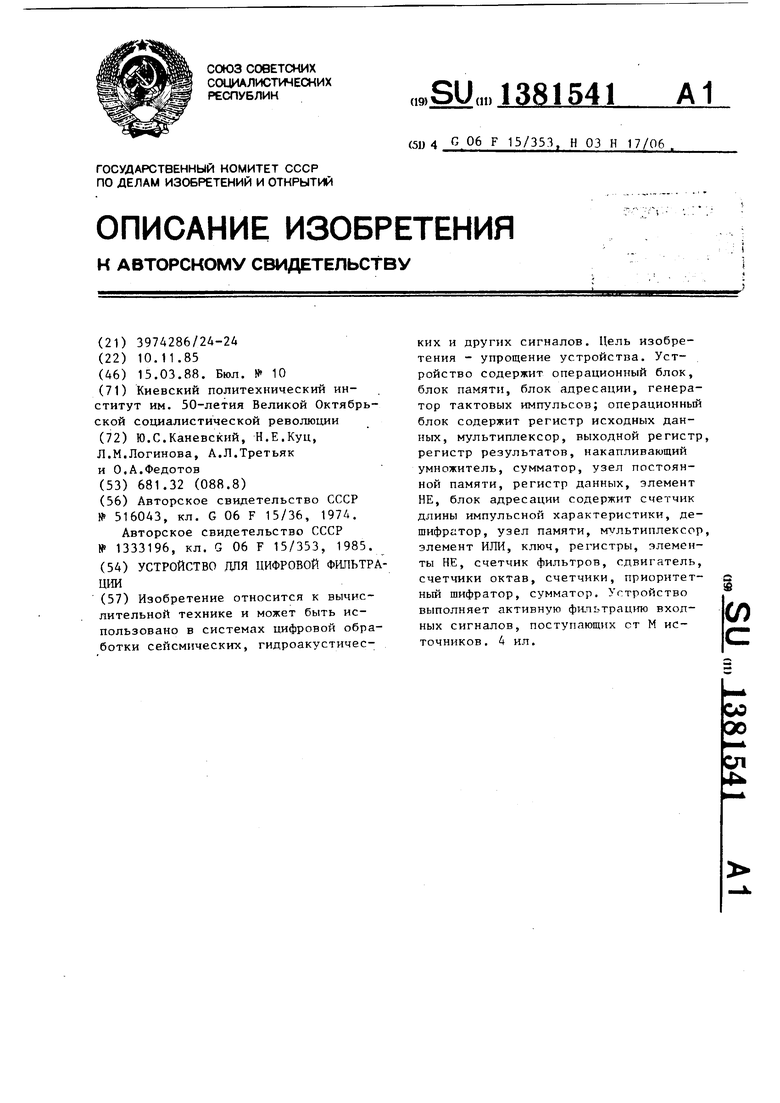

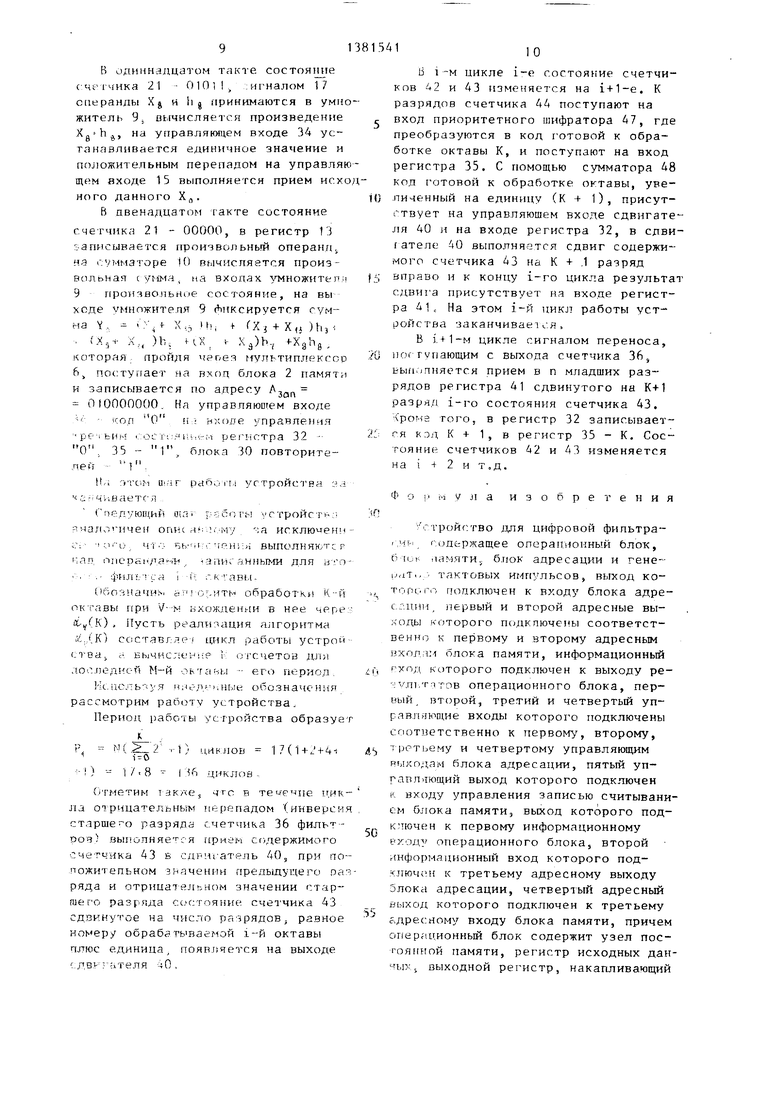

На фиг.1 представлена блок-схема устройства для цифровой фильтрации; на фиг.2 - матрица элементарных фильтров (ЭФ); на фиг.З - импульсная характеристика фильтра; на фиг. - формат адреса блока 2 памяти.

Устройство цифровой фильтрации содержит операционный блок 1, блок 2 памяти, блок 3 адресации, генератор 4 тактовых импульсов ч. Операционный блок 1 включает регистр 5 исходных данных, мультиплексор 6, выходной регистр 7, выход 8 результатов, накапливающий умножитель 9, сумматор 10, узел 11 постоянной памяти (коэффициентов), вход 12, регистр 13 данных, вход 1i, управляющий вход 15 элемент НЕ 16, управляющий вход 17, управляющий вход 18, адресные выходы 19 и 20 блока 3 адресации. Блок 3 адресации содержит счетчик 21 длины импульсной характерист}1ки, вход 22, дешифратор 23, узел 2ц постоянной памяти с выходом 25 блока 3 управляющие выходы 26 и 27, мультиплексор 28 элемент И.ПИ 29, ключ 30, управляющий выход 31, регистр 32, элемент НЕ 33, управляющий выход 34, регистр 35, счетчик 36 фильтров, регистр 37, ад- ресньш выход 38, элемент НЕ 39, слв гатель 40, регистр 41, счетчики 42 и 43 октав, счетчики 44 ц 45, регистр 46, приоритетный шифратор 47 и сумматор 48.

Устройство выполняет октавную фильтрацию входных сигналов, посту- дающих от М источников. Это обеспечи вается последовательной реализацией матрицы элементарных фильтров (МВФ) размером КхМ, которая приведена на фиг.2. При каскадном включении ЭФ в каждой октаве осуществляется прореживание даннь х вдвое, т.е. каждый из ЭФ формирует выходной отсчет тол1 ко по получении двух входных отсчетов. Поэтому ЭФ каждой последующей октавы обрабатывается вдвое реже фильтров предыдущер октавы. Это позволяет использовать один операционный блок для реапизации всей МЭФ.

Реализация любого ЭФ сводится к выполнению операции ациклической свертки по формуле

N-

(1)

-

ю 15

20 25 30 40

д,

5

где h - коэффициенты импульсной характеристики-;

отсчет входног о сигнала;

Y - выходной результат. Для иллюстрации работы устройства на фиг.З приведена импульсная характеристика, общее число N коэффициентов которой равно 17, причем все коэффициенты с четными номерами, кроме центрального (bg), равны нулю, а обшез число ненулевых коэффициентов равно (N-1)/2 -f 1, т.е. 9. В силу симметрии импульсной характеристики относительно оси ординат число различных нулевых коэффициентов равно 5 (4 боковых и 1 центральный). Симметричность импульсной характеристики . позволяет сократить число умножений, если входные отсчеты, которые должны быть умножены на симметричные коэффициенты предварительно просуммировать и затем умножить на соответствующий коэффициент. Из формулы (1) следует, что перед вычислением о.че- редного результата ЭФ последовательность входных отсчетов сдвигается относительно последовательности коэффициентов импульсной характеристики на две позиции. В предлагаемом устройстве -этот сдвиг осуществляется формированием на каждом шаге вычислений определенной последовательности адресов считывания. Эта последовательность зависит от количества вхождений в данную октаву (в данный ЭФ) и не зависит от номера обрабатываемой октавы. Пришедший последний по времени отсчет суммируется с самым старым отсчетом, т.е. отсчетом, ко- торьп на следующем щаге вычислений использоваться не будет, далее суммируются отсчет, предшествовавший последр1ему по времени, и отсчет, пришедщир после самого старого, и т.д. Все эти операции вь полняются только над нечетным отсчетом за исключением отсчета, который должен быть умножен на центральный коэффициент. Поскольку в данном случае (фиг.З) импульсная характеристика содержит 8 ненулевых нечетных коэффициентов, то существует 8 вариантов таких последовательностей.

Пусть At - интервал времени между двумя соседними отсчетами, поступаю- щими на вход устройства. Тогда 2Mit AT - время накопления двух отсчетов для всех ЭФ первой октавы, где М - число ЭФ в октаве. Устройст- во фильтрации работает в реальном масштабе времени, если за время Л Т вычисляется Y для М фильтров первой и М фильтров любой- другой октавы и время реализации одного ЭФ при этом составляет At.

Для последовательной реализации (обработки) ЭФ требуется объем памят V Y lW слов, где К - количество октав; М - количество фильтров в октаве; N-длина импульсной характе- ристики (количество отсчетов).

При формировании последовательности адресов блока 2 памяти примене способ присоединительной адресации. Формат адреса представлен на фиг.4. Первое поле адреса содержит адрес обрабатываемой октавы, или адрес следующей октавы, или адрес первой октавы. Количество разрядов первого поляk 1 1оргК. Второе поле адреса содержит адрес обрабатьгеаемого фильтра (количество разрядов т третье поле - адрес номера отсчета импульсной характеристики при чтении данных Х , записи результата Y и записи исходных данных в ЭФ первой октавы (количество разрядов п

О log Н О.

Следует отметить, что термин Vre вхождение в i-ю октаву озна- чает вычисление выходного отсчета Y для М фильтров i-й октавы в соответствии с вьфажением (1) и запись Y,,

в качестве исходных данных

v-n

для

i+1-й октавы, вхождение в каждую i-ю октаву выполняется в два раза чаще, чем в i-i-1-ю; при V-M вхождении в любую октаву значения адресов чтения данных Х.„ ( ) и записи выходных данных А отличаются только зна- чением в первом после адреса.

Для иллюстрации работы устройства рассмотрим случай при К 3, М 3, N 17.

В данном случае счетчик 21 длины импульсной характеристики имеет коэффициент пересчета N

1.4 12

JQ 15

и 20

н25 О

Q

дд Q

55

и для реализации требуется п 4 разряда, счетчик 36 фильтров имеет коэффициент пересчета М 3 и для его реализации требуется m .f 2 разряда, счетчик 42 октав имеет коэффициент пересчета N 17 и требует п 31ор2 5 разрядов, у счетчика 44 коэффициент пересчета равен 8 и для его реализации требуется К 3 разряда, счетчик 45 имеет коэффициент пересчета N и требует п lopgN 5 разрядов, у счетчик 43 коэффициент

пересчета К- ( .2 + 1) 136. -o

Для формирования первого поля адР ап,0, ис (адреса записи исходных данных для первой октавы) используются суммгчтор 48, ключ 30 и приоритетный шифратор 47, Приоритетный шифратор 47 определяет номер готовой к вхождению октавы, который получается преобразователем К- разрядного слова в К-разрядный код, соответствующий номеру разряда с младшим нулем в этом слове. Например, ХХХО - 000, ХХХ01 - 001, ХХ011 - 010, XI11 - 111 и т.д. (крайний первый разряд - это самый младший разряд счетчика 43, X - безразличное состояние).

Кроме того, использован сдвига- тель 40, который выполняет сдвиг вправо текущего значения В счетчика 43 на количество разрядов, равное К + 1. В результате такого преобразования получаем старшие п разрядов адреса узла 24 постоянной памяти. Младшие п разрядов этого адреса формируются на счетчике 21. Считанные из узла 24 постоянной памяти последовательности образуют третье поле адреса Азмп{ 4 Состояние счетчика 42 определяет значение третьего поля адреса А . Значение второго поля адреса Ajan .;;, , А , соответствует состоянию счетчика 36 фильтров.

С целью упрощения описания работы устройства будем считать, что прием информации во все регистры и умножитель, переключение счетчиков осуществляются положительным перепадом синхроимпульсов, выбранному выходу дешифратора 23 соответствует нулевое значение, режиму записи в блок 2 памяти - нулевое значение на управляющем входе 34, а режиму считывания единичное, режиму приема информации в сдвигатель соответствует наличие отрицательного перепада на входе управления приемом, а режиму выдачи информации - состояние О на входе управления приемом и состояние 1 на входе управления выдачей, режиму без накопления в умножителе 9 соответствует нулевое значение на управ- ,ляющем входе 18.

Шаг работы устройства составляет

N-1

N тактов работы счетчика 21 длины импульсной характерио- Из N тактов М --- -1-1 9

тики,

N-1 -2- тактов используются для режима считывания данных Х,||, один такт - дл записи исходных данных и еще два та та - для получения и записи результ та вычислений v в б:1ок 2 памяти.

Для реализации i-ro вхождения в октаву требуется ш 3 шага. Пусть 1-е вхожд.ение в октаву составляет цикл работы устройства, а период ег работы образовывает количество циклов, необходимое для г ычисления отсчетов послрднс (третьей) октавы,

1 . тЛ, т - 1) 17-8 136

т-О ЦИКЛОВ.

в исходном состоянии, которое пусть соотвртствурт первому такту первого шага и псовому циклу работы устройства, в регистр 46, в который принимаются значения для третьего поля адресов, записан код 00001, в счетчике 21 длины п -тульспой характеристики 21 установлен код 00001, в регистре 41 - код 00000, которьш соответствует номеру вхождения в октаву, из узла 24 постоянной памяти считывается значение адреса 01111, которое присутствует на входе мультиплексора 28, на управляющих входах f льтиплeкcopa 28 - код 1 1 , который разрешает прохождение иформации с выхода узла 24 постоянно памяти на вход регистра 46, в регисре 37 - код 00, а в счетчике 36 фильтров - кол 01, в регистре 32 - код 01, в регистре 35 - кол 00, на входе управления третьим состоянием Z регистра 35 присутствует нулевое значение, которое разрешает прохождение содержимого чтого регистра на адресный вход )ка 2 памяти. Таким образом, на адресном входе блока 2

памяти присутствуят i fц (1) 000000001. На вхолр 34 управления записью-считыванием блока 2 памяти присутствует единичное значение, на выходе блока 2 памяти - данное Х, считаем, что в блоке 2 памяти - отсчеты для фильтров 1-й октавы, на адресном входе узла 11 постоянной памяти присутствует адрес 000, по которому из узла 11 памяти выбирается произвольное значение, В регистр 5 исходных данных записан операнд X .

Во втором такте первого шага на нхол 22 поступает тактовый импульс, который изменяет состояние счетчика 21 па 00010, этим же импульсом выпол- няе1 си прием кода 01111 в регистр 46. состояние регистров 41, 37, 32 и 35, упраплпю1 1их входов сумматоров 48, 10 и мультиплексоров 28 и 6 не изменяется. В регистр 13 принимается ланное Х| (сигнал 17). По адресу А, (2) 000001 Г 1 из блока 2 памяти считывается операнл X (на управляющем Bxo;ie 34 - 1), который поступает на }эход сумматора 10 (на управляющем вход(.- 15 сумматора 10 - уровень 1) 3 г;,мматоре 10 вычисляется сумма

ГУ

{

- X,,)

которая поступает iia первый вход лакап.чиваюиего умножителя 9, на втором входе накап- ливаю цего умножителя 9 присутствует

5

0

5

0

5

, которое считывается из

значение п

учл; 1 i постоянной памяти по адресу 0001. Из узла 24 ттостоянной памяти по а.лресу 0000010 считывается значение 0001 1 . .

Г) -рс:тьем такте состояние счетчика 21 - 00011, в регистр 46 принимается кол 00011, из узла 24 постоянной памяти по адресу 0000011 считывается код 01101, Состояние ррг истров 37, 32, 41 и 35 и сигналы управления мул1 тнплексорами и сумматорами не измС Няются, На адресном ВХО/ТР блока 2 памяти присутствует (3) 0(10000011, по которому считывается Xj. Положительным перепадом сигнала 17 выполняется прием суммы (.) и в умножитель 9, на управляю1чем, вхопе 18 умножителя 9 присутствует код О, в умножителе произведение (Х , + суммируется с нулем.

четве том такте г ервого шага состояние счетчика 21 - 00100, в регистр 46 принимается код ОП01, а из учла 24 памяти по адресу 00(10100

N. h,,

вычисляется которое

считывается код 00101. Состояние регистров 37, 32, 35 и 41, управляющих входов сумматоров 10 и 48, мультиплексоров 28 и 6 не изменяется. В регистр 13 принимается операнд (сигнал 17), из блока 2 памяти по адресу Aj.,. (Д) 000001101 считывается X,, и поступает на вход сумматора 10 b сумматоре 10 вычисляется (Xj X,., ) и поступает на первый вход умножителя 9, на втором входе умножителя 9 присутствует значение h ,, счргтанное из узла 11 постоянной памяти по адресу 0010, в умножителе 9 положи- тельным перепадом (сигнал 17) фиксируется значение (Х,+ X,5) h, на выходе умножителя 9.

В пятом такте первого шага состояние счетчика 21 - 00101, в регистр 46 принимается код 00101, из узла 24 постоянной памяти по адресу 0000101 считывается код 01011. Как и в предыдущих тактах, состояние регистров, сумматоров, мультиплексоров (элемен- ты 41, 37, 32, 30, 10, 40, 6, 28) не измеклется.

На адресном зходе блока 2 памяти - адрес (5) 000000101, по которому считывается операнд Х. Сигналом i 7 выполняется прием (Хз+ ) и hj в умножитель 9 (на управляющем входе 18 код 1) и вычисляется ( x,j )Ьз .

В шестом такте (состояние счетчика 21 - 00110) работа устройства аналогична описанной для второго и четвертого тактов, за исключением того, что значение на управляющем входе 18 соответствует 1 и в умножителе 9 вычисляется сумма (Х,- + Х,с ) (Хз+ Х,5 )hj .

В регистр 13 записывается операнд Xj, из блока 2 памяти считывается X,, , в сумматоре 10 вычисляется (Xj + X,, ) и поступает на первый вход умножителя 9, на второй вход умножителя 9 поступает значение hj-, считанное из узла 11 постоянной памяти по адресу 0011, из узла 2А постоянной памяти считывается код 00111.

На выходе умножителя 9 фиксируется ( )h, + (Хз+ X,j )Ьз .

В седьмом такте состояние счетчика 21 - 00111, работа устройства аналогична описанной для третьего и пятого тактов. Из узла 24 памяти считывается код 01001, в регистр 46 принимается код 00111, на адреснрм

5

0 5

О

5

0

5

входе блока 2 памяти адрес А,(7) 000000111, по которому считывается операнд Х-. Cигнaлo . 17 принимаются (Xj + Х, ) и bj в умножителг,- 9 (на управляющем зхоле 18 - кол 1), вычисляется (Х + х,, )-h5.

Восьмой такт (состояние счетчика 21 - 01000) аналогичен шестому. В умножителе 9 управляющим сигналом 17 фиксируется сумма (Х,-н X|j)-h, + -f (Х;,+ Х„ )-hy - (X 4. х,, ).Ъз, в регистр 13 записывается операнд Х, из блока 2 памяти считывается Хд, в сумматоре 10 вычисляется ( Хд) и поступает на первый вход умножителя 9, на второй вход умножителя 9 поступает значение h, считанное из узла 11 постоянной памяти по адресу 0100, из узла 24 постоянной 1 амяти считывается код 01000.

В девятом такте состояние счетчика 21 - 01001, в регистр 46 ется код 00000, на адресном Бходе блока 2 памяти адрес А (9)

С-Ц U Т

000001000, по которому считывается операнд Х§, умножаемый на централь- нь й коэффициент 1гмпульс ной характеристики hg. Сигналом 17 принимаются (Х-,+ Xj) и h в умножитель 9 (на управляющем входе 18 - код 1), вычисляется ( Хз)Ь-, .

На мультиплексоре 28 изменяется управляющий код на 01, который разрешает прохождение информации с выхода счетчика 42.

В десятом такте состояние счетчика 21 - OtOlO, в регистр 13 записывается операнд Xj, на управляющем входе 15 сумматора 10 - код О, который соответствует режиму Пропуск операнда, и Хд поступает на первый вход умножителя 9, на втором входе умножителя 9 присутствует значение hg , считанное из узла 11 постоянной памяти по адресу 0101, в умножителе 9 фиксируется сумма ( X,y) h + + (Хз+ X,., )-Ьз+ (Xj+ X,, )-hj + + ( Xg) h , в регистр 46 принимается значение 00000, на адресных входах блока 2 памяти присутствует адрес А(./ 000000000. На управляющем входе 34 блока 2 памяти присутствует нулевое значение, что обеспечивает запись X по адресу . «рОООООООО. В этом же такте из узла 24 постоянной памяти по адресу 00000 считывается код 00001.

В одиннадцатом такте cocTonmie (:ч ч-чика 21 - 0101, сигналом 17 операнды Xj и hg принимаются в умножитель 9j вычисляется произведение , на управляющем входе 34 устанавливается единичное значение и положительным перепадом на управляющем йходе 15 выполняется прием исхоного данного Xfi.

В пвенадцатом такте состояние

счетчика 21 - 00000, в регистр 13 записывается гфоичвольный операнд на ovMMaTope 10 вычисляется произвольная сунма на входах ножитеп, 9 пронзБОльное состояние, на вы ходе умножителя 9 фиксируется сумна Y, -

/ V

Х,- которая

. н

, ) h, П Х i- X пройдя чеоез

i Xi + Х,л )Ьз

fXghj

a)bv мультиплексор 2 памятя

fij поступает на вход блока и запись(вается по адресу A-j, 010000000. На управляюшем входе - коп о : ьхопе управления pe ifcHi i;:oc г;:яш, -м регистра 32 - 1., блока 30 повторите

О, лей

35 -

- M V

Ь; fcvci ui-ir pafto iT.i устройсп на ч a п ч;;ваетс-л

Гг)епую1ций ouTi чнало нчеи oniis, ;;; ;,1. ч) , что

1-пд олерйнда-гн

. , фил f с а

; ойс) rw VстройсTV-; с М7 Я исключен ЧеНГп BbinonHHKjTCF

а п I а н н ыми дд я с.к- сяви..

Обозначив, йтчог-ить обработки К-н октавы ггри V- M ьхожден1- и в нее чере liy(K) , Пусть реалт)зация алгоритма i i.,i.K) составлле цикл работы устройства,, а нычис; ;ен;;р I: отсчетов для л.О . ледисй М-й OhTiifibi его период.

lieuC. обозначения рассмотрим pa6oTv устройства.

Период работы усгройства образуе

А Р, w(. 2 -.-t) циклов 17(1+J + 4i

- 1 /. 8

( 36

циклов

(отметим тзк/хе, в теиечие пик да О1рнцательным перепадом (инверси старшего разряда счетчика 36 фильтров) вы1 олняе ся содержимого счетчика 43 в с/1Ригатель 40, при по пожитепьном значении предыдущего раряда и отрицательном значении старшего разряда сс. стояние счетчика 43 сдзинутое на число разрядов равное номеру oбpa6гтывae (oй 1--й октавы плюс единипа появ; чется на выходе ( двиу ателя 40 ,

)

j

0

i

В 1 /. 9

-м цикле 1-е состоя ие счетчиков - 4 и 43 изменяется на i+1-e, К разрядов счетчика 44 поступают на вход приоритетного шифратора 47, где преобразуются в код г отовой к обработке октавы К, и поступают на вход регистра 35. С помощью сумматора 48 код ГОТОВОР1 к обработке октавы, увеличенный на единицу (К 4 1), присутствует на управляюшем входе сдвигате-- ля 40 и на входе регистра 32, в сдви- ателе 40 выполняется сдвиг содержимого счетчика 43 на К + .1 разряд вправо и к концу i-ro цикла результат сдвига присутствует на входе регистра 4 1 , На этом i-й цикл работы устройства заканчивает с-Я ,

В i+l-M цикле сигналом переноса, iiof гупающим с выхода счетчика 36, вы/юпняется прием в п младших раз рядов регистра 41 сдвинутого на К+1 разряд i-ro состояния счетчика 43. Apor-is того, в регистр 32 записывается кэд К + 1, в регистр 35 - К. Состояние счетчиков 42 и 43 изменяется на i -t 2 и т,д.

Ф о м у л а изобретения

/стройсугво для цифровой фипьтра- /, г;,1держащее операп/ионный блок, б 101 памяти, блок адресации и гене- иат., тактовь х импудьсов, выход которого подключен к входу блока адре- c.rLiuin, первый и второй адресные выходы которого подкпючеиы соответственно к первому и второму адресным вхолмм блока памяти, информационный гход которого подключен к выходу ре- :. Л1.т-тгов операционного блока, первый, втсзрой, третий и четвертый уп- равл;поп;ие входы которого подключены соотиетственно к первом , второму, третьему и четвертому управляющим н,1хо;;ам блока адресации, пятый управляющий выход которого подключен к входу управления записью считыванием блока памяти, выход которого подключен к первому информационному входу операционного блока, второй г(нформационный вход которого под- Kjrt04;ui к третьему адресному выходу блока адресации, четвертый адресный выход которого подключен к третьему адресному входу блока памяти, причем операционный блок содержит узел пос- гоянной памяти, регистр исходных дан- чыХ; выходной регистр, накапливающий

умножитель, регистр данных, элемент НЕ, сумматор и мультиплексор, при этом информационный вход регистра исходных данных является информационным входом фильтра, а выход регистра исходных данных подключен к первому информационному входу мульти- плексора, выход которого подключен к информационному входу вькодного регистра и является выходом результатов операционного блока, а выход выходного регистра является информационным выходом устройства, второй информационньЕЙ вход, мультиплексора подключен к выходу накапливающего умножителя, первый и второй информационные входы которого подключены к выходам соответственно узла постоянной памяти и сумматора, первый вход которого соединен с информационным входом регистра данных и является первым информационным входом операционного блока, вторым информационным входом которого является адресный вход узла постоянной памяти, выход регистра данных подключен к второму входу сумматора, синхровход приема данных накапливающего умножителя соединен с входом элемента НЕ и является первым управляющим входом операционного блока, вторым управляющим входом которого является синхровход накопления данных накапливающего умножителя, синхровход выдачи данных которого соединен с синхро- входом регистра данных и подключен к выходу элемента НЕ, управляющий вход мультиплексора соединен с синхровхо- дами сумматора и регистра исходных данных и является третьим управляющим входом операционного блока, четвертым управляющим входом которого является синхровход выходного регистра, причем блок адресации содержит счетчик длины импульсной характеристики, дешифратор, узел постоянной памяти, элемент ИЛИ, ключ, четыре регистра, два счетчика октав, приоритетный шифратор, мультиплексор, элемент НЕ и сумматор, причем в блоке адресации счетный вход счетчика длин импульсной характеристики соединен с синхровходом четвертого регистра и является входом блока адресации, а информационный выход счетчика длины импульсной характеристики подключен к входу дешифратора и первому адресному входу узла постоянной памяти,

0

5

0

5

0

5

0

5

0

5

выходы разрядов, кроме младшего, счетчика длины импульсной характеристики являются третьим адресным выходом блока адресации, первым управ- ; яющим выходом которого является выход младшего разряда счетчикл длины импульсной характеристики, первый выход дешифратора является вторым управляющим вьг :одом блока адресации, второй выход дешифратора подключен к первому управляющему входу мультиплексора, третий выход дешифратора подключен к первому входу элемента ИЛИ, управляющему входу ключа и является третьим управляющим выходом блока адресации, четвертый выход дешифратора подключен к втopo fy управляющему входу мультиплексора, пятый выход дешифратора подключен к второму входу элемента 1ШИ, входу управления состоянием выходов первого регистра и является четвертым управляющим выходом блока адресации, выход элемента ИЛИ подключен к входу элемента НЕ и является пятым управляющим выходом блока адресации, выход элемента НЕ подключен к входу управления состоянием выходов 1 торого регистра, информационный выход первого счетчика октав подключен к первому информационному входу мультиплексора, второй информационный вход которого подключен к выходу узла постоянно) памяти, выход третьего регистра подключен к третьему информационному входу мультиплексора и второму адресному входу узла постоянной памяти, выход мульту - плексора подключен к информационному входу четвертого регистра, выход которого является первым адресным выходом блока адресации, информационный выход второго счетчика октав подключен к входу приоритетного шифратора, выход которого подключен к информационному входу второго регистра и первому входу сумматора, второй вход которого является входом задания константы устройства, выход сумматора подключен к информационному входу первого регистра, информационный вход ключа является входом задания кода нуля устройства, выходы первого и второго регистров соединены с выходом ключа и являются вторым адресным выходом блока адресации, о т- личающееся тем, что, с целью упрощения устройства, блок адресации содержит счетчик фильтров, пятый регистр и сдвигатель, выход переноса счетчика длины импульсной характеристики подключен к счетному входу счетчика фильтров, выход переноса которого подключен к счетным входам первого и второго счетчиков октав, синхровходам первого, второго и третьего регистров, информационный выход счетчика фильтров подключен к информационному входу пятого регистра, выход которого является четвертым адресным выходом блока адресации информационный выход второго счетчика октав подключен к информационному входу сдвигателя, вход управления сдвигом которого подключен к выходу сумматора, зход управления приемом информации сдвигателя подключен к выходу элемента НЕ, вход которого подключен к выходу М-го разряда счетчика фильтров (М - разрядность счет- чика фильтров), выход (М-1)-го разряда которого подключен к входу управления выдачей сдвигателя, информационный выход которого подключен к информационному входу третьего регистра ,

s

ч Н -d

13815Д1

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Устройство для быстрого преобразования Фурье | 1986 |

|

SU1392577A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сейсмических, гидроакустических и других сигналов. Цель изобретения - упрощение устройства. Устройство содержит операционный блок, блок памяти, блок адресации, генератор тактовых импульсов; операционный блок содержит регистр исходных данных, мультиплексор, выходной регистр, регистр результатов, накапливающий умножитель, сумматор, узел постоянной памяти, регистр данных, элемент НЕ, блок адресации содержит счетчик длины импульсной характеристики, дешифратор, узел памяти, мультиплексор, элемент ИЛИ, ключ, регистры, элементы НЕ, счетчик фильтров, сдвигатель, счетчики октав, счетчики, приоритетный шифратор, сумматор. Устройство выполняет активную фильтрацию входных сигналов, поступающих от М источников. 4 ил. S (Л

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1333196, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1985-11-10—Подача