4 СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Цифровой генератор функций | 1986 |

|

SU1388842A1 |

| Устройство для контроля родовой деятельности | 1988 |

|

SU1605259A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Вычислительное устройство | 1983 |

|

SU1130862A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

Изобретение относится к импульсной технике. Цель изобретения - расширение .диапазона дискретного регулирования фазы при заданной помехозащищенности. Устр-во .содержит г-р 1 импульсов, счетчик 2, сумматор 3, триггер 4, блок задержки 5, коммутатор 6 и эл-т ИЛИ 7. Цель достигается введением блока задержки 5, коммутатора 6 и эл-та ИЖ 7, сигнал на выходе которого относительно сигнала на выходе счетчика 2 в зависимости от вида сигнала на шине Направление сдвига и значения кода фазы позво- ляет регулировать фазовый сдвиг ретно как на опережение, так и на запаздывание в диапазоне М 2Г( - 1)/2 . Устр-во по п, 2 ф-лы отличается выполнением блока задержки 5. 1 з.п, ф-лы, 3 ил.

со

I Изобретение относится к импульсной технике и может быть использовано в системах цифровой обработки сигналов .

Целью изобретения является расширение диапазона дискретного регулирования фазы при заданной помехозащищенности,

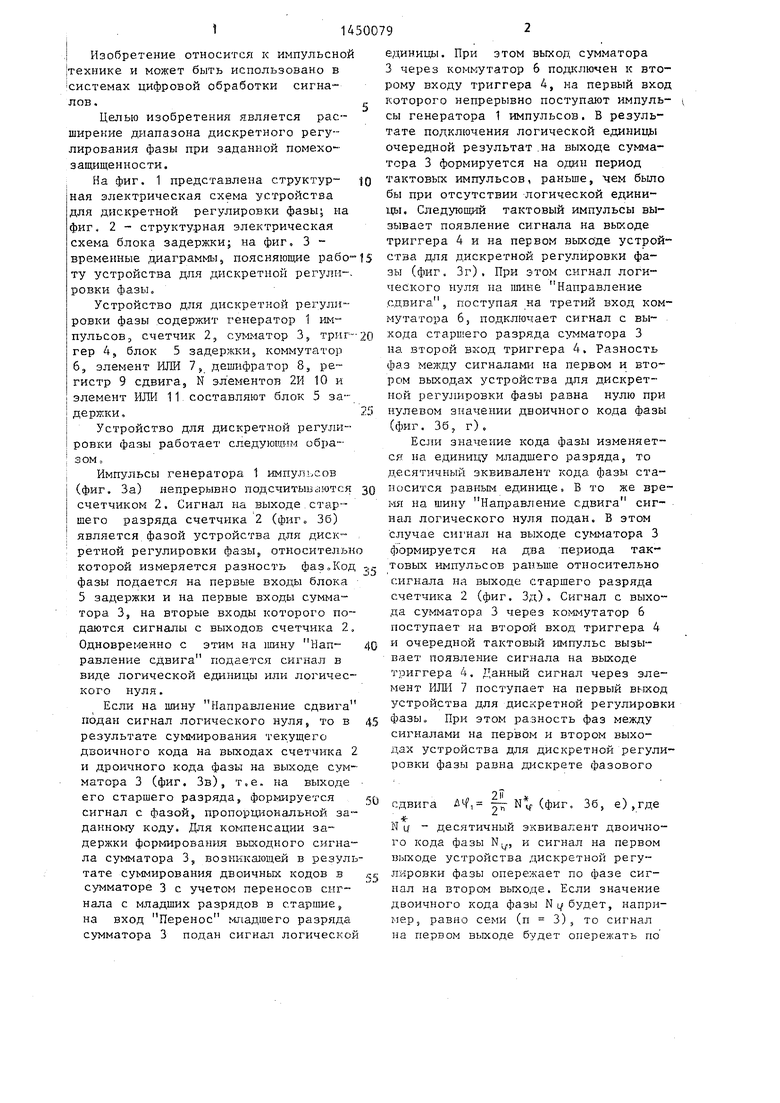

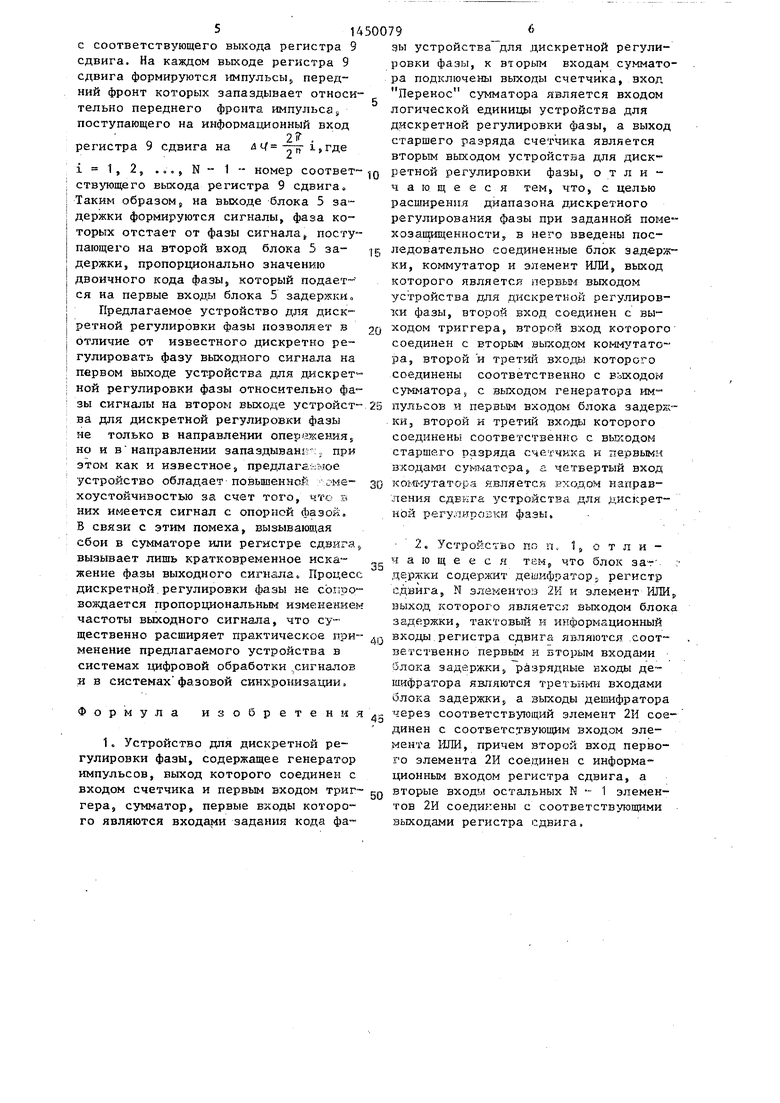

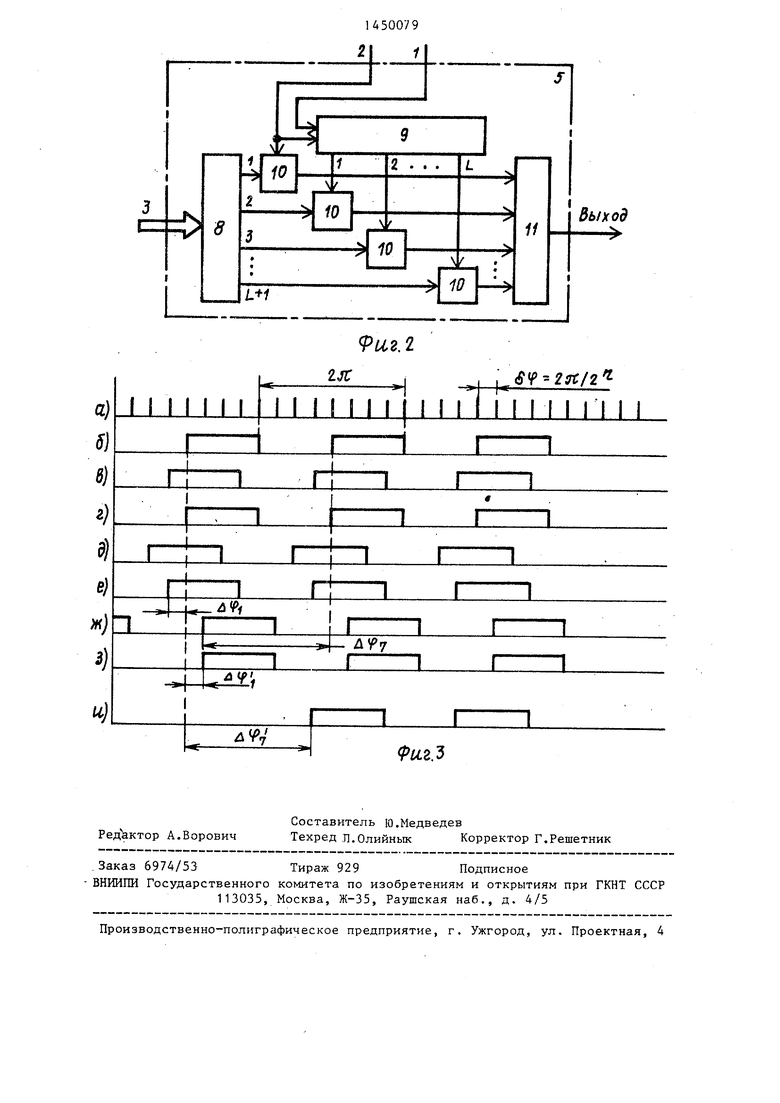

; На фиг. 1 представлена структур- |ная электрическая схема устройства для дискретной регулировки фазы на фиг. 2 - структурная электрическая схема блока задержки; на фиг, 3 - временные диаграммы, поясняющие работу устройства для дискретной регули-. ровки фазы.

Устройство для дискретной регулировки фазы содержит генератор 1 импульсов, сх1етчик 2, сумматор 3, триггер 4, блок 5 задержки, коммутатор б, элемент ИЛИ 7, дешифратор 8, регистр 9 сдвига, N элементов 2И 10 и элемент ИЛИ 11.составляют блок 5 задержки ,

Устройство для дискретной регулировки фазы работает следующим обра- ; зом о

; Импульсы генератора 1 импул :,сов I (фиг. За) непрерывно пoдcчитыБdютc { счетчиком 2. Сигнал на выходе.старшего разряда счетчика 2 (фиг„ 36) является.фазой устройства для диск™ ретной регулировки фазы., относительн которой измеряется разность фаз.Код фазы подается на первы.е входы блока 5 задержки и на первые входы сумматора 3, на вторые входы которого подаются сигналы с выходов счетчика 2, Одновременно с этим на шину Нап равление сдвига подается сигнал в виде логической единицы или логического нуля.

Если на шину Направление сдвига подан сигнал логического нуля, то в результате суммирования текущего двоичного кода на выходах счетчика 2 и дроичного кода фазы на выходе сумматора 3 (фиг, Зв), . на выходе его старшего разряда, фориируется сигнал с фазой, пропорциональной за™ дaннo ry коду. Для компенсации задержки формирования выходного сигнала сумматора 3, возникающей в результате суммирования двоичных кодов в

сумматоре 3 с учетом переносов сигнала с младших разрядов в старшие, на вход Перенос м:чадшего разряда сумматора 3 подан сигнал логической

единицы. При зтом выход сумматора 3 через коммутатор 6 подключен к второму входу триггера 4, на первый вход которого непрерывно поступают импуль сы генератора 1 импульсов, В результате подключения логической eдиниu lI очередной результат .на выходе сумматора 3 формируется на одан период тактовых импульсов, раньще, чем бьшо бы при отсутствии логической единицы. Следующей тактовый импульсы вызывает появление сигнала на выходе триггера 4 и на первом выходе устройства для дискретной регулировки фазы (фиг. Зг). При этом сигнал логического нуля на шине Направление .сдвига 5 поступая на третий вход коммутатора 6) подключает сигнал с выхода старшего разряда сумматора 3 на. второй вход триггера 4. Разность фаз между сигналами на первом и втором выходах устройства дпя дискретной регулировки фазы равна нулю при нулевом значении двоичного кода фазы (фиг. 36, г).

Если значение кода фазы изменяется на едини1 ;у младшего разряда, то десятичный эквивалент кода фазы ста- носится равным единще. В то же вре 1.ш на шину Направление сдвига сигнал логического нуля подан, В этом случае сигнал на выходе сумматора 3 формируется на два периода тактовых импульсов раньше относительно сигнала на выходе старшего разряда счетчика 2 (фиг. Зд), Сигнал с выхода сумматора 3 через коммутатор 6 поступает на второй вход триггера 4 и очередной тактовый импульс вызывает появление сигнала на выходе триггера 4. Данный сигнал через элемент ИЛИ 7 поступает на первый выход устройства для дискретной регулировк фазы о При этом разность фаз между сигналами на первом и втором выхо- i,ax устройства для дискретной регулировки фазы равна дискрете фазового

2V сдвига 1, - Ntf (фиг. Зб, е),,где

(N ц - десятичный эквивалент двоичного кода фазы N;, и сигнал на первом выходе устройства дискретной регулировки фазы опережает по фазе сигнал на втором выходе. Если значение двоичного кода фазы N (убудет, например, равно семи (п 3), то сигнал на первом выходе будет опережать по

фазе сигнал на втором выходе на максимальную величину, равную З i (фиг. Зж).

При поступлении на шину Направление сдвига сигнала логической единицы устройство для дискретной регулировки фазы работает следующим образом.

Сигнал с выхода старшего разряда счетчика 2 поступает на второй выход устройства для дискретной регулировки фазы и одновременно на второй вход блока 5 задержки, на первый вход которого поступают импульсы с генератора 1 импульсов. При этом на первые входы блока 5 задержки поступает двоичный код фазы Nqj. В зависимости от величины данного кода сигнал, поступающий на второй вход блока 5 задержки, задерживается на время, пропорциональное величине кода. С выхода блока 5 задержки сигнал |поступает на второй вход коммутатора 6 и далее с второго выхода коммутатора 6 через элемент ИЛИ 7 на первый выход устройства. Сигнал с выхода сумматора 3 блокируется в коммутаторе 6 сигналом логической единицы, поступающим с шины На правле- ние сдвига на третий вход коммутатора 6. Если значение кода фазы,равно нулю, то сигнал с выхода блока 5 задержки совпадает по фазе с сигналом на втором выходе устройства для дискретной регулировки фазы и через коммутатор 6 и злемент ИЛИ 7 поступает на первый выход устройства для дискретной регулировки фазы. Если значение кода фазы увеличить на единицу младшего разряда, то сигнал старшего разряда счетчика 2 задержится в блоке 5 задержки на одну дискрету, равную периоду следования импульсов с выхода генератора 1 импульсов. Поэтому сигнал на первом выходе устройства для дискретной регулировки

фазы отстает по фазе на

,

(фиг. Зз). Если значение двоичного кода фазы равно, например ,семи, то в блоке 5 задержки сигнал с выхода Старшего разряда счетчика 2 задержий,

Г

( 1)/

Бается на время

(фиг. Зи).

Таким образом, сигнал на первом выходе устройства для дискретной регулировки фазы относительно сигнала

0

на втором выходе устройства для дискретной регулировки фазы в зависимости от вида сигнала на шине Направление сдвига и значения кода фазы позволяет регулировать фазовый сдвиг дискретно как на опережение, так и на запаздывание в диапазоне If ± 1(2 - 1).

Блок 5 задержки (фиг. 2) работает следующим образом.

На первый его вход и далее на тактовый вход регистра 9 сдвига пос5 тупают импульсы с выхода генератора 1 импульсов. На второй вход блока 5 задержки и далее на информационный вход регистра 9 сдвига поступает сигнал с выхода старшего разряда счетQ чика 2(фиг. 1). Одновременно с этим на разрядные входы дешифратора 8 поступает двоичный код фазы. Если значение двоичного кода фазы равно нулю, то на первом выходе дешифрато5 ра 8 присутствует сигнал логической ед11ницы в виде высокого уровня напряжения, который поступает на первый вход первого элемента 2И 10. В то же время на первые входы остальных N-1

0 элементов 2И 10 поступают сигналы с логического нуля в виде низких .уровней напряжения. Поэтому только первый элемент 2И 10 открыт и сигнал с второго входа блока 5 задержки через него и элемент ИЛИ 11 поступает на выход блока 5 задержки без временной задержки.

При увеличении кода фазы на единицу младшего разряда на втором выходе дешифратора 8 имеется сигнал логической единицы, а на остальных выходах - сигналы логического нуля. Сигнал логической единицы с второго выхода дешифратора 8 поступает на перg вый вход второго элемента 2И 10, на второй вход которого поступает сигнал с первого выхода регистра 9 сдвига, сдвинутый по фазе на один период следования импульсов, постуQ паюших на тактовый вход регистра 9 сдвига, поступает на выход блока 5 задержки через открытый второй элемент 2И 10 и элемент ИЛИ 11. При изменении значения кода фазы от нулеg вого значения до максимального, равного (2 - 1), сигналы на выходе дешифратора 8 открывают один из элементов 2И 10 по первому входу, на второй вход которых поступает сигнал

5

0

с соответствующего выхода регистра 9 сдвига. На каждом выходе регистра 9 сдвига формируются импульсы передний фронт которых запаздывает относительно переднего фронта импульсаj поступающего на информационный вход

2 регистра 9 сдвига на ,где

1, 2,

N

на &Ц 1 -2

, it I номер соответ- ствугощего выхода регистра 9 сдвига Таким образом, на выходе блока 5 задержки формируются сигналы, фаза которых отстает от фазы сигналаj поступающего на второй вход блока 5 задержки, пропорционально значению двоичного кода фазЫа который подает ся на первые входы блока 5 задержки Предлагаемое устройство для диск ратной регулировки фазы позволяет в отличие от известного дискретно регулировать фазу выходного сигнала на первом выходе устройства дд1я ди скрет- ной регулировки фазы относительно фазы сигналы на втором выходе устройст- ва для дискретной регулировки фазы не только в направлении опережения, но и в направлении запаздыванк , при этом как и известное9 предлагаемое устройство обладает- повьшеннсй с ме

счет того, что в с опорной фазой.

хоустоичивостью за них имеется сигнал В связи с этим помеха, вызывающая сбои в сумматоре или регистре сдвига вызывает лишь кратковременное искажение фазы выходного сигнала. Процесс дискретной.регулировки фазы не сопровождается пропорциональным изме нением частоты выходного сигнала, что существенно расширяет практическое применение предлагаемого устройства в системах цифровой обработки .сигналов и в системах фазовой синхронизации.

которого является первым выходом устройства для дискретной регулиров- 1СИ фазы, второй вход соединен с вы- 2Q ходом триггера, второй вход которого соединен с вторым выходом коммутатора, второй и третий входь которого соединены соответственно с выходом сумматора, с выходом генератора импульсов и nepBbSM входом блока задержки, второй и третий входы которого соединены соответственно с вькодом старшего разряда счетчика и первымн зз кодами сумматора а четвертый вход кою-и-утатора является входом направления сдвига устройства для дискретной регулирс1вки фазы.

35

и 3 о б р е т е и и я д через соответств ующий злемент 2И соединен с соответствующим входом зле- .мента ИЛИ, причем второй вход первого злемента 2И соединен с информа- ционньм входом регистра сдвига, а вторые входы остальных N 1 элементов 2И соединены с соответствующими выходами регистра сдвига.

Формула

1 Устройство для дискретной регулировки фазы, содержащее генератор импульсов, выход которого соединен с входом счетчика и первым входом триггера, сумматор, первые вкоды которого являются входами задания кода фа50

зы устройства для дискретной регулировки фазы, к вторьп«1 входам сумматора подключены выходы счетчика, вход Перенос сумматора является входом логической единицы устройства для дискретной регулировки фазы, а выход старшего разряда счетчика является вторым выходом устройства для дискретной регулировки фазы, о т л и - ч а ю, щ е е с я тем, что, с целью расширения диапазона дискретного регулирования фазы при заданной поме хозащищенности, в него введены последовательно соединенные блок задержки, коммутатор и элемент ИШИ, выход

которого является первым выходом устройства для дискретной регулиров- 1СИ фазы, второй вход соединен с вы- ходом триггера, второй вход которого соединен с вторым выходом коммутатора, второй и третий входь которого соединены соответственно с выходом сумматора, с выходом генератора импульсов и nepBbSM входом блока задержки, второй и третий входы которого соединены соответственно с вькодом старшего разряда счетчика и первымн зз кодами сумматора а четвертый вход кою-и-утатора является входом направления сдвига устройства для дискретной регулирс1вки фазы.

9иг.2

| Устройство для дискретной регулировки фазы | 1984 |

|

SU1200193A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-01-07—Публикация

1987-05-28—Подача