Изобретение относится к вычислительной технике и может быть исполь- .зовано для организации ввода-вывода информации в вычислительных системах

Целью изобретения является повышение надежности устройства за счет организации программного контроля адресации абонентов.

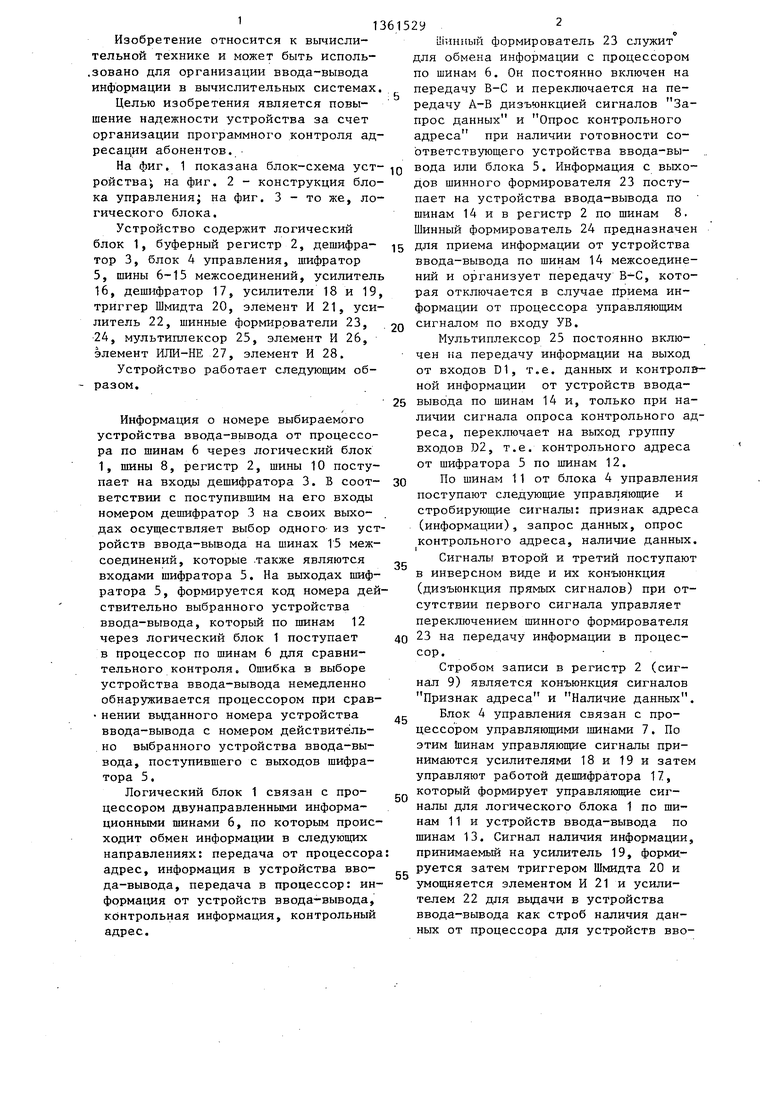

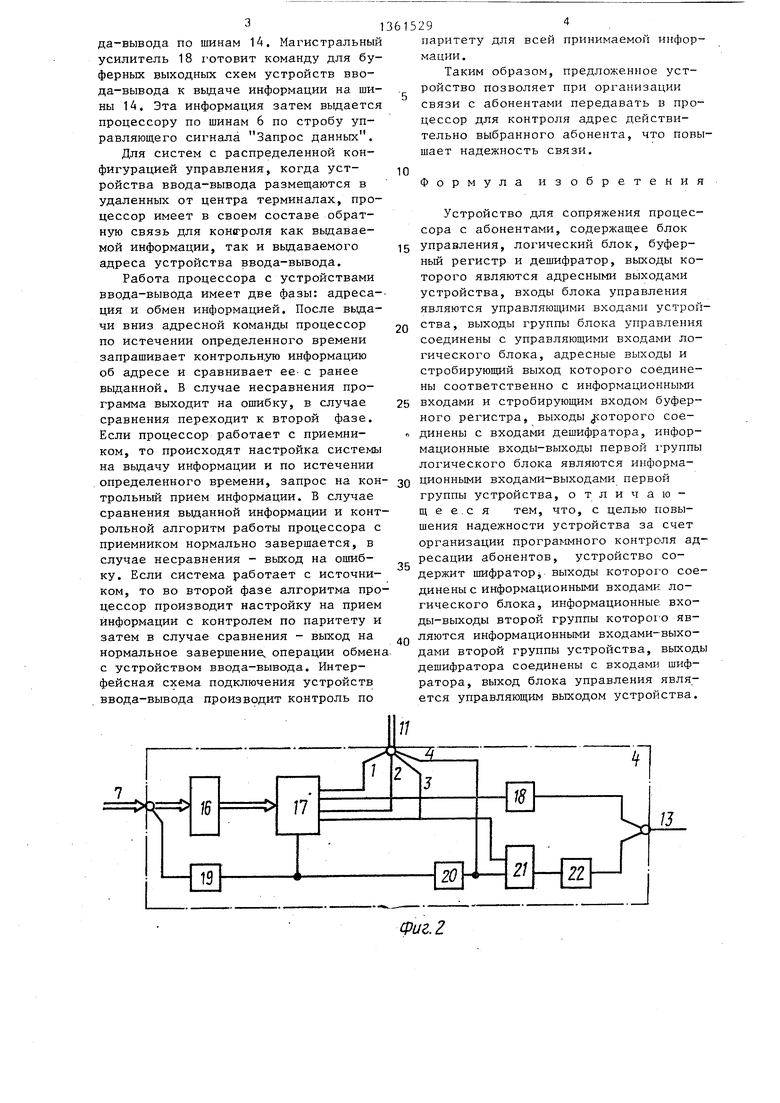

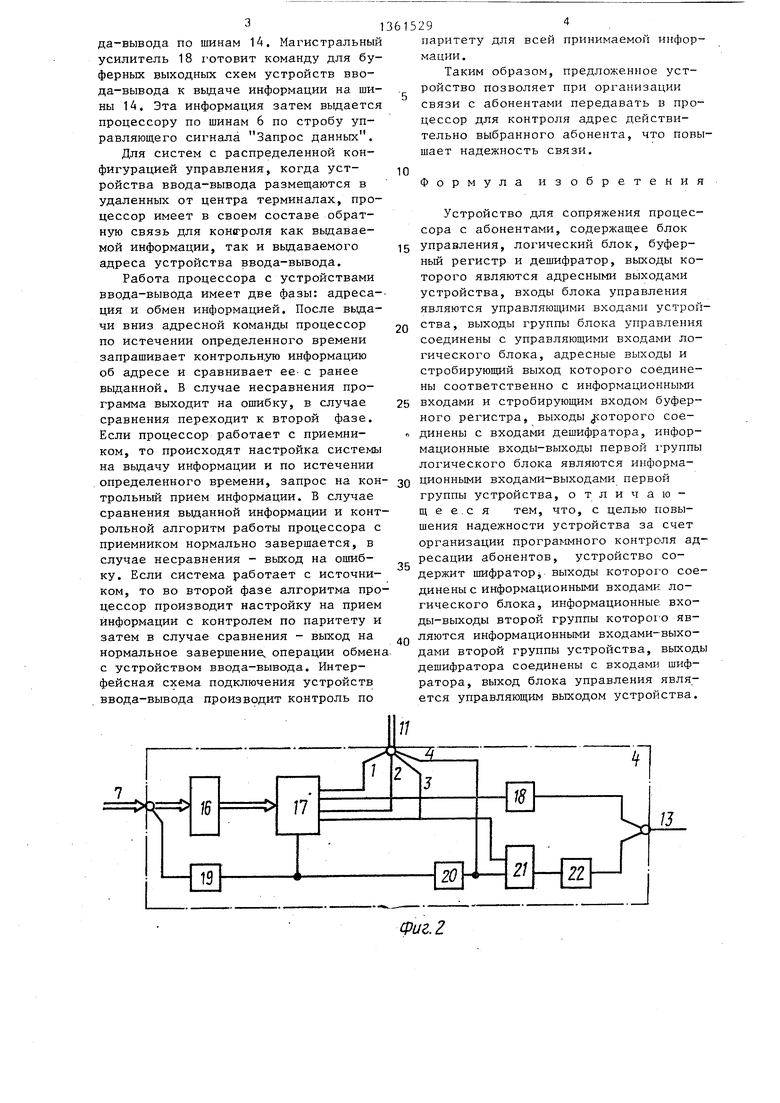

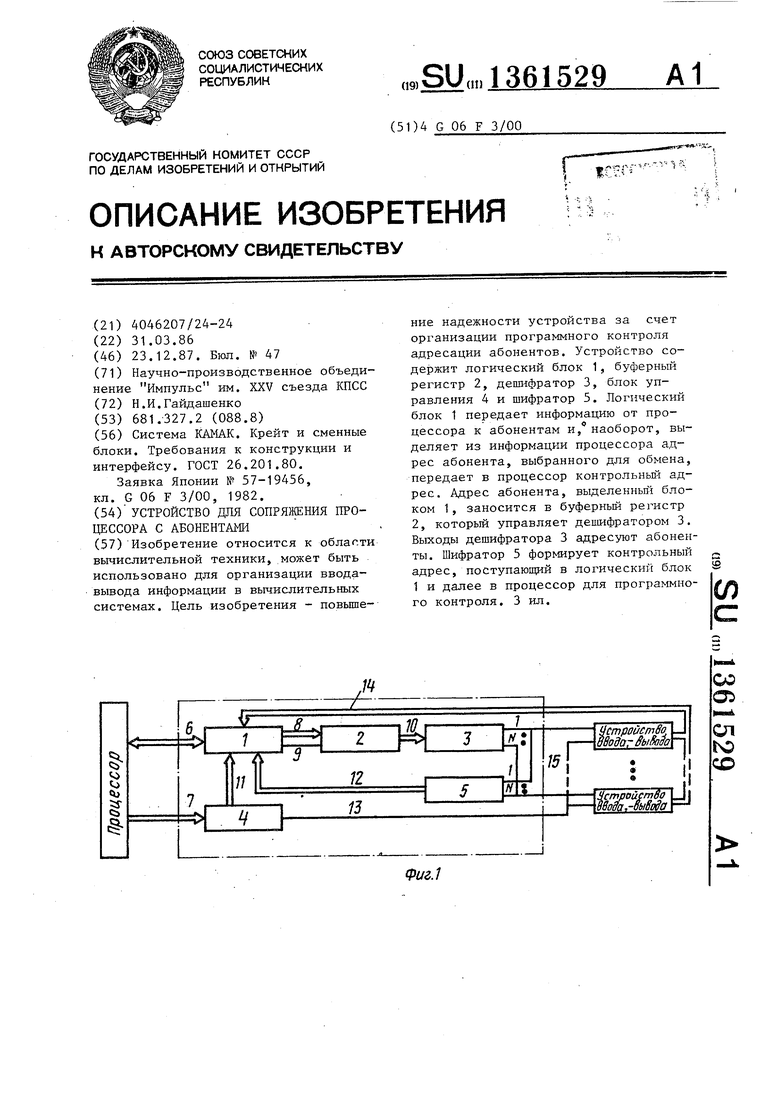

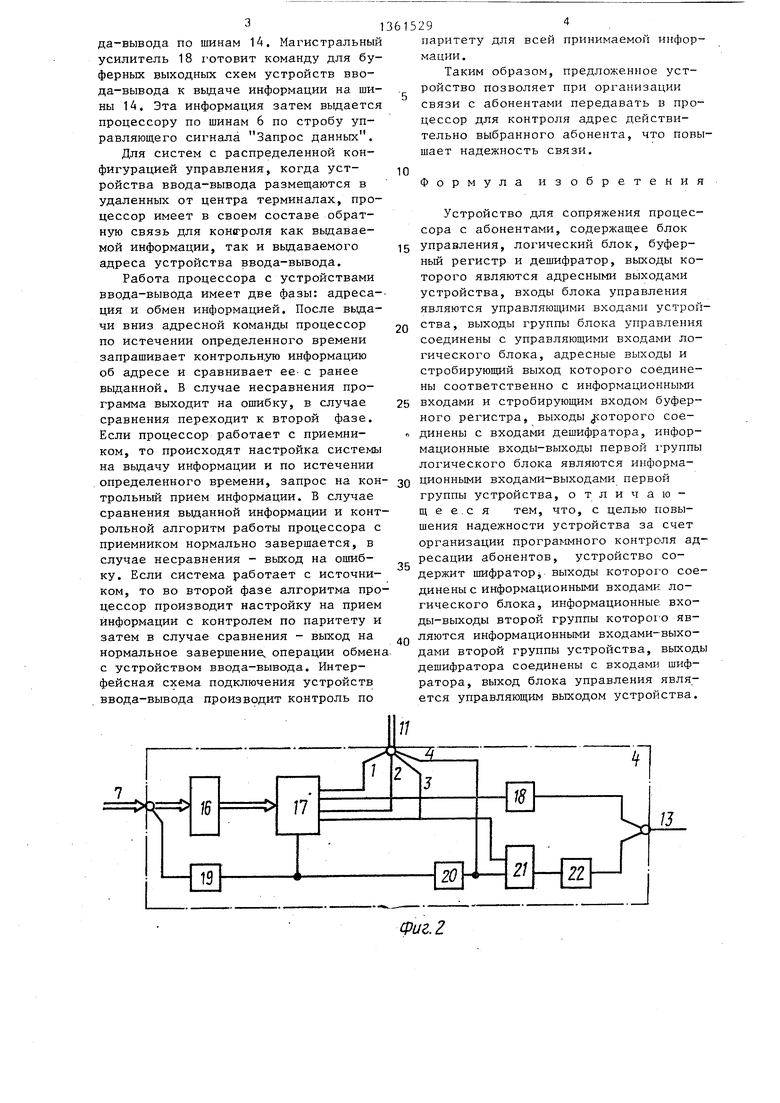

На фиг. 1 показана блок-схема устройства; на фиг. 2 - конструкция блока управления; на фиг. 3 - то же, логического блока.

Устройство содержит логический блок 1, буферный регистр 2, дешифратор 3, блок 4 управления, шифратор 5, шины 6-15 межсоединений, усилитель 16, дешифратор 17, усилители 18 и 19 триггер Шмидта 20, элемент И 21, усилитель 22, шинные формирователи 23, 24, мультиплексор 25, элемент И 26, элемент ИЛИ-НЕ 27, элемент И 28.

Устройство работает следуюш 1м образом.

Информация о номере выбираемого устройства ввода-вывода от процессора по шинам 6 через логический блок 1, шины 8, регистр 2, шины 10 поступает на входы дешифратора 3. В соответствии с поступившим на его входы номером дешифратор 3 на своих выходах осуществляет выбор одного- из устройств ввода-вьшода на шинах 15 межсоединений, которые .также являются входами шифратора 5. На выходах шифратора 5, формируется код номера действительно выбранного устройства ввода-вывода, который по шинам 12 через логический блок 1 поступает в процессор по шинам 6 для сравнительного контроля. Ошибка в выборе устройства ввода-вывода немедленно обнаруживается процессором при срав- нении выданного номера устройства ввода-вывода с номером действительно выбранного устройства ввода-вывода, поступившего с выходов шифратора 5.

Логический блок 1 связан с процессором двунаправленными информационными шинами 6, по которым происходит обмен информации в следующих направлениях: передача от процессора адрес, информация в устройства ввода-вывода, передача в процессор: информация от устройств ввода-вывода, контрольная информация, контрольный адрес.

0

5

Шинный формирователь 23 служит для обмена информации с процессором по шинам 6. Он постоянно включен на передачу В-С и переключается на передачу А-В дизъюнкцией сигналов Запрос данных и Опрос контрольного адреса при наличии готовности соответствующего устройства ввода-вывода или блока 5. Информация с выходов шинного формирователя 23 поступает на устройства ввода-вывода по шинам 14 и в регистр 2 по шинам 8. Шинный формирователь 24 предназначен 5 для приема информации от устройства ввода-вывода по шинам 14 межсоединений и организует передачу В-С, которая отключается в случае Приема информации от процессора управляющим сигналом по входу УВ.

Мультиплексор 25 постоянно включен на передачу информации на выход от входов D1, т.е. данных и контролв- ной информации от устройств ввода- вывода по шинам 14 и, только при наличии сигнала опроса контрольного адреса, переключает на выход группу входов D2, т.е. контрольного адреса от шифратора 5 по шинам 12.

По шинам 11 от блока 4 управления поступают следующие управляюш;ие и стробируюш е сигналы: признак адреса (информации), запрос данных, опрос контрольного адреса, наличие данных.

Сигналы второй и третий поступают в инверсном виде и их конъюнкция (дизъюнкция прямых сигналов) при отсутствии первого сигнала управляет переключением шинного формирователя 23 на передачу информации в процессор.

Стробом записи в регистр 2 (сигнал 9) является конъюнкция сигналов Признак адреса и Наличие данных.

Блок 4 управления связан с процессором управляющими шинами 7. По этим Шинам управляющие сигналы принимаются усилителями 18 и 19 и затем управляют работой дешифратора 17, который формирует управляющие сигналы для логического блока 1 по шинам 11 и устройств ввода-вывода по шинам 13. Сигнал наличия информации, принимаемый на усилитель 19, формируется затем триггером Шмидта 20 и умощняется элементом И 21 и усилителем 22 для выдачи в устройства ввода-вывода как строб наличия данных от процессора для устройств вво0

5

0

5

0

5

да-вьшода по шинам 14. Магистральный усилитель 18 готовит команду для буферных выходных схем устройств ввода-вывода к выдаче информации на шины 1А, Эта информация затем вьщается процессору по шинам 6 по стробу управляющего сигнала Запрос данных.

Для систем с распределенной конфигурацией управления, когда устройства ввода-вывода размещаются в удаленных от центра терминалах, процессор имеет в своем составе обратную связь для контроля как выдаваемой информации, так и вьщаваемого адреса устройства ввода-вывода.

Работа процессора с устройствами ввода-вывода имеет две фазы: адресация и обмен информацией. После вьзда- чи вниз адресной команды процессор по истечении определенного времени запрашивает контрольную информацию об адресе и сравнивает ее с ранее вьщанной. В случае несравнения программа выходит на ошибку, в случае сравнения переходит к второй фазе. Если процессор работает с приемником, то происходят настройка системы на выдачу информации и по истечении определенного времени, запрос на контрольный прием информации. В случае сравнения выданной информации и контрольной алгоритм работы процессора с приемником нормально завершается, в случае несравнения - выход на ошибку. Если система работает с источником, то во второй фазе алгоритма процессор производит настройку на прием информации с контролем по паритету и затем в случае сравнения - выход на нормальное завершение, операции обмен с устройством ввода-вывода. Интерфейсная схема подключения устройств ввода-вывода производит контроль по

361529

паритету для всей принимаемой информации .

Таким образом, предложенное уст- ройство позволяет при организации связи с абонентами передавать в процессор для контроля адрес действительно выбранного абонента, что повышает надежность связи.

10

Формула изобретения

Устройство для сопряжения процессора с абонентами, содержащее блок управления, логический блок, буферный регистр и дешифратор, выходы которого являются адресными выходами устройства, входы блока управления являются управляющими входами устрой20

ства, выходы группы блока управления

соединены с управляющими входами логического блока, адресные выходы и стробирующкй выход которого соединены соответственно с информационными 5 входами и стробирующим входом буферного регистра, выходы :оторого сое- динены с входами дешифратора, информационные входы-выходы первой 1 руппы логического блока являются информа- 0 ционными входами-выходами первой группы устройства, отличаю- щ е е.с я тем, что, с целью повышения надежности устройства за счет организации программного контроля адресации абонентов, устройство содержит шифраторj выходы которого соединены с информационными входами логического блока, информационные входы-выходы второй группы которог о являются информационными входами-выходами второй группы устройства, выходы дешифратора соединены с входами шифратора, выход блока управления является управляющим выходом устройства.

5

0

Фиг. 2

Составитель В.Файзрахманов Редактор Н.Гунько Техред М.ДвдькКорректор А.Тяско

Заказ 6283/47 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственнб-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Модульная многоуровневая система коммутации процессоров | 1984 |

|

SU1249524A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

Изобретение относится к области вычислительной техники, может быть ние надежности устройства за счет организации программного контроля адресации абонентов. Устройство содержит логический блок 1, буферный регистр 2, дешифратор 3, блок управления 4 и шифратор 5. Логический блок 1 передает информацию от процессора к абонентам и, наоборот, выделяет из информации процессора адрес абонента, выбранного для обмена, передает в процессор контрольньш адрес. Адрес абонента, выделенньш блоком 1, заносится в буферный регистр 2, который управляет дешифратором 3. Выходы дешифратора 3 адресуют абоненты. Шифратор 5 формирует контрольный

| Система КАМАК | |||

| Крейт и сменные блоки | |||

| Требования к конструкции и интерфейсу | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-03-31—Подача