Изобретение относится к вычислительной технике, в частности к организации микропрограммных мультиплексных каналов микропрограммных вычислительных машин,, может быть использовано для организации обмена информацией между периферийными устройствами и процессором и является усовершенствованием изобретения по авт.св. № 1256036.

Цель изобретения - расширение функциональных возможностей микропрограммного мультиплексного канала за счет организации плавающего количества подканалов с возможностью их Произвольного распределения, т.е. назначения любого подканала любому периферийному устройству-с последующим освобождением его после конца

связи канала с периферийным устройст-20 информационный выход 41 блока региством,

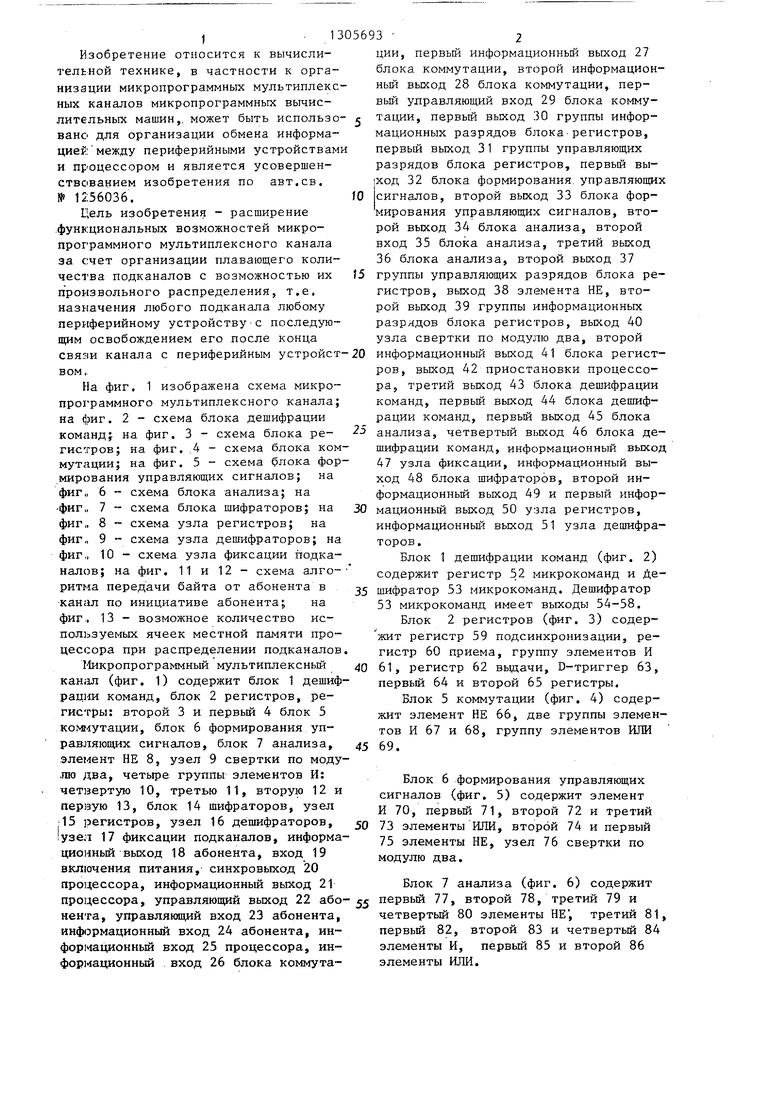

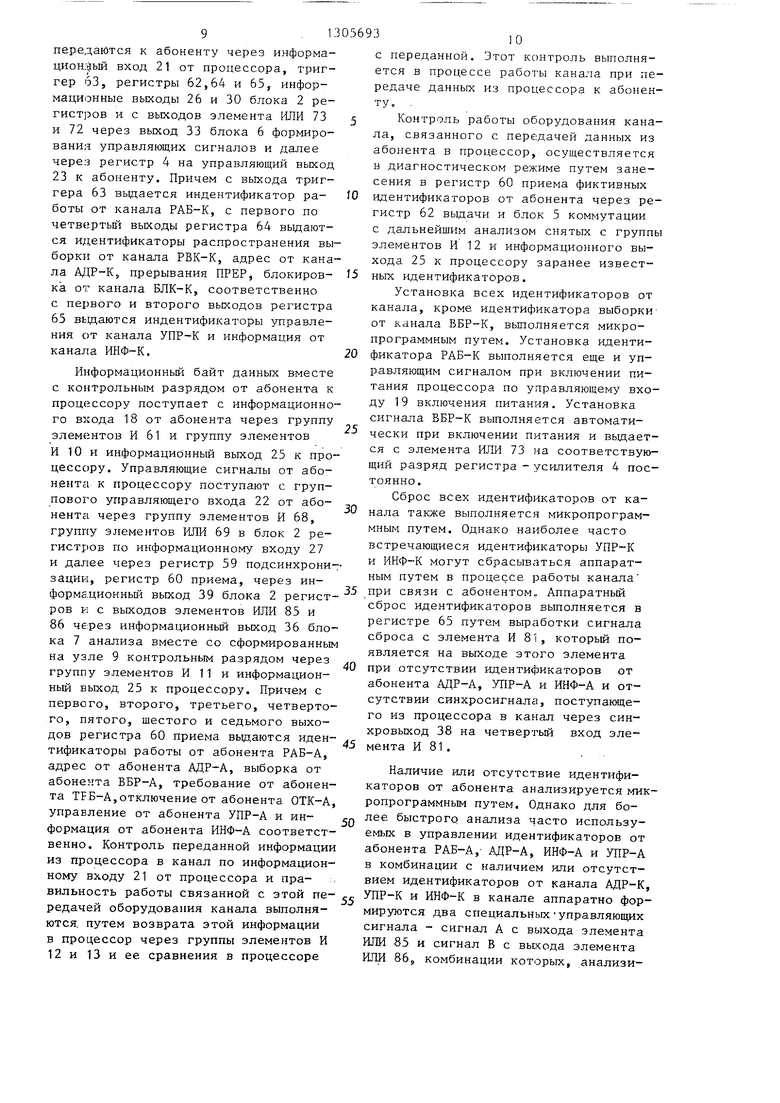

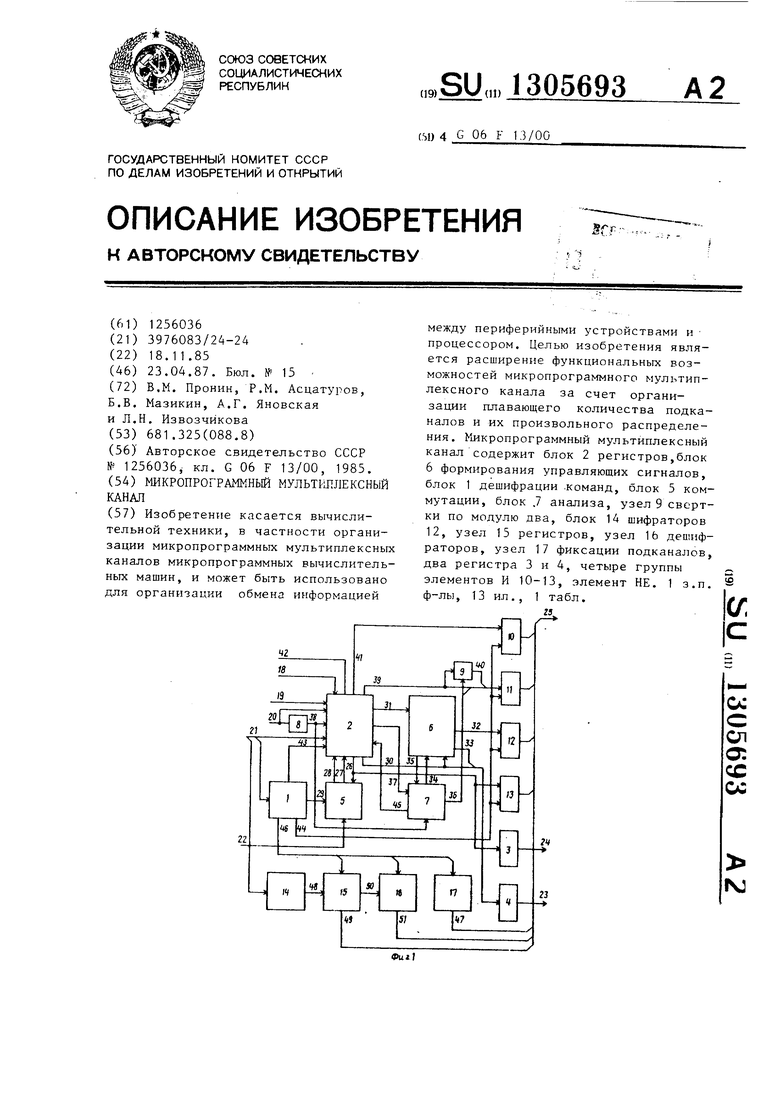

На фиг, 1 изображена схема микропрограммного мультиплексного канала; на фиг. 2 - схема блока дешифрации команд; на фиг. 3 - схема блока регистров; на фиг. .4 - схема блока коммутации; на фиг. 5 - схема блока формирования управляющих сигналов; на фиг,, 6 - схема блока анализа; на -фиг., 7 - схема блока шифраторов; на фиг с. 8 - схема узла регистров; на фиг,, 9 - схема узла дешифраторов; на фиг,, 10 - схема узла фиксации подканалов; на фиг. 11 и 12 - схема алгоритма передачи байта от абонента в -кангш по инициативе абонента; на фиг., 13 - возможное количество используемых ячеек местной памяти процессора при распределении подканалов.

11икропрограммный мультиплексный кан;зл (фиг. 1) содержит блок 1 дешифрации команд, блок 2 регистров, регистры: второй 3 и первый 4 блок 5 комг,1утации, блок 6 формирования управляющих сигналов, блок 7 анализа, 45 элемент НЕ 8, узел 9 свертки по моду- .гао два, четыре группы элементов И: четвертую 10, третью 11, вторую 12 и первую 13, блок 14 шифраторов, узел 15 регистров, узел 16 дешифраторов, 50 узел 17 фиксации подканалов, информационный выход 18 абонента, вход 19 вкл очения питания, синхровыход 20 процессора, информационный выход 21

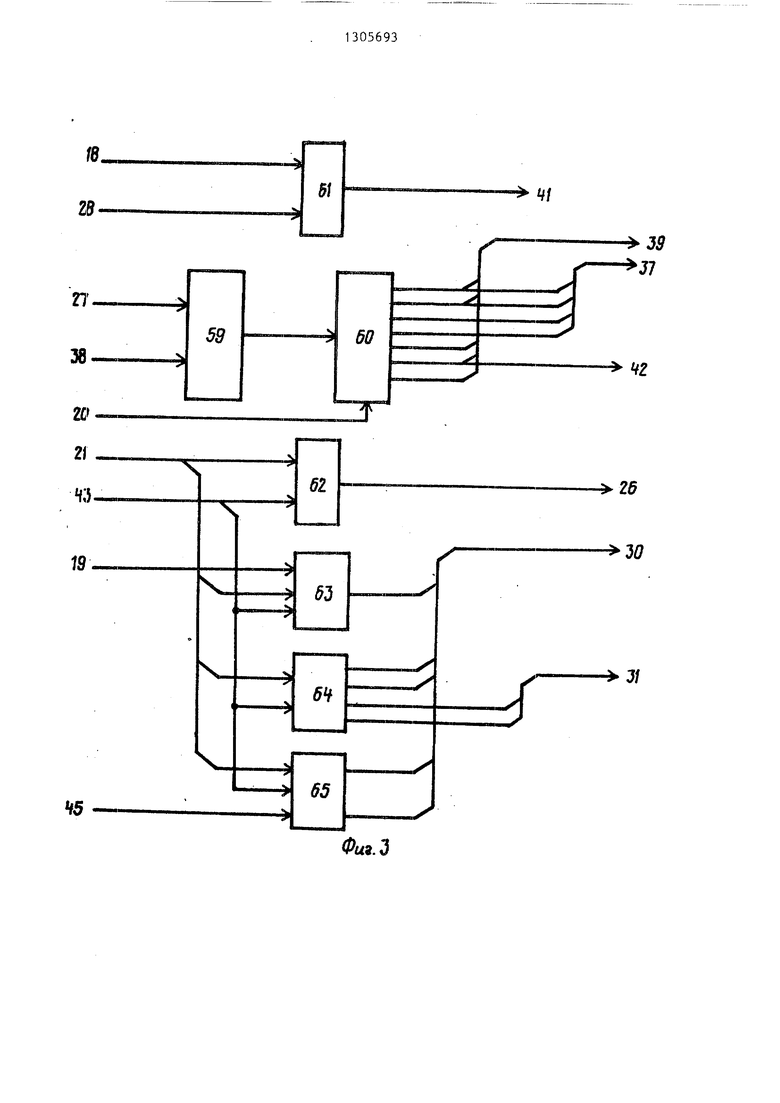

Блок 5 коммутации (фиг. 4) содержит элемент НЕ 66, две группы элементов И 67 и 68, группу элементов ИЛИ 69.

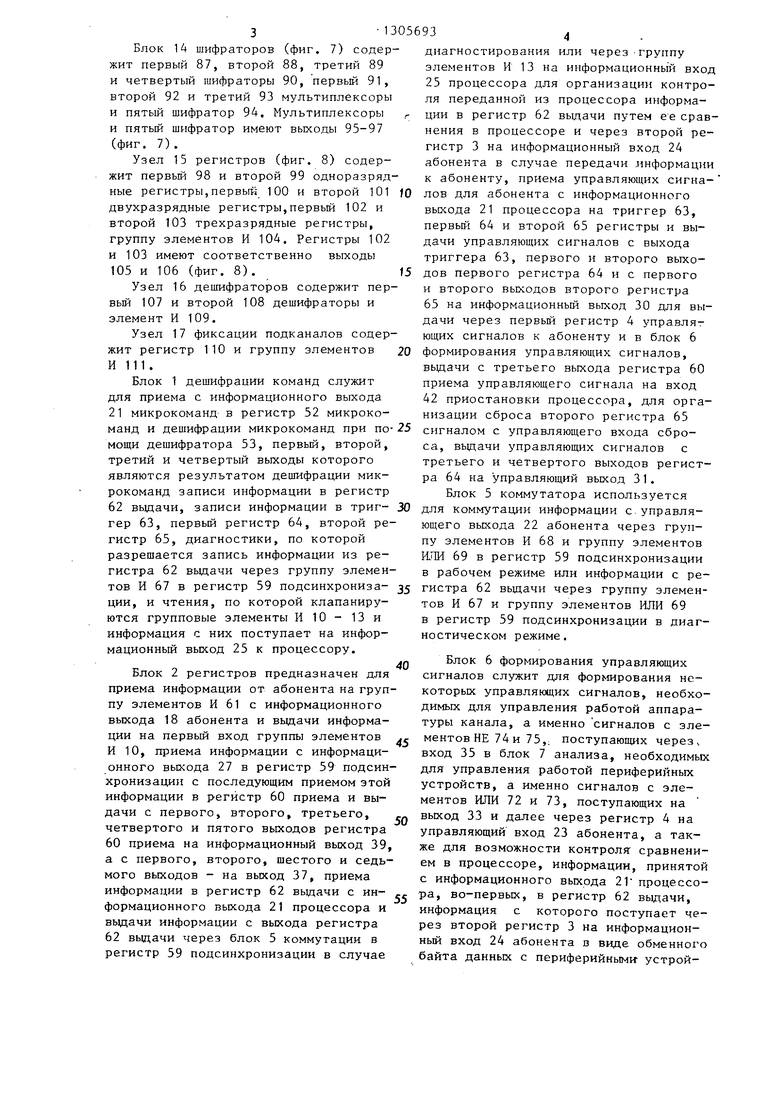

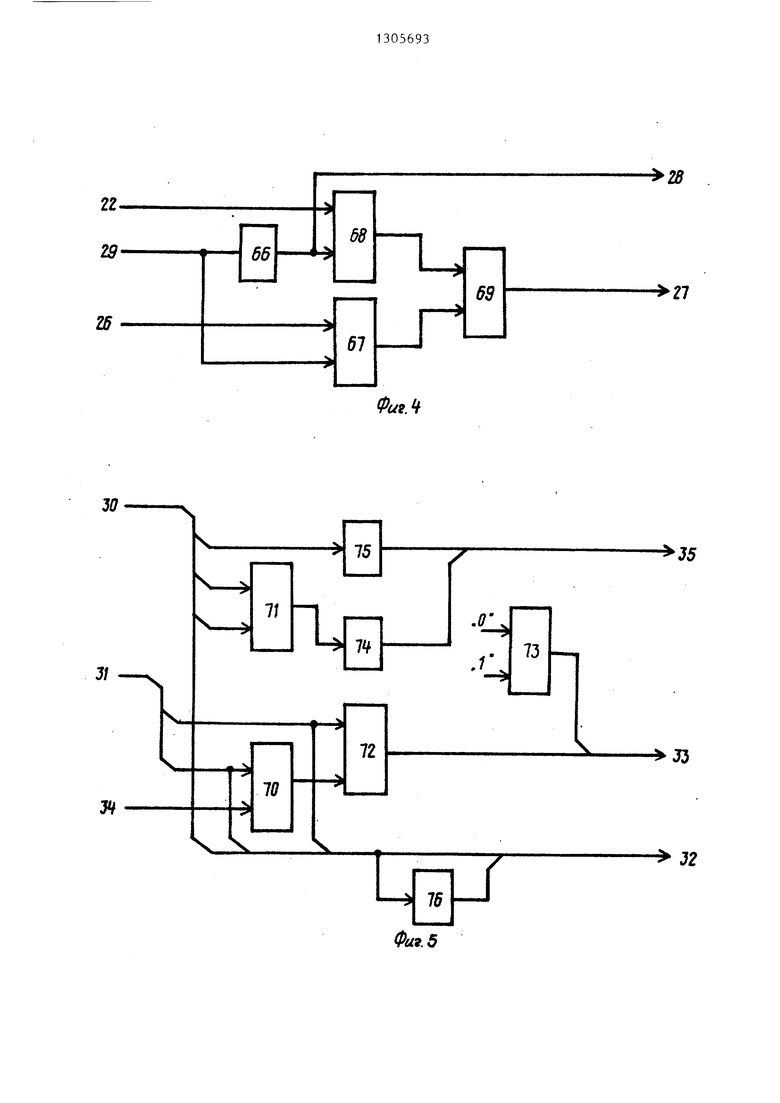

Блок 6 формирования управляющих сигналов (фиг, 5) содержит элемент И 70, первый 71, второй 72 и третий 73 элементы Ш1И, второй 74 и первый 75 элементы НЕ, узел 76 свертки по модулю два.

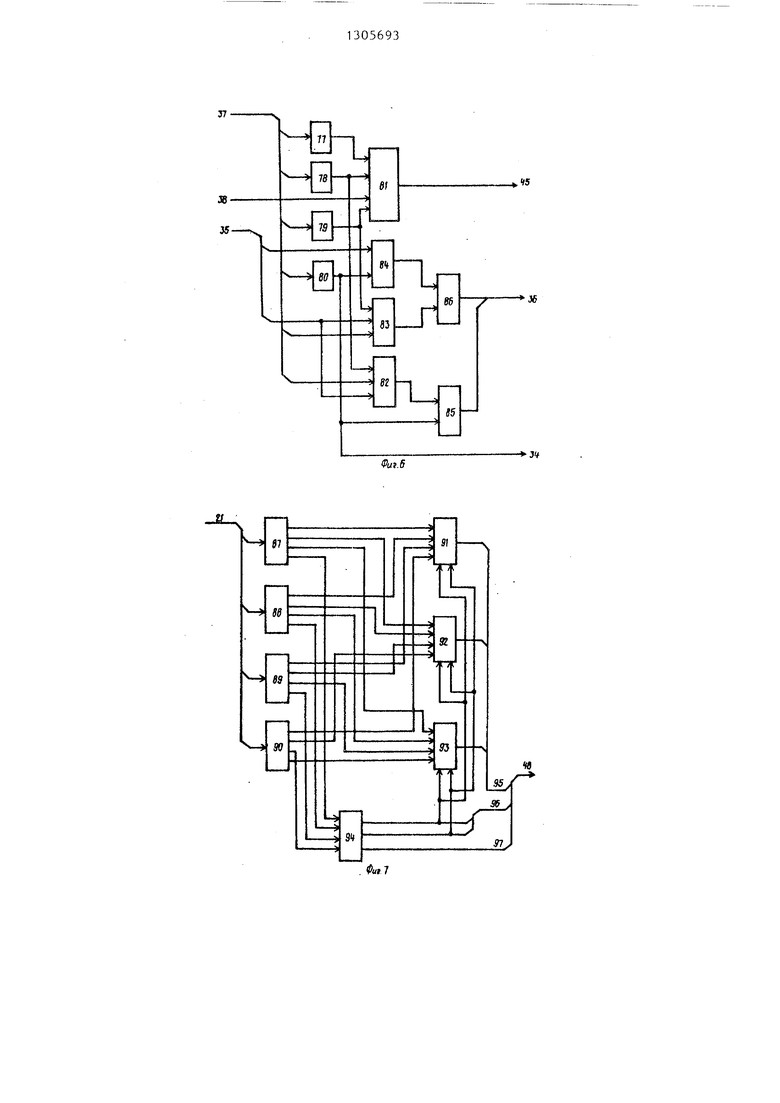

Блок 7 анализа (фиг. 6) содержит

процессора, управляющий выход 22 або- 55первый 77, второй 78, третий 79 и

нента, управляющий вход 23 абонента,четвертый 80 элементы НЕ , третий 81,

информационный вход 24 абонента, ин первый 82, второй 83 и четвертый 84

формационньш вход 25 процессора, ин-элементы И, первый 85 и второй 86

формационный . вход 26 блока коммута-элементы ИЛИ.

ции, первый информационный выход 27 блока коммутации, второй информационный выход 28 блока коммутации, первый управляющий вход 29 блока коммутации, первый выход 30 группы информационных разрядов блока-регистров, первый выход 31 группы управляющих разрядов блока регистров, первый выход 32 блока формирования, управляющих сигналов, второй выход 33 блока формирования управляющих сигналов, второй выход ЗА блока анализа, второй вход 35 блока анализа, третий выход 36 блока анализа, второй выход 37 группы управляющих разрядов блока регистров, выход 38 элемента НЕ, второй выход 39 группы информационных разрядов блока регистров, выход 40 узла свертки по модулю два, второй

ров, выход 42 приостановки процессора, третий выход 43 блока дешифрации команд, первый выход 44 блока дешифрации команд, первый выход 45 блока

анализа, четвертый выход 46 блока дешифрации команд, информационный выход 47 узла фиксации, информационный выход 48 блока шифраторов, второй информационный выход 49 и первый информационный выход 50 узла регистров, информационньш выход 51 узла дешифраторов.

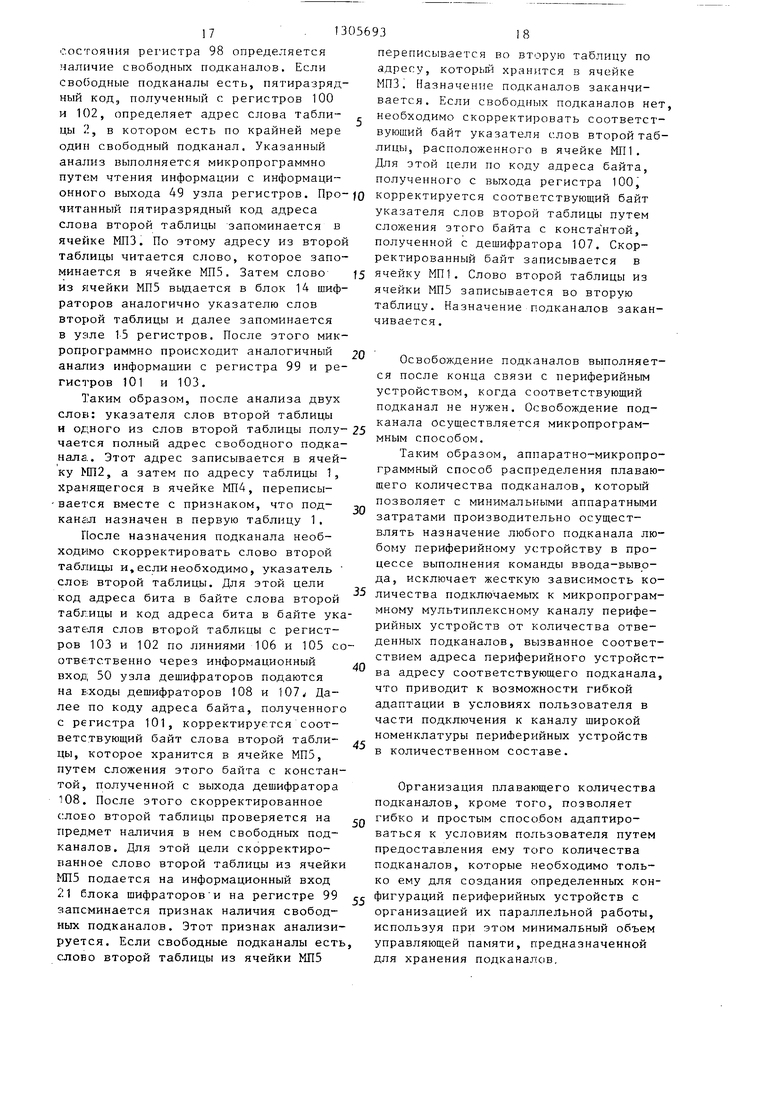

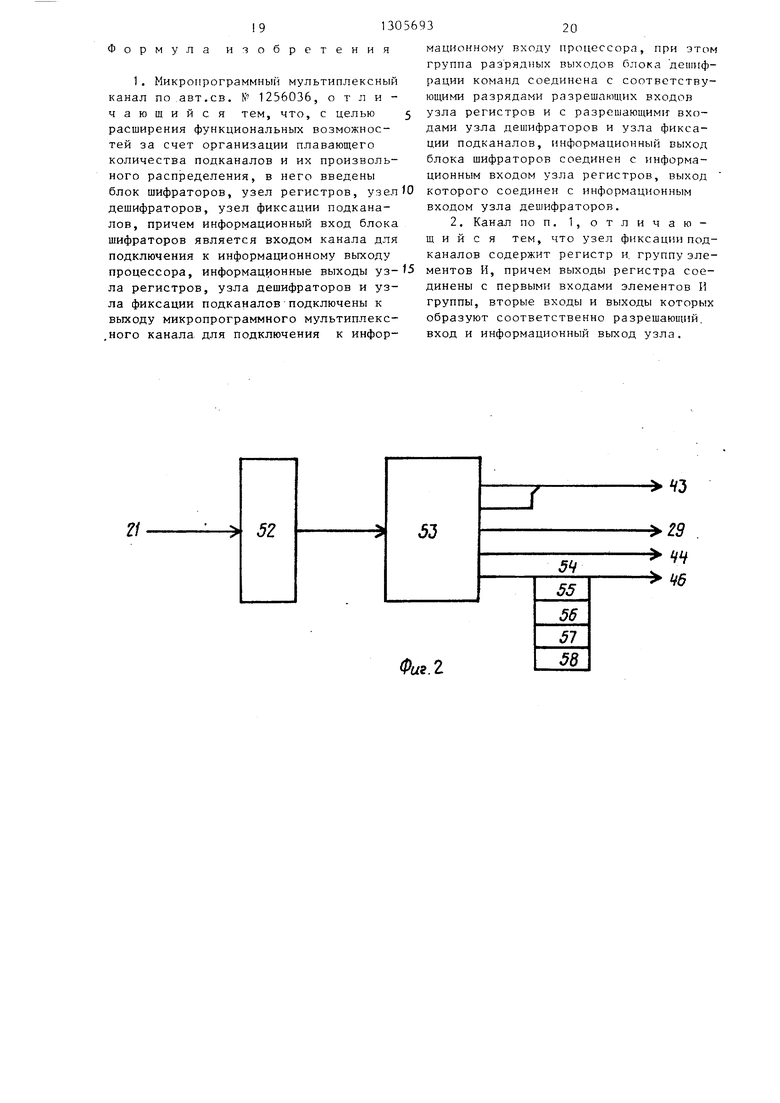

Блок 1 дешифрации команд (фиг. 2) содержит регистр 52 микрокоманд и дешифратор 53 микрокоманд. Дешифратор 53 микрокоманд имеет выходы 54-58.

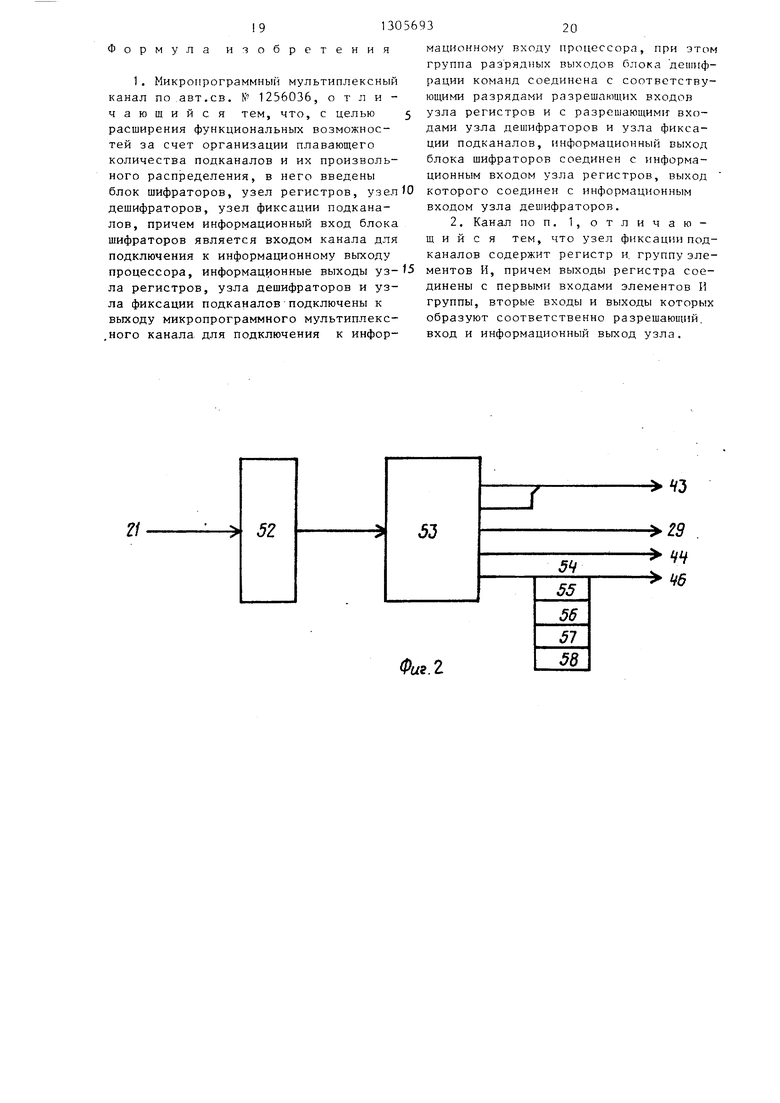

Блок 2 регистров (фиг. 3) содер- жит регистр 59 подсинхронизации, регистр 60 приема, группу элементов И

61, регистр 62 вьщачи, D-триггер 63, первый 64 и второй 65 регистры.

Блок 5 коммутации (фиг. 4) содержит элемент НЕ 66, две группы элементов И 67 и 68, группу элементов ИЛИ 69.

Блок 6 формирования управляющих сигналов (фиг, 5) содержит элемент И 70, первый 71, второй 72 и третий 73 элементы Ш1И, второй 74 и первый 75 элементы НЕ, узел 76 свертки по модулю два.

Блок 7 анализа (фиг. 6) содержит

3-1305693

Блок 14 шифраторов (фиг, 7) содержит первый 87, второй 88, третий 89 и четвертый шифраторы 90, первый 91, второй 92 и третий 93 мультиплексоры и пятый шифратор 94. Мультиплексоры ,- и пятый шифратор имеют выходы 95-97 (фиг. 7).

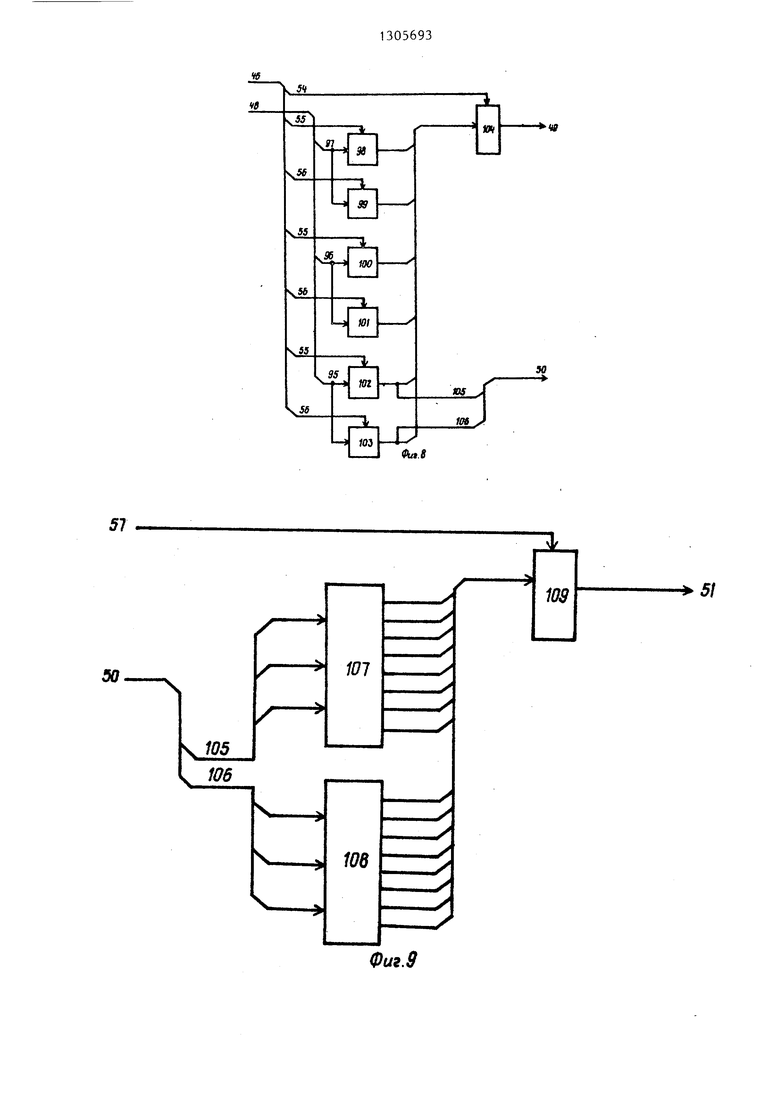

Узел 15 регистров (фиг. 8) содержит первый 98 и второй 99 одноразрядные регистры,первый 100 и второй 101 fO двухразрядные регистры,первый 102 и второй 103 трехразрядные регистры, группу элементов И 104. Регистры 102 и 103 имеют соответственно выходы 105 и 106 (фиг. 8).

Узел 16 дешифраторов содержит первый 107 и второй 108 дешифраторы и элемент И 109.

Узел 17 фиксации подканалов содержит регистр 110 и группу элементов И 111.

Блок 1 дешифрации команд служит для приема с информационного выхода 21 микрокоманд в регистр 52 микрокодиагностирования или через -группу элементов И 13 на информационный вход 25 процессора для организации контроля переданной из процессора информации в регистр 62 выдачи путем ее сравнения в процессоре и через второй регистр 3 на информационный вход 24 абонента в случае передачи .информации к абоненту, приема управляющих сигналов для абонента с информационного вьЕХОда 21 процессора на триггер 63, первый 64 и второй 65 регистры и выдачи управляющих сигналов с выхода триггера 63, первого и второго выходов первого регистра 64 и с первого и второго выходов второго регистра 65 на информационный выход 30 для выдачи через первьм регистр 4 управлят ющих сигналов к абоненту и в блок 6 20 формирования управляющих сигналов, выдачи с третьего выхода регистра 60 приема управляющего сигнала на вход 42 приостановки процессора, для организации сброса второго регистра 65

f5

манд и дешифрации микрокоманд при по- 25сигналом с управляющего входа сбромощи дешифратора 53, первый, второй,са, выдачи управляющих сигналов с

третий и четвертый выходы котороготретьего и четвертого выходов регистявляютс-я результатом дешифрации мик-ра 64 на управляющий выход 31. рокоманд записи информации в регистр Блок 5 коммутатора используется

62 вьщачи, записи информации в триг- 30для коммутации информации с.управлягер 63, первый регистр 64, второй ре-ющего выхода 22 абонента через групгистр 65, диагностики, по которойпу элементов И 68 и группу элементов

разрешается запись информации из ре-ИЛИ 69 в регистр 59 подсинхронизации

гистра 62 выдачи через группу элемен-в рабочем режиме или информации с ретов И 67 в регистр 59 подсинхрониза- 35гистра 62 вьщачи через группу элеменции, и чтения, по которой клапаниру-тон И 67 и группу элементов ИЛИ 69 ются групповые элементы И 10 - 13 и информация с них поступает на информационный выход 25 к процессору.

„ „40

Блок / регистров предназначен для

приема информации от абонента на группу элементов И 61 с информационного выхода 18 абонента и вьщачи информации на первый вход группы элементов ментов НЕ 74 и 75,; поступающих через. И 10, приема информации с информаци- вход 35 в блок 7 анализа, необходимых онного выхода 27 в регистр 59 подсинхронизации с последующим приемом этой информации в регистр 60 приема и выдачи с первого, второго, третьего.

в регистр 59 подсинхронизации в диагностическом режиме.

Блок 6 формирования управляющих сигналов служит для формирования некоторых управляющих сигналов, необходимых для управления работой аппаратуры канала, а именно сигналов с зле50

для управления работой периферийных устройств, а именно сигналов с элементов ИЛИ 72 и 73, поступающих на выход 33 и далее через регистр 4 на управляющий вход 23 абонента, а также для возможности контроля сравнением в процессоре, информации, принятой с информационного выхода 21 процессо- сс ра, во-первых, в регистр 62 вьщачи, информация с которого поступает через второй регистр 3 на информационный вход 24 абонента в виде обменного байта данных с периферийными- устройчетвертого и пятого выходов регистра 60 приема на информационный выход 39, а с первого, второго, шестого и седьмого выходов - на выход 37, приема информации в регистр 62 вьщачи с информационного выхода 21 процессора и вьщачи информации с выхода регистра 62 вьщачи через блок 5 коммутации в регистр 59 подсинхронизации в случае

-

O

диагностирования или через -группу элементов И 13 на информационный вход 25 процессора для организации контроля переданной из процессора информации в регистр 62 выдачи путем ее сравнения в процессоре и через второй регистр 3 на информационный вход 24 абонента в случае передачи .информации к абоненту, приема управляющих сигна лов для абонента с информационного вьЕХОда 21 процессора на триггер 63, первый 64 и второй 65 регистры и выдачи управляющих сигналов с выхода триггера 63, первого и второго выходов первого регистра 64 и с первого и второго выходов второго регистра 65 на информационный выход 30 для выдачи через первьм регистр 4 управлят ющих сигналов к абоненту и в блок 6 0 формирования управляющих сигналов, выдачи с третьего выхода регистра 60 приема управляющего сигнала на вход 42 приостановки процессора, для организации сброса второго регистра 65

5

тон И 67 и группу элементов ИЛИ 69

ментов НЕ 74 и 75,; поступающих через. вход 35 в блок 7 анализа, необходимых

в регистр 59 подсинхронизации в диагностическом режиме.

Блок 6 формирования управляющих сигналов служит для формирования некоторых управляющих сигналов, необходимых для управления работой аппаратуры канала, а именно сигналов с зле ментов НЕ 74 и 75,; поступающих через. вход 35 в блок 7 анализа, необходимых 0

для управления работой периферийных устройств, а именно сигналов с элементов ИЛИ 72 и 73, поступающих на выход 33 и далее через регистр 4 на управляющий вход 23 абонента, а также для возможности контроля сравнением в процессоре, информации, принятой с информационного выхода 21 процессо- сс ра, во-первых, в регистр 62 вьщачи, информация с которого поступает через второй регистр 3 на информационный вход 24 абонента в виде обменного байта данных с периферийными- устрой15

CTB.aMHj a также для контроля сравне- нием в процессоре через группу элементов И 13 на информационньй вход 25 процессора и, во-вторых,.в триг- гер 63, регистры 64 и 65, с выходов которых информация поступает в блок 6 формирования управляющих сигналов, где эта информация поступает с выходов 30 и 31 на элемент 76 для формирования к этой информации контрольно-JQ го разряда и на выход 32 вместе с конт-- рольным разрядом с выхода элемента 76 и через группу элементов И 12 на информационный вход 25 процессора.

Блок 7 анализа используется для выработки управляющих сигналов с выхода элемента И 81 и с элемента НЕ 80, которые через выходы 45 и 34 поступают на сбросовый вход регистра 65 и на второй вход элемента И 70 соответственно с целью исключения микропрограммного анализа наиболее часто участвующих в управлении управляющих сигналов, что сокращает объем канальных микропрограмм и, следовательно, 25 время их выполнения, а также формирования определенной комбинации управляющих сигналов, получаемых с выходов элементов ИЛИ 85 и 86, которые поступают в процессор через группу JQ элементов И 11, после анализа которых микропрограммным путем канальная микропрограмма определяет состояние трех управляющих сигналов, за счет

20

чего сокращается объем канальных мик- , но первые, вторые и третьи адресные

ропрограмм и, следовательно, время их выполнения.

Элемент НЕ 8 используется для инверсии принятого с синхровхода 20 синхронизирующего сигнала о дальнейшем использовании прямого и инверсного синхронизирующих сигналов для управления приемом информации в регистре 59 и 60 блока 2 регистров и для выработки в определенное время управляющего сигнала с выхода элемента И 81 в блоке 7 анализа.

Узел 9 свертки по модулю два служит для формирования контрольного

40

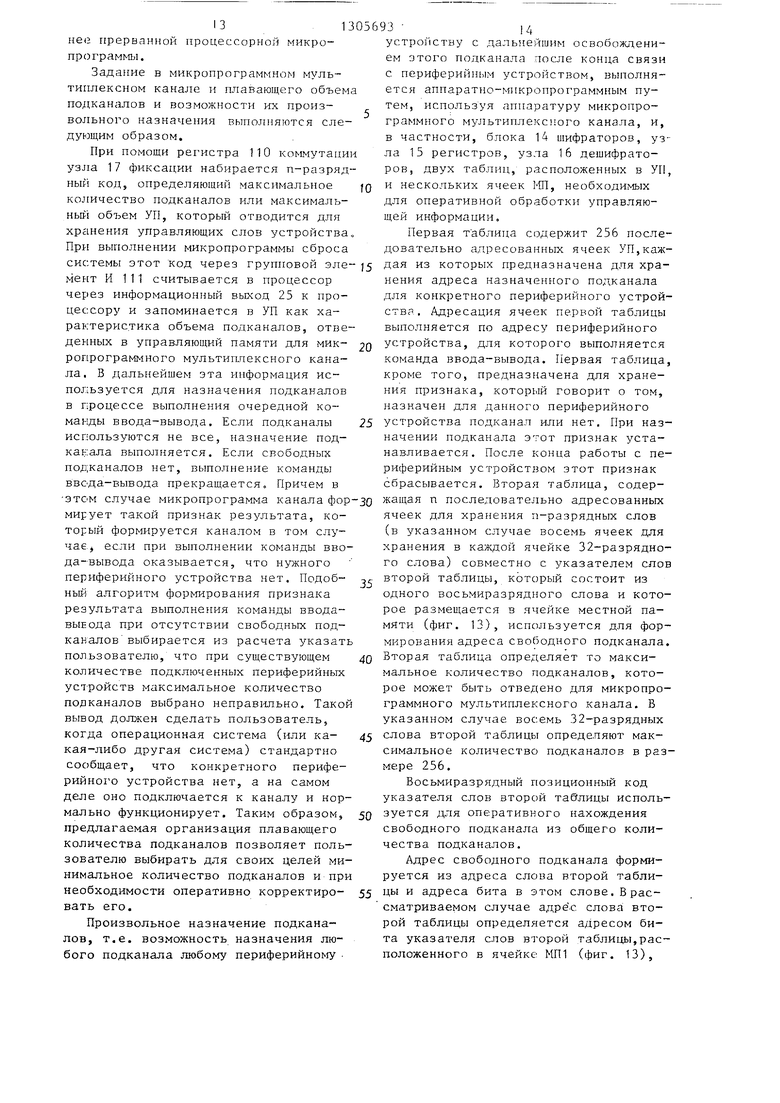

выходы щифраторов 87-90, и выдачи с выходов мультиплексоров 91-93, с ад ресного и управляющего выходов щиф- ратора 94 на информационньй выход 4 блока трех-, двух-и одноразрядного кодов соответственно.

Узел 15 регистров используется дл хранения на регистрах 98-103 информа ции, полученной с информационного входа 48, а также выдачи информации с регистров 98-103 через группу элементов И 104 под управлением управляющего сигнала с выходов 54, полученного с выхода дешифратора 53, на

разряда к информации, которая посту- Q первый информационный выход 49 и с

пает на его вход из блока 7 анализа и блока 2 регистров соответственно, и вьщачи этого контрольного разряда на первьй вход группы элементов И 11.

Группы элементов И 10-13 используются для коммутации при помощи управляющего сигнала, поступающего с выхода 44 дешифрации, информации,пос- тупаЬщей из блока 2. регистров с вывыходов регистров 102 и 103 на второй информационный выход 50.

Узел 16 дешифраторов предназначе для формирования соответствующих ко сс стант путем дешифрации на дешифрато рах 107 и 108 трехразрядной информа ции, поступающей на входы дешифрато ров 107 и 108 с информационного вхо да 50 и выдачи этих констант через.

хода группового элемента И 61 на первый вход четвертой группы элементов И 10, блока 2 регистров с выхода регистра 60 приема через информационный выход 39, из блока 7 анализа с элементов ИЛИ 85 и 86 и с выхода 40 на первый вход третьей группы элемен5

5 Q

тов И 1 1

блока 6 формирования с первьш вход второй груп- И 12, из блока 2 регист0

из

вькода 32 на пы элементов ров с выхода регистра 62 выдачи на первьй вход первой группы элементов И 13 с последующей одновременной выдачей с выходов групп элементов И 10- 13 информации на информационньй вход 25 процессора.

Блок 14 шифраторов предназначен для формирования адреса свободного подканала, которьй выполняется путем анализа на наличие нулевых бит в че- тьфех байтах информационного слова, поступающего с информационного выхода 21 процессора побайтно на информационные входы шифраторов 87-90, и формирования первого нулевого бита в информационном слове, начиная, например, с нулевого бита, при помощи пятого шифратора 94, на первьй - четвертый информационные входы которого поступают управляющие выходы с шифраторов 87-90 соответственно, и при помощи трех мультиплексоров 91-93, на первьй - четвертый информационные входы которых поступают соответствен

0

выходы щифраторов 87-90, и выдачи с выходов мультиплексоров 91-93, с адресного и управляющего выходов щиф- ратора 94 на информационньй выход 48 блока трех-, двух-и одноразрядного кодов соответственно.

Узел 15 регистров используется для хранения на регистрах 98-103 информации, полученной с информационного входа 48, а также выдачи информации с регистров 98-103 через группу элементов И 104 под управлением управляющего сигнала с выходов 54, полученного с выхода дешифратора 53, на

первый информационный выход 49 и с

выходов регистров 102 и 103 на второй информационный выход 50.

Узел 16 дешифраторов предназначе н для формирования соответствующих кон- стант путем дешифрации на дешифраторах 107 и 108 трехразрядной информации, поступающей на входы дешифрато-, ров 107 и 108 с информационного входа 50 и выдачи этих констант через.

групповой элемент И 109 под управлением управляющего сигнала с входа 57, полученного с выхода дешифратора 53, на информационный выход 51,

Узел 17 фиксации предназначен для задания при помощи регистра 110 коммутации конкретного количества подканалов путем набора при помощи переключателей определенного кода на регистре 110 коммутации и выдачи этого кода через групповой элемент И 111 под управлением управляющего сигнала 58, полученного с выхода дещифратора 53, на информационный выход 47.

Микропрограммный (мультиплексный канал работает под управлением канальных микропрограмм, расположенных совместно с процессорными микропрограммами в памяти микропрограмм (управляющей памяти). Это позволяет в любой20 ти для хранения всех управляющих слово

момент времени выполнять или микропрограммы процессора, или микропрограммы мультиплексного канала.

Микропрограммы мультиплексного канала являются более приоритетными по отнощению к процессорным микропрограммам. Как только возникает необходимость в выполнении канальных микропрограмм процессорные микропрограммы

немедленно приостанавливаются и начи-30 устройства. Извлечение из управляюнается выполнение канальных микропрограмм. После их выполнения выполнение процессорных микропрограмм продолжается.

Операция ввода-вывода в микропро- граммном мультиплексном канале начинается по специальной команде процессора, которая задает адреса канала и периферийного устройства и при помощи специальных управляющих слов ка- нала, которые указываются или в проблемной программе, или формируются при помощи специальной управляющей прогщей памяти управляющее сло ется в местную память проц при необходимости обратно ется в управляющую память. разом, возможность одновре боты канала с несколькими ными устройствами определя чеством управляющих слов, гут храниться в управляюще т.е. объемом управляющей п количеством подканалов, от для хранения управлякяцих с ной памяти используется ст ек, сколько необходимо для

раммы (например, супервизор ввода-вывода), указывает код команды, началь- 45 одного управляющего слова, ный адрес оперативной памяти для организации обмена данными, количество передаваемых байт данных и другие управляющие признаки, по которым под управлением специальной канальной 50 микропрограммы формируется управляющее слово устройства.

После формирования упра слова устройства канальная рамма начинает организовыв с периферийным устройством том) по стандартному интер да-вывода. При этом инфор байт данных вместе с контр рядом из процессора переда ненту через информационный от процессора, регистр 62 второй информационный выхо 2 регистров и регистр 3. У идентификаторы канала из п

Формирование управляющего слова устройства выполняется с использованием нескольких ячеек в местной памяти процессора, построенной на полупроводниковых запоминающих элементах, быстродействие которых соизмеримо с

быстродействием регистровой памяти, что позволяет значительно сократить время работы канальных микропрограмм, С этой целью управляющее слово устройства, если его необходимо сохранить, переписывается из местной памяти процессора не в оперативную память, а в управляющую, быстродействие которой гораздо выше оперативной памяти.

Так как канал может работать с несколькими периферийными устройствами (абонентами) одновременно, то для каждого абонента необходимо сохранять

его управляющее слово. Для этой цели в управляющей памяти отводится специальная область для хранения управляющего слова для каждого абонента.Причем общая область в управляющей памяотводится таким образом, чтобы выборку управляющих слов из управляющей памяти можно было организовать по адресу периферийного устройства, совмещенного с определенной базой, определяющей начало массива. Это позволяет простым способом быстро извлекать из управляющей памяти управляющее слово для конкретного периферийного

щей памяти управляющее слово помещается в местную память процессора и при необходимости обратно переписывается в управляющую память. Таким образом, возможность одновременной работы канала с несколькими периферийными устройствами определяется количеством управляющих слов, которые могут храниться в управляющей памяти, т.е. объемом управляющей памяти или количеством подканалов, отведенной для хранения управлякяцих слов, В местной памяти используется столько ячеек, сколько необходимо для хранения

одного управляющего слова,

одного управляющего слова,

После формирования управляющего слова устройства канальная микропрограмма начинает организовывать связь с периферийным устройством (абонентом) по стандартному интерфейсу ввода-вывода. При этом информационный байт данных вместе с контрольным разрядом из процессора передается к абоненту через информационный вход 21 от процессора, регистр 62 вьщачи во второй информационный выход 26 блока 2 регистров и регистр 3. Управляющие идентификаторы канала из процессора

9. 1305693

переданЗтся к абоненту через информа- цион,:$ый вход 21 ОТ процессора, триггер 63, регистры 62,64 и 65, информационные выходы 26 и 30 блока 2 ре- и с выходов элемента ИЛИ 73 и 72 через выход 33 блока 6 формирования управляющих сигналов и далее через регистр 4 на управляющий выход 23 к абоненту. Причем с выхода триггера 63 выдается индентификатор ра- 10 боты от канала РАБ-К, с первого по четвортьпЧ выходы регистра 64 вьщают- ся идентификаторы распространения выборки от канала РВК-К, адрес от канала АДР-К, прерывания ПРЕР, блокиров- 15 ных идентификаторов, ка от канала БЛК-К, соответственно Установка всех идентификаторов от

0

с переданной. Этот контроль выполняется в процессе работы канала при пе редаче данных из процессора к абонен ту, .

Контроль работы оборудования кана ла, связанного с передачей данных из абонента в процессор, осуществляется в диагностическом режиме путем занесения в регистр 60 приема фиктивных идентификаторов от абонента через ре гистр 62 выдачи и блок 5 коммутации с дальнейшим анализом снятых с групп элементов И 12 и информационного выхода 25 к процессору заранее известс первого и второго выходов регистра 65 выдаются индентификаторы управления от канала УПР-К и информация от канала ИНФ-К.

Информационньш байт данных вместе с контрольным разрядом от абонент-а к процессору поступает с информационного входа 18 от абонента через группу элементов И 61 и группу элементов И 10 и информацис1нный выход 25 к процессору. Управляющие сигналы от абонента к процессору поступают с группового управляющего входа 22 от абонента через группу элементов И 68, группу элементов ИЛИ 69 в блок 2 ре- rHCTjioB по информационному входу 27 и далее через регистр 59 подсинхрони- зации, регистр 60 приема, через ин20

25

30

канала, кроме идентификатора выборк от канала ВБР-К, выполняется микропрограммным путем. Установка идентификатора РАБ-К выполняется еще и управляющим сигналом при включении питания процессора по управляющему вхо ду 19 включения питания. Установка сигнала ББР-К выполняется автоматически при включении питания и вьщает ся с элемента ИЛИ 73 на соответствую щий разряд регистра - усилителя 4 по тоянно.

Сброс всех идентификаторов от канала также выполняется микропрограммным путем. Однако наиболее часто встречающиеся идентификаторы УПР-К и ИНФ-К могут сбрасываться аппаратным путем в процессе работы канала

, - on с т 35 при связи с абонентом. Аппаратный

форма.ционныи выход 39 блока 2регист- ;,

„„--„ сброс идентификаторов выполняется в

ров и с выходов элементов ИЛИ85 и

регистре 65 путем выработки сигнала сброса с элемента И 81, который порегистре 65 путем выработки сигнала сброса с элемента И 81, который по86 через информационньм выход 36 блока 7 анализа вместе со сформированным

,,является на выходе этого элемента

на узле У контрольным разрядом через ,,,,.

„ ,40 при отсутствии идентификаторов от

группу элементов И 11 и информационный выход 25 к процессору. Причем с первого, второго, третьего, четвертого, пятого, шестого и седьмого выхоабонента АДР-А, УПР-А и ИНФ-А и отсутствии синхросигнала, поступающего из процессора в канал через син,„хровыход 38 на четвертый вход эле- дов регистра 60 приема выдаются иден- .. „он

, ТЛАГ1 л - мента И 81 . тификаторы работы от абонента РАБ-А,

адрес от абонента АДР-А, выборка от абонента ВБР-А, требование от абонента TFB-A,отключение от абонента ОТК-А, управление от абонента УПР-А и информация от абонента ИНФ-А соответственно. Контроль переданной информации из процессора в канал по информационному входу 21 от процессора и пра- ; вильность работы связанной с этой пе- „ УПР-К и ИНФ-К в канале аппаратно фор- редачей оборудования канала выполни- мируются два специальных-управляющих ются, путем возврата этой информации сигнала - сигнал А с выхода элемента в процессор через группы элементов И ИЛИ 85 и сигнал В с выхода элемента 12 и 13 и ее сравнения в процессоре ИЛИ 86, комбинации которых, анализи50

Наличие или отсутствие идентификаторов от абонергта анализируется микропрограммным путем. Однако для более быстрого анализа часто используемых в управлении идентификаторов от абонента РАБ-А,- АДР-А, ИНФ-А и УПР-А в комбинации с наличием или отсутствием идентификаторов от {санала АДР-К,

ных идентификаторов, Установка всех идентификаторов от

0

с переданной. Этот контроль выполняется в процессе работы канала при передаче данных из процессора к абоненту, .

Контроль работы оборудования канала, связанного с передачей данных из абонента в процессор, осуществляется в диагностическом режиме путем занесения в регистр 60 приема фиктивных идентификаторов от абонента через регистр 62 выдачи и блок 5 коммутации с дальнейшим анализом снятых с группы элементов И 12 и информационного выхода 25 к процессору заранее извест0

5

0

канала, кроме идентификатора выборки- от канала ВБР-К, выполняется микропрограммным путем. Установка идентификатора РАБ-К выполняется еще и управляющим сигналом при включении питания процессора по управляющему входу 19 включения питания. Установка сигнала ББР-К выполняется автоматически при включении питания и вьщает- ся с элемента ИЛИ 73 на соответствующий разряд регистра - усилителя 4 постоянно.

Сброс всех идентификаторов от канала также выполняется микропрограммным путем. Однако наиболее часто встречающиеся идентификаторы УПР-К и ИНФ-К могут сбрасываться аппаратным путем в процессе работы канала

регистре 65 путем выработки сигнала сброса с элемента И 81, который по„ УПР-К и ИНФ-К в канале аппаратно фор- мируются два специальных-управляющих сигнала - сигнал А с выхода элемента ИЛИ 85 и сигнал В с выхода элемента ИЛИ 86, комбинации которых, анализи0

Наличие или отсутствие идентификаторов от абонергта анализируется микропрограммным путем. Однако для более быстрого анализа часто используемых в управлении идентификаторов от абонента РАБ-А,- АДР-А, ИНФ-А и УПР-А в комбинации с наличием или отсутствием идентификаторов от {санала АДР-К,

руемые одной микрокомандой в процессоре, идентичны анализу трех идентификаторов от абонента РАБ-А, УПР-А, ИНФ-А, для анализа которых требуется три микрокоманды.

В таблице указаны комбинации сигналов А и В.

ОРАБ-А установлено

0ИНФ-А установлено

1УПР-А установлено 1РАБ-А снято

Кроме того, если в канале есть конечное прерывание типа Канал кончил, что анализируется микропрограммным путем, микропрограммно в регистре 64 устанавливается признак прерывания, которьй с третьего выхода регистра 64 поступает через вход 31 блока формирования управляющих сигналов на первьш вход элемента И 70, на

второй вход которого поступает инверс-35 принимает байт данных и устанавливает

ный идентификатор РАБ-А. Таким образом, идентификатор БЛК-К автоматически формируется в канале и выдается к абоненту при отсутствии идентификатора РАБ-А до тех пор, пока не обрабо- тается конечное прерывание, т.е. пока не снимется сигнал прерывания микропрограммным путем.

Идентификатор от абонента ТРБ-А с четвертого выхода регистра 60 через вход 42 приостановки поступает в процессор. В конце каждой микрокоманды процессор анализирует наличие этого сигнала и, если он есть, приостанав-

ливает выполнение процессорных микро- 50 ных и т.д. Если комбинация сигналов

программ и начинает выполнение канальных микропрограмм.

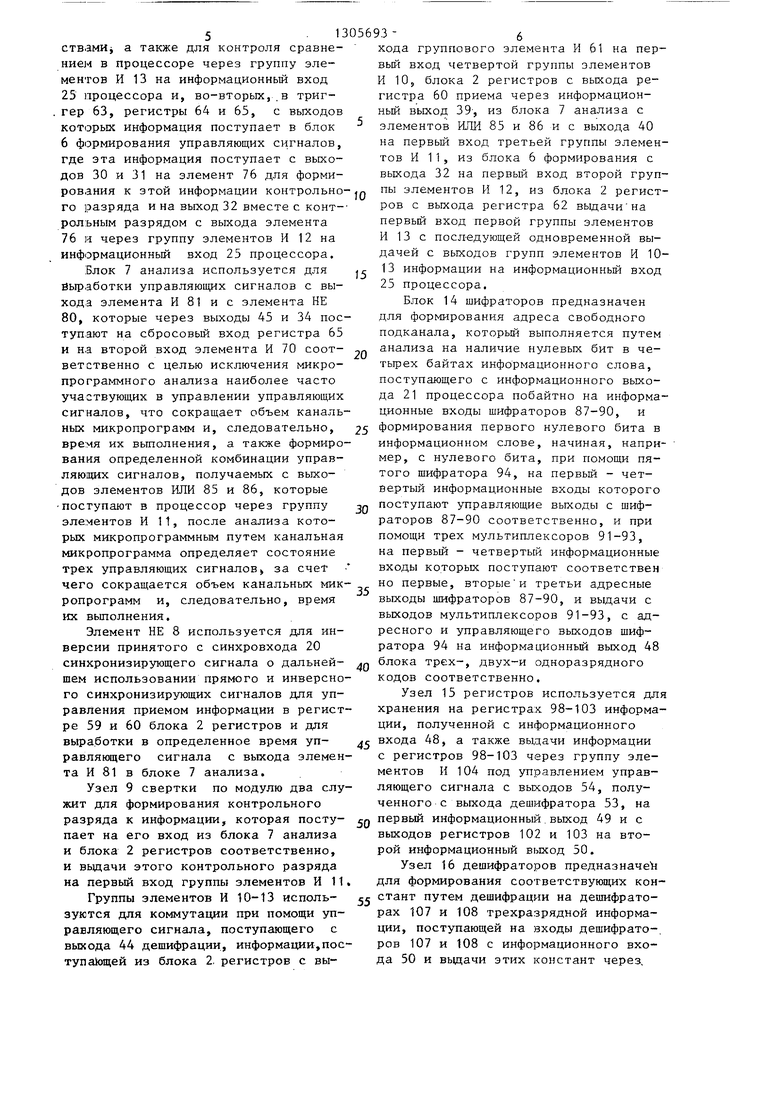

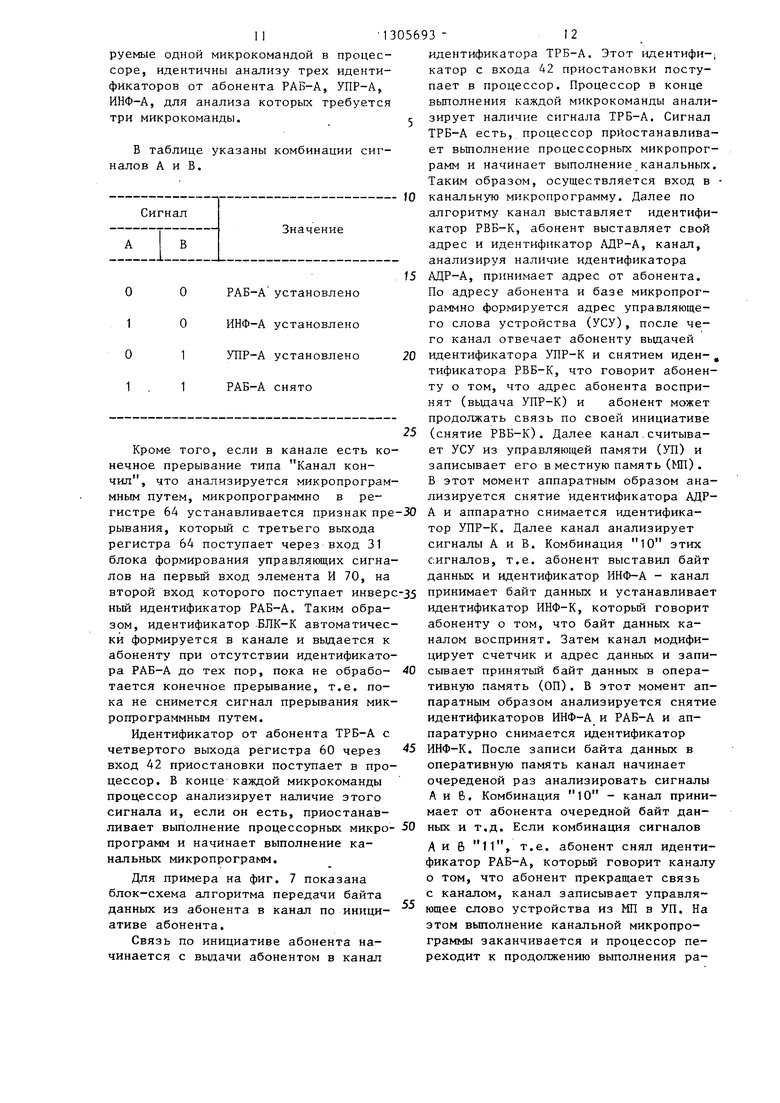

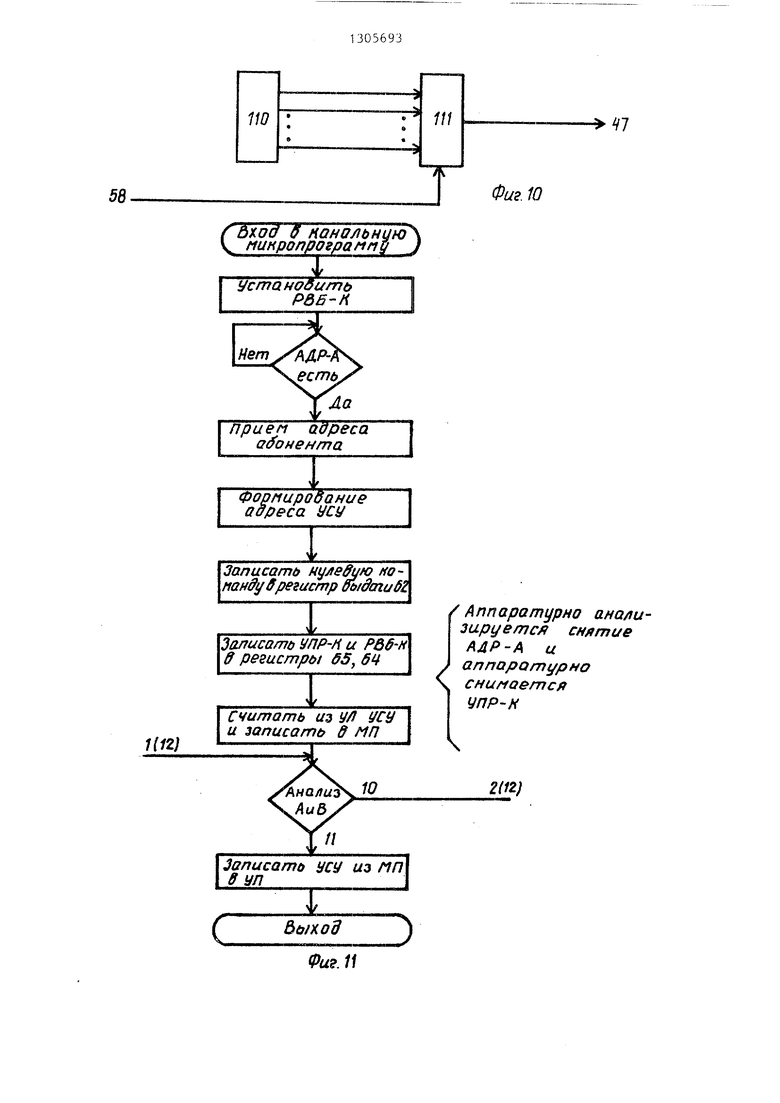

Для примера на фиг. 7 показана блок-схема алгоритма передачи байта данных из абонента в канал по инициативе абонента.

Связь по инициативе абонента начинается с выдачи абонентом в канал

я

5

- fO

f5

оме30аа

1305693 -12

идентификатора ТРБ-А. Этот идентифи- катор с входа 42 приостановки поступает в процессор. Процессор в конце выполнения каждоЕ1 микрокоманды анализирует наличие сигнала ТРБ-А, Сигнал ТРБ-А есть, процессор приостанавливает вьшолнение процессорных микропрограмм и начинает выполнение канальных. Таким образом, осуществляется вход в - канальную микропрограмму. Далее по алгоритму канал выставляет идентификатор РВБ-К, абонент выставляет свой адрес и идентификатор АДР-А, канал, анализируя наличие идентификатора АДР-А, принимает адрес от абонента. По адресу абонента и базе микропрограммно формируется адрес управляющего слова устройства (УСУ), после чего канал отвечает абоненту выдачей идентификатора УПР-К и снятием иден- , тификатора РВБ-К, что говорит абоненту о том, что адрес абонента воспринят (вьщача УПР-К) и абонент может продолжать связь по своей инициативе (снятие РВБ-К). Далее канал.считывает УСУ из управляющей памяти (УП) и записывает его в местную память (МП). В этот момент аппаратным образом анализируется снятие идентификатора АДР- А и аппаратно снимается идентификатор УПР-К. Далее канал анализирует сигналы А и В. Комбинация 10 этих сигналов, т.е. абонент выставил байт данных и идентификатор ИНФ-А - канал

20

25

идентификатор ИНФ-К, который говорит абоненту о том, что байт данных каналом воспринят. Затем канал модифицирует счетчик и адрес данных и записывает принятый байт данных в оперативную память (ОП). В этот момент аппаратным образом анализируется снятие идентификаторов ИНФ-А и РАБ-А и ап- паратурно снимается идентификатор ИНФ-К. После записи байта данных в оперативную память канал начинает очереденой раз анализировать сигналы А и 6. Комбинация 10 - канал принимает от абонента очередной байт дан

АИ 6 11, т.е. абонент снял идентификатор РАБ-А, которьй говорит каналу о том, что абонент прекращает связь с каналом, канал записывает управляющее слово устройства из МП в УП. На этом выполнение канальной микропрограммы заканчивается и процессор переходит к продолжению выполнения ранее прерванной процессорной микропрограммы.

Задание в микропрограммном мультиплексном канале и плавающего объема подкан;1лов и возможности их произвольного назначения выполняются следующим образом.

При помощи регистра 110 коммутации узла 17 фиксации набирается п-разряд- ный код, определяющий максимальное количество подканалов или максималь- Hbtt объем УП, который отводится для хранения управляющих слов устройства„ Пр выполнении микропрограммы сброса

системы этот код через групповой эле- )5 дая из которых предназначена для храмент И 111 считывается в процессор через информационный вькод 25 к процессору и запоминается в УП как характеристика объема подканалов, отве- в управляющий памяти для микропрограммного мультиапексного канала, В дальнейшем эта информация ис- пох;ьзуется для назначения подканалов в процессе выполнения очередной команды ввода-вывода. Если подканалы используются не все, назначение подканала выполняется. Если свободных подканалов нет, выполнение команды ввода-вывода прекращается. Причем в

этом случае микропрограмма канала фор-зо жащая п последовательно адресованных

мирует такой признак результата, который формируется каналом в том слу- чае, если при выполнении команды ввода-вывода оказывается, что нужного периферийного устройства нет. Подобный алгоритм формирования признака результата выполнения команды ввода- при отсутствии свободньгх подканалов выбирается из расчета указать пользователю, что при существующем количестве подключенных периферийных устройств максимальное количество подканалов выбрано неправильно. Такой вывод должен сделать пользователь, когда операционная система (или какая-либо другая система) стандартно сос бщает, что конкретного перифе- рийно1 о устройства нет, а на самом деле оно подключается к каналу и нормально функционирует. Таким образом, предлагаемая организация плавающего количества подканалов позволяет пользователю выбирать для своих целей минимальное количество подканалов и при необходимости оперативно корректировать его.

Произвольное назначение подканалов, т.е. возможность назначения любого подканала любому пepифepийнo ry .

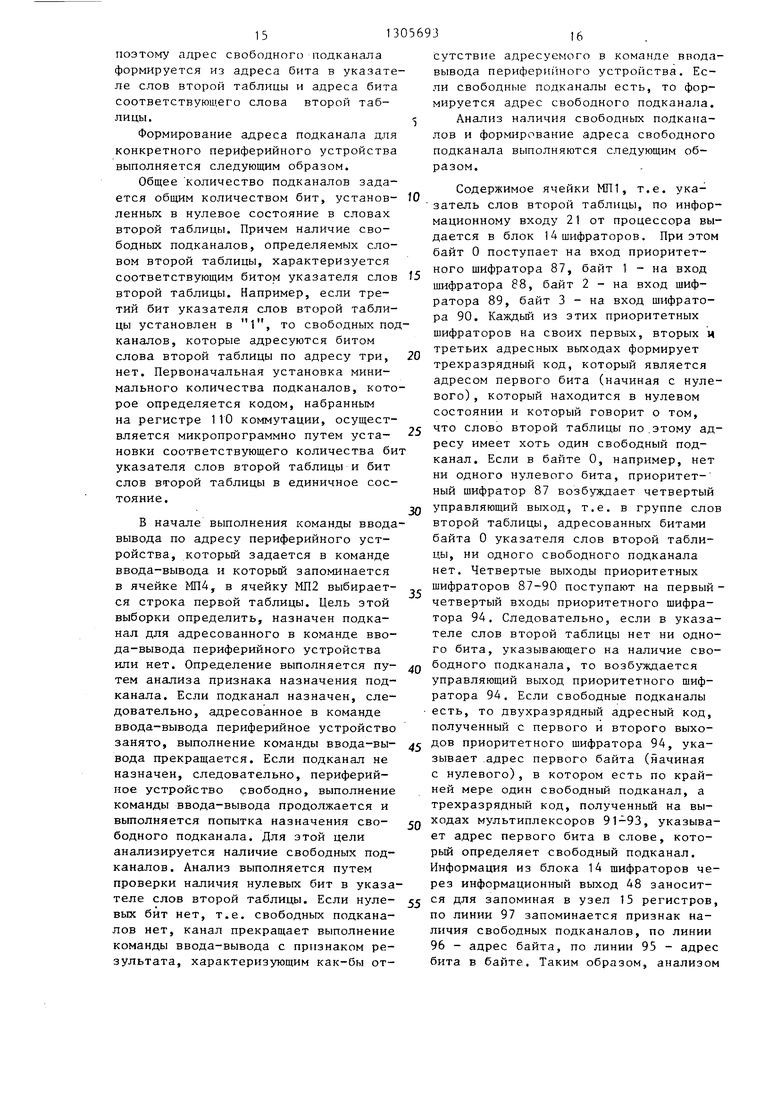

устройству с дальнейшим освобождением этого подканала после конца связи с периферийным устройством, выполняется аппаратно-микропрограммным путем, используя аппаратуру микроцро- граммного мультиплекс1:ого канала, и, в частности, блока 14 шифраторов, узла 15 регистров, узла 16 дешифраторов, двух таблиц, расположенных в УП, и нескольких ячеек lill, необходимых для оперативной обработки управляющей информации.

Первая таблица содержит 256 последовательно адресованных ячеек УП,кажнения адреса назначенного подканала для конкретного периферийного устройства. Адресация ячеек первой таблицы выполняется по адресу периферийного

устройства, для которого выполняется команда ввода-вывода. Первая таблица, кроме того, предназначена для хранения признака, который говорит о том, назначен для данного периферийного

устройства подканал или нет. При назначении подканала этот признак устанавливается. После конца работы с периферийным устройством этот признак сбрасывается. Вторая таблица, содер5

0

5

0

5

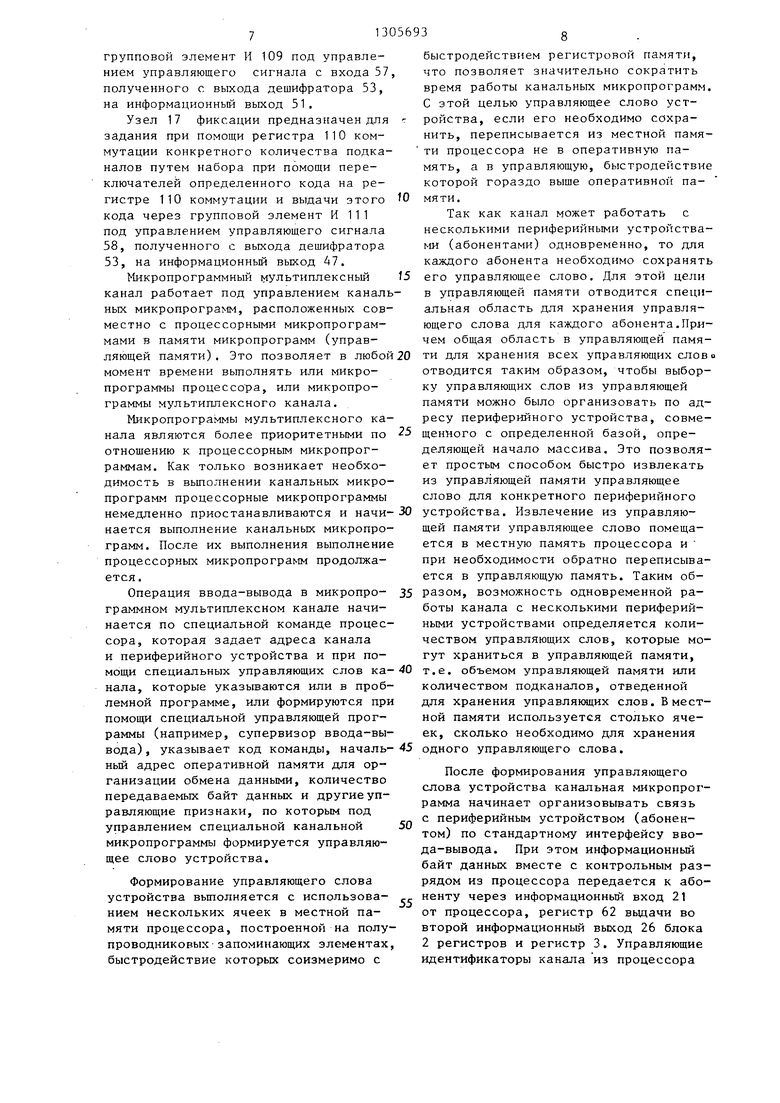

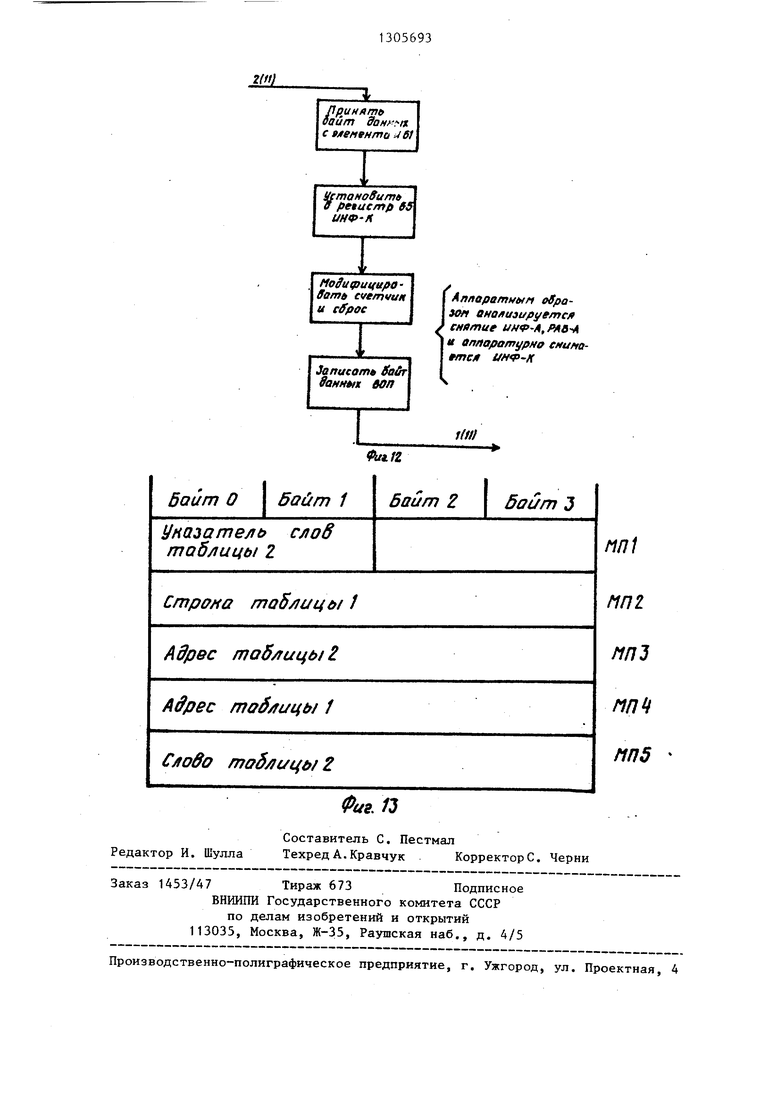

ячеек для хранения п-разрядных слов (в указанном случае восемь ячеек для хранения в каждой ячейке 32-разрядного слова) совместно с указателем слов второй таблицы, который состоит из одного восьмиразрядного слова и которое размещается в ячейке местной памяти (фиг. 13), используется для формирования адреса свободного подканала. Вторая таблица определяет то максимальное количество подканалов, которое может быть отведено для микропрограммного мультиплексного канала. В указанном случае восемь 32-разрядных слова второй таблицы определяют максимальное количество подканалов в размере 256.

Восьмиразрядный позиционный код указателя слов второй таблицы используется для оперативного нахождения свободного подканала из общего количества подканалов.

Адрес свободного подканала формируется из адреса слова второй табли- ды и адреса бита в этом слове. В рассматриваемом случае адрес слова второй таблицы определяется адресом бита указателя слов второй таблицы,расположенного в ячейке МП1 (фиг. 13),

.-

поэтому адрес свободного подканала формируется из адреса бита в указателе слов второй таблицы и адреса бита соответствующего слова второй таблицы.

Формирование адреса подканала для конкретного периферийного устройства выполняется следующим образом.

Общее количество подканалов задается общим количеством бит, установленных в нулевое состояние в словах второй таблицы. Причем наличие свободных подканалов, определяемых словом второй таблицы, характеризуется соответствующим битом указателя слов второй таблицы. Например, если третий бит указателя слов второй таблицы установлен в 1, то свободных подканалов, которые адресуются битом слова второй таблицы по адресу три, нет. Первоначальная установка минимального количества подканалов, которое определяется кодом, набранным на регистре 110 коммутации, осуществляется микропрограммно путем уста новки соответствующего количества би указателя слов второй таблицы и бит слов второй таблицы в единичное состояние.

В начале выполнения команды ввода вывода по адресу периферийного устройства, который задается в команде ввода-вывода и который запоминается в ячейке МП4, в ячейку МП2 выбирается строка первой таблицы. Цель этой выборки определить, назначен подканал для адресованного в команде ввода-вывода периферийного устройства или нет. Определение выполняется путем анализа признака назначения подканала. Если подканал назначен, следовательно, адресованное в команде ввода-вывода периферийное устройство занято, выполнение команды ввода-вывода прекращается. Если подканал не назначен, следовательно, периферийное устройство свободно, выполнение команды ввода-вывода продолжается и вьшолняется попытка назначения свободного подканала. Для этой цели анализируется наличие свободных подканалов. Анализ выполняется путем проверки наличия нулевых бит в указателе слов второй таблицы. Если нулевых бит нет, т.е. свободных подканалов нет, канал прекращает выполнение команды ввода-вывода с признаком результата, характеризующим как-бы от

W

J5

25

20т30

- сутствие адресуемого в команде ввода- вывода периферийного устройства. Если свободные подканалы есть, то формируется адрес свободного подканала. Анализ наличия свободных подканалов и формирование адреса свободного подканала выполняются следующим образом.

Содержимое ячейки МП1, т.е. указатель слов второй таблицы, по информационному входу 21 от процессора выдается в блок 1 4 шифраторов. При этом байт О поступает на вход приоритетного шифратора 87, байт 1 - на вход шифратора 88, байт 2 - на вход шифратора 89, байт 3 - на вход шифратора 90. Каждьп из этих приоритетных шифраторов на своих первых, вторых ц третьих адресных выходах формирует трехразрядный код, который является адресом первого бита (начиная с нулевого) , который находится в нулевом состоянии и который говорит о том, что слово второй таблицы по.этому адресу имеет хоть один свободный подканал. Если в байте О, например, нет ни одного нулевого бита, приоритет- ный шифратор 87 возбуждает четвертый управляющий выход, т.е. в группе слов второй таблицы, адресованных битами байта О указателя слов второй таблицы, ни одного свободного подканала нет. Четвертые выходы приоритетных шифраторов 87-90 поступают на первый- четвертый входы приоритетного шифратора 94. Следовательно, если в указателе слов второй таблицы нет ни одного бита, указывающего на наличие свободного подканала, то возбуждается управляющий выход приоритетного шифратора 94. Если свободные подканалы есть, то двухразрядный адресный код, полученный с первого и второго выходов приоритетного шифратора 94, указывает .адрес первого байта (начиная с нулевого), в котором есть по крайней мере один свободный подканал, а трехразрядный код, полученный на выходах мультиплексоров 91-93, указывает адрес первого бита в слове, который определяет свободный подканал. Информация из блока 14 шифраторов через информационный выход 48 заносит- ся для запоминая в узел 15 регистров, по линии 97 запоминается признак наличия свободных подканалов, по линии 96 - адрес байта, по линии 95 - адрес бита в байте. Таким образом, анализом

35

40

45

50

состояния регистра 9о определяется наличие свободных подканалов. Если свободные подканалы есть, пятиразрядный код, полученный с регистров 100 и 102, определяет адрес слова таблицы 2, в котором есть по крайней мере один свободный подканал. Указанный ана:п1з выполняется микропрограммно путем чтения информации с информационного выхода 49 узла регистров. Про-jg корректируется соответствующий байт

читанный пятиразрядный код адреса слона второй таблицы запоминается в ячейке МПЗ. По этому адресу из второй таблицы читается слово, которое запоминается в ячейке МП5. Затем слово |5 ячейку МП1, Слово второй таблицы из из ячейки МП5 выдается в блок 14 шиф- ячейки МЛ5 записывается во вторую

указателя слов второй таблицы путем сложения этого байта с конста нтой, полученной с дешифратора 107. Скорректированный байт записывается в

раторов аналогично указателю слов второй таблицы и далее запоминается в узле 1-5 регистров. После этого микропрограммно происходит аналогичный анализ информации с регистра 99 и регистров 101 и 103,

Таким образом, после анализа двух слои: указателя слов второй таблицы и одного из слов второй таблицы полу- чается полный адрес свободного подканала. Этот адрес записывается в ячейку MI12, а затем по адресу таблицы 1, Хранящегося в ячейке МП4, переписы- вается вместе с признаком, что под- каИсЛ назначен в первую таблицу 1.

После назначения подканала необходимо скорректировать слово второй и, если необходимо, указатель слов второй таблицы. Для этой цели код адреса бита в байте слова второй таблицы и код адреса бита в байте указателя слов второй таблицы с регистров 103 и 102 по линиями 106 и 105 соответственно через информационный вход 50 узла дешифраторов подаются на Е:ходы дешифраторов 108 и 107 Далее по коду адреса байта, полученного с регистра 101, корректируется соответствующий байт слова второй табли- цы, которое хранится в ячейке МП5, путем сложения этого байта с константой, полученной с выхода дешифратора 108. После этого скорректированное слоЕо второй таблицы проверяется на предмет наличия в нем свободных подканалов. Для этой цели скорректированное слово второй таблицы из ячейки

Организация плавающего количества подканалов, кроме того, позволяет гибко и простым способом адаптироваться к условиям пользователя путем предоставления ему того количества подканалов, которые необходимо только ему для создания определенных кон

Ш5 подается на информационный вход 21 блока шифраторов И на регистре 99 ее фигурации периферийных устройств с запоминается признак наличия свобод- организацией их параллельной работы, ных подканалов. Этот признак анализируется. Если свободные подканалы есть, слово второй таблицы из ячейки МПЗ

используя при этом минимальный объем управляющей памяти, предназначенной для хранения подканалов.

переписывается во вторую таблицу по адресу, KOTOpbttl хранится в ячейке МПЗ. Назначение подканалов заканчивается. Если свободных подканалов нет, необходимо скорректировать соответствующий байт указателя слов второй таблицы, расположенного в ячейке МП1. Для этой дели по коду адреса байта, полученного с выхода регистра 100,

ячейку МП1, Слово второй таблицы из ячейки МЛ5 записывается во вторую

указателя слов второй таблицы путем сложения этого байта с конста нтой, полученной с дешифратора 107. Скорректированный байт записывается в

0

0

5

п

5

0

таблицу. Назначение подканалов заканчивается ,

Освобождение подканалов выполняется после конца связи с периферийным устройством, когда соответствующий подканал не нужен. Освобождение подканала осуществляется микропрограммным способом.

Таким образом, аппаратно-микропро- граммный способ распределения плавающего количества подканалов, который позволяет с минимальными аппаратными затратами производительно осуществлять назначение любого подканала любому периферийному устройству в процессе выполнения команды ввода-вывода, исключает жесткую зависимость количества подключаемых к микропрограммному мультиплексному каналу периферийных устройств от количества отведенных подканалов, вызванное соответствием адреса периферийного устройства адресу соответствующего подканала, что приводит к возможности гибкой адаптации в условиях пользователя в части подключения к каналу широкой номенклатуры периферийных устройств в количественном составе.

Организация плавающего количества подканалов, кроме того, позволяет гибко и простым способом адаптироваться к условиям пользователя путем предоставления ему того количества подканалов, которые необходимо только ему для создания определенных конее фигурации периферийных устройств с организацией их параллельной работы,

фигурации периферийных устройств с организацией их параллельной работы,

используя при этом минимальный объем управляющей памяти, предназначенной для хранения подканалов.

191305693

Формула изобретения

1 . Микропрограммный мультиплексный канал по ,авт.св. Р 1256036, отличающийся тем, что, с целью расширения функциональных возможностей за счет организации плавающего количества подканалов и их произвольного распределения, в него введены

20

мационному входу процессора, при этом группа разрядных выходов блока дешифрации команд соединена с соответствующими разрядами разрешающих входов узла регистров и с разрешающими входами узла дешифраторов и узла фиксации подканалов, информационный выход блока шифраторов соединен с информационным входом узла регистров, выход

входом узла дешифраторов.

2. Канал по п. 1, отличающий с я тем, что узел фиксации подканалов содержит регистр и. группу элеблок шифраторов, узел регистров, узелШ которого соединен с информационным дешифраторов, узел фиксации подканалов, причем информационный вход блока шифраторов является входом канала для подключения к информационному выходу процессора, информационные выходы уз- 5 ментов И, причем выходы регистра сое- ла регистров, узла дешифраторов и уз- динены с первыми входами элементов И ла фиксации подканаловподключены к группы, вторые входы и выходы которых выходу микропрограммного мультиплекс- образуют соответственно разрешающий. ного канала для подключения к инфор- вход и информационный выход узла.

3

20

мационному входу процессора, при этом группа разрядных выходов блока дешифрации команд соединена с соответствующими разрядами разрешающих входов узла регистров и с разрешающими входами узла дешифраторов и узла фиксации подканалов, информационный выход блока шифраторов соединен с информационным входом узла регистров, выход

входом узла дешифраторов.

2. Канал по п. 1, отличающий с я тем, что узел фиксации подканалов содержит регистр и. группу элекоторого соединен с информационным ментов И, причем выходы регистра сое- динены с первыми входами элементов И группы, вторые входы и выходы которых образуют соответственно разрешающий. вход и информационный выход узла.

Фиа.

27

71

Rj

J/

Фиг.

75

,0

7

J

73

72

J3

Ш1

- J2

«.5

SO

Ю7

JOS 106

т

51

Фиг.9

foxoff о нанальнцю MUHponpoepafing J

Установить Р5Б-Я

есть,

Ла

приеп адреса абонента

Форпирование адй&са УСУ

Записать нулв&ию но- нанду ffрегистр вь/даги62.

л L.

Золисата УПР-Н и PQ6-H ff pesucmpt) 65, бЦ

1(12}

1

Считать из У/1 УСУ и. записать в МП

Аппаратурно ана/iu- JupyefTjcft CHflmue А4Р-А и аппаратур на снимаетсй УПР-н

2(12)

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1640702A1 |

| Устройство для формирования сигнала подключения периферийного устройства к каналу ввода-вывода | 1985 |

|

SU1247881A1 |

Изобретение касается вычислительной техники, в частности организации микропрограммных мультиплексных каналов микропрограммных вычислительных машин, и может быть использовано для организации обмена информацией между периферийными устройствами и процессором. Целью изобретения является расширение функциональных возможностей микропрограммного мультиплексного канала за счет организации плавающего количества подканалов и их произвольного распределения. Микропрограммный мультиплексный канал содержит блок 2 регистров,блок 6 формирования управляющих сигналов, блок 1 дешифрации .команд, блок 5 коммутации, блок ,7 анализа, узел 9 свертки по модулю два, блок 14 шифраторов 12, узел 15 регистров, узел 16 дешифраторов, узел 17 фиксации подканалов, два регистра 3 и 4, четыре группы элементов И 10-13, элемент НЕ. 1 з.п. ф-лы, 13 ил., 1 табл. гг. to а С ОС с ел о: ее ос Ч 23 I4J

С

Ьыкод Фи. 11

fa

айт с менвнто i/tf/

ifcmoHoffum о petucmfi 95 иНФ Л

Moffu9 uifu/ o ffamt eve/nvuH и cffpoc

Записать 9аннмх ЛОП

байт о I байт 1

У Низ а т ел tf слов таблицы Z

Страна таблицш 1

Адрвс таб/гицы Z

Affpec тоб/гицы 1

Слово тоб/1ицш Z

Фиг. /J

Редактор И. Шулла

Составитель С. Пестмал

Техред А.Кравчук Корректоре. Черни

Заказ 1453/47 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

I Лппоратнып о8ро- 1 iOH анализируется ) снятие ,рл I и аппаратурно емипа- I етсл

байт 2 байт J

пп

ппг

пп 5

/V/74

ПП5

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-11-18—Подача