113

Изобретение относится к вычислительной Л бхнике и может быть использовано в устройствах для определения угловых координат объекта.

Целью изобретения является повышение быстродействия.

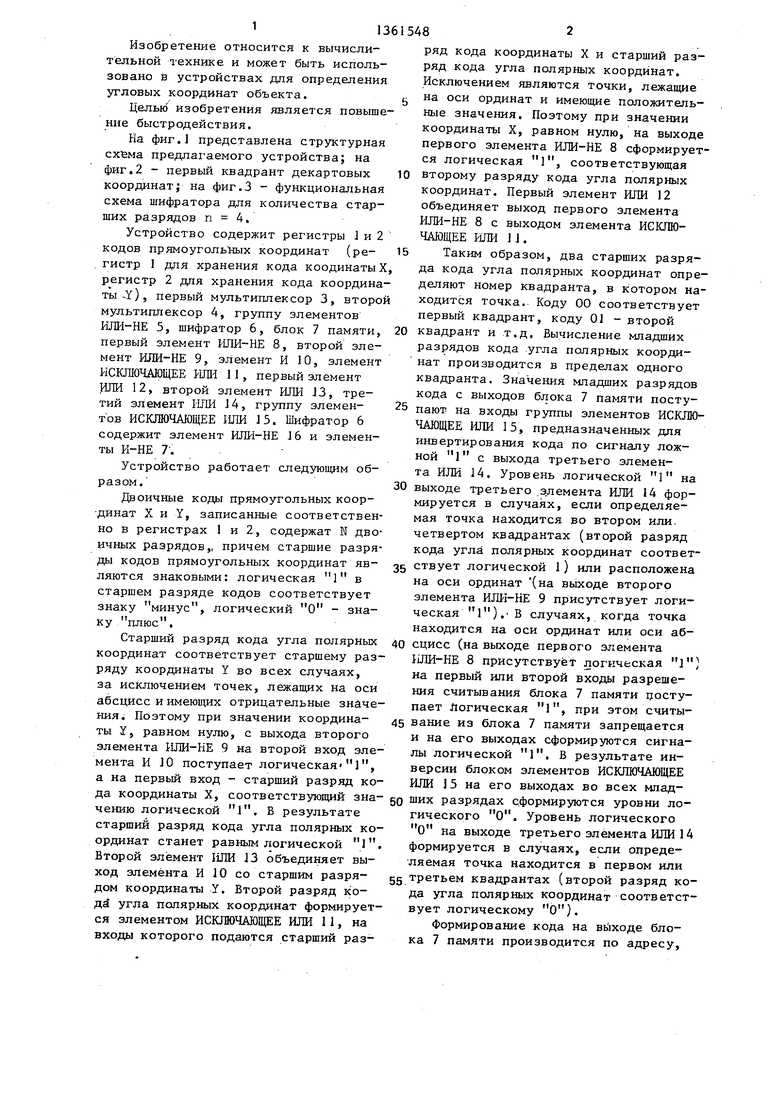

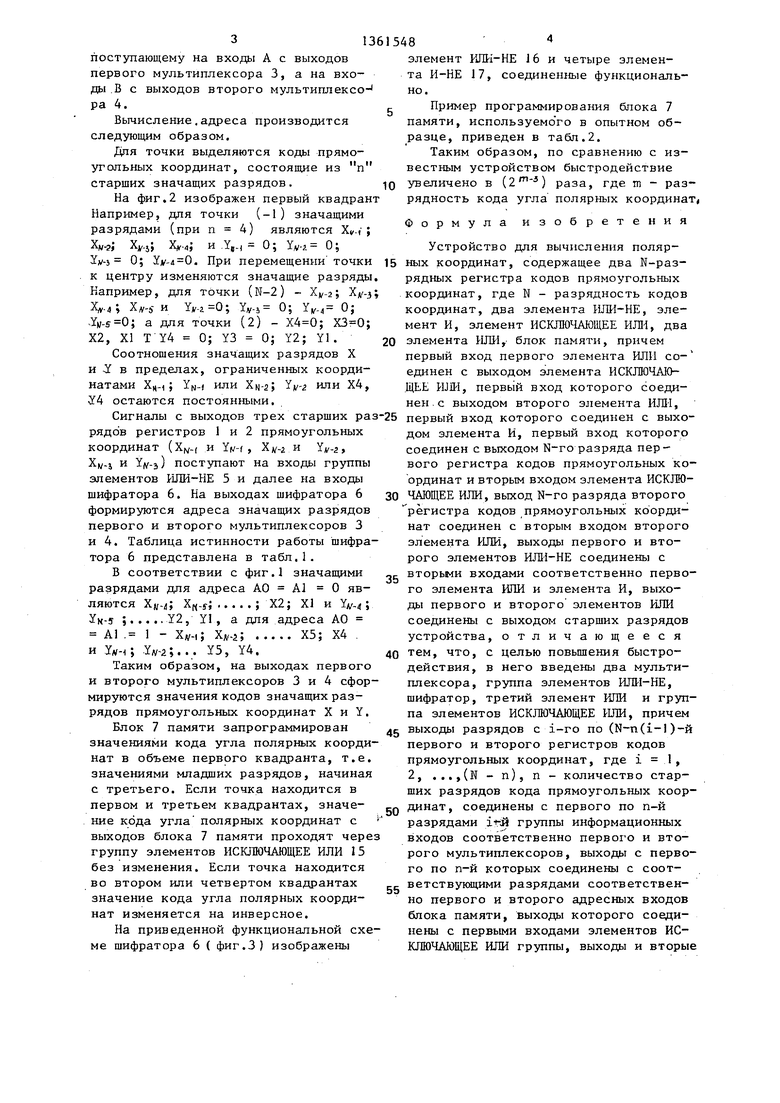

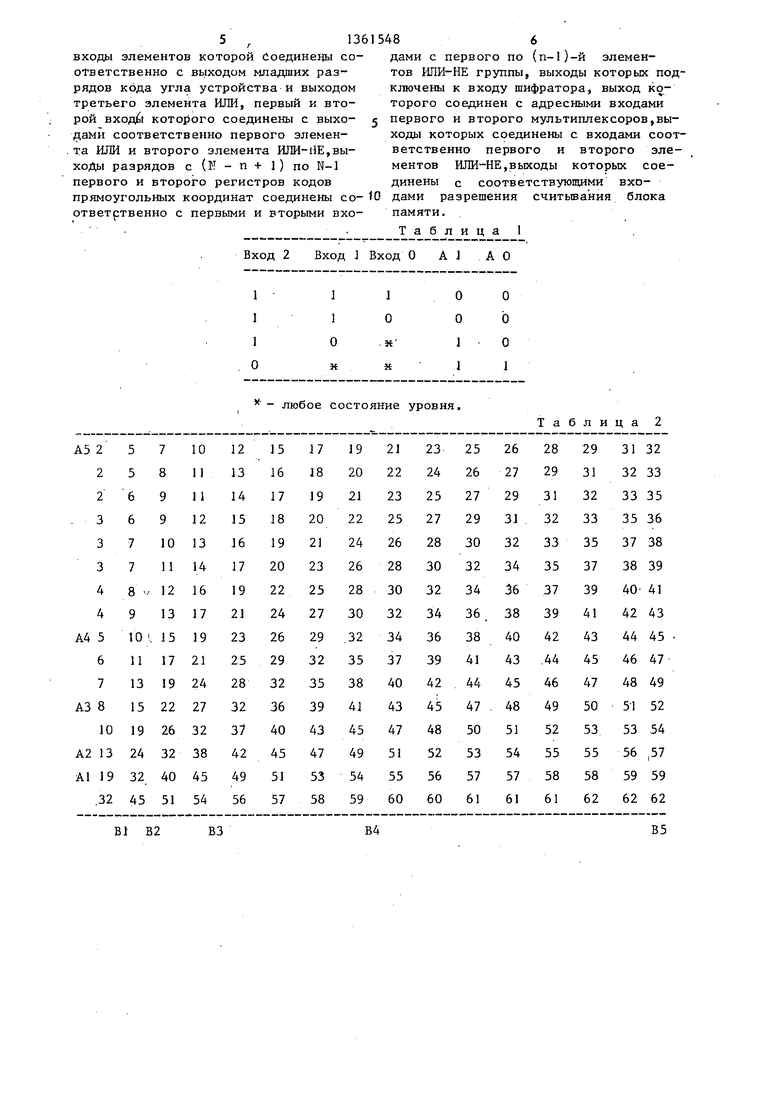

На фиг. представлена структурная схема предлагаемого устройства; на фиг.2 - первый квадрант декартовых координат; на фиг.З - функциональная схема шифратора для количества старших разрядов п 4.

Устройство содержит регистры J и 2 кодов прямоугольных координат (регистр 1 для хранения кода коодинатыХ регистр 2 для хранения кода координаты У), первый мультиплексор 3, второй мультиплексор 4, группу элементов

ИЛИ-НЕ 5, шифратор 6, блок 7 памяти, 20 квадрант и т.д. Вычисление младших

первый элемент ИЛИ-НЕ 8, второй элемент ИЛИ-ПЕ 9, элемент И 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11 , первый элемент ИЛИ 12, второй элемент РШИ J3, третий элемент ИЛИ 14, группу элементов ИСКЛЮЧАЮЩЕЕ ИДИ J5. Шифратор 6 содержит элемент ИЛИ-НЕ 16 и элементы И-НЕ 7:

Устройство работает следующим образом.

Двоичные коды прямоугольных коор- дйнат X и Y, записанные соответственно в регистрах 1 и 2, содержат N двоичных разрядов,, причем старшие разряды кодов прямоугольных координат являются знаковыми: логическая 1 в

старшем разряде кодов соответствует знаку

минус, логический О - знаку плюс

находится на оси ординат или оси аб- Старший разряд кода угла полярных 40 сцисс (на выходе первого элемента координат соответствует старшему раз- ИЛИ-НЕ 8 присутствует логическая

на первый или второй входы разрешения считывания блока 7 памяти цостуряду координаты Y во всех случаях, за исключением точек, лежащих на оси абсцисс и имеющих отрицательные значения. Поэтому при значении координаты Y, равном нулю, с выхода второго элемента ИЛИ-НЕ 9 на второй вход элемента И JO поступает логическая- 1, а на первый вход - старший разряд копает Логическая 1 , при этом считы- 45 вание из блока 7 памяти запрещается и на его выходах сформируются сигналы логической 1. В результате инверсии блоком элементов ИСКЛЮЧАЮЩЕЕ ИЛИ J 5 на его выходах во всех младда координаты X, соответствующий зна- 50 ших разрядах с.формируются уровни ло- чению логической J. В результате старший разряд кода угла полярных координат станет равным логической 1.

гического О . Уровень логического о на выходе третьего элемента ИЛИ 14 формируется в случаях, если опредеБторой элемент 1ШИ 13 объединяет вы- ляемая точка находится в первом или ход элемента И 10 со старшим разря- gg третьем квадрантах (второй разряд кодом координаты У. Второй разряд ко- да угла полярных координат соответствует логическому О).

Формирование кода на вйходе блока 7 памяти производится по адресу.

дй угла поляр.ных координат формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 11, на входы которого подаются старший раз

ряд кода координаты X и старший разряд кода угла полярных координат. Исключением являются точки, лежащие на оси ординат и имеющие положительные значения. Поэтому при значении координаты X, равном нулю, на выходе первого элемента ИЛИ-НЕ 8 сформируется логическая 1, соответствующая второму разряду кода угла полярных координат. Первый элемент ИЛИ 12 объединяет выход первого элемента ИЛИ-НЕ 8 с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и.

Таким образом, два старших разряда кода угла полярных координат определяют номер квадранта, в котором находится точка. Коду 00 соответствует первый квадрант, коду 01 - второй

разрядов кода угла полярных координат производится в пределах одного квадранта. Значения мпадших разрядов кода с выходов блока 7 памяти посту25 пают на входы группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15, предназначенных для инвертирования кода по сигналу ложной 1 с выхода третьего элемента ИЛИ 14. Уровень логической 1 на

30 выходе третьего .элемента ИЛИ 14 формируется в случаях, если определяемая точка находится во втором или. четвертом квадрантах (второй разряд кода угла полярных координат соответ35 ствует логической 1) или расположена на оси ординат (на выходе второго элемента ИЛК-НЕ 9 присутствует логическая 1) . В случаях, когда точка

пает Логическая 1 , при этом считы- 45 вание из блока 7 памяти запрещается и на его выходах сформируются сигналы логической 1. В результате инверсии блоком элементов ИСКЛЮЧАЮЩЕЕ ИЛИ J 5 на его выходах во всех младших разрядах с.формируются уровни ло-

гического О . Уровень логического о на выходе третьего элемента ИЛИ 14 формируется в случаях, если опредепоступающему на входы А с выходов первого мультиплексора 3, а на входы .В с выходов второго мультиплексо- ра 4.

Вычисление,адреса производится следующим образом.

Для точки выделяются коды прямоугольных координат, состоящие из п старщих значащих разрядов.

На фиг.2 изображен первый квадрант Например, для точки (-1) значащими разрядами (при п 4) являются Х,., ; Xjjf.j} и ,,.( 0; Yv-i- 0; YV-J 0; . При перемещении точки к центру изменяются значащие разряды. Например, для точки (N-2) - Хц,-2; Х.; и Yv. Yv-i 0; Y,. 0; -Yv-s 0; a для точки (2) - X2, XI Т Y4 0; Y3 0; Y2; Yl .

Соотношения значащих разрядов X и в пределах, ограниченных координатами Хц-1; YN-J или XN-S; или Х4, Y4 остаются постоянными.

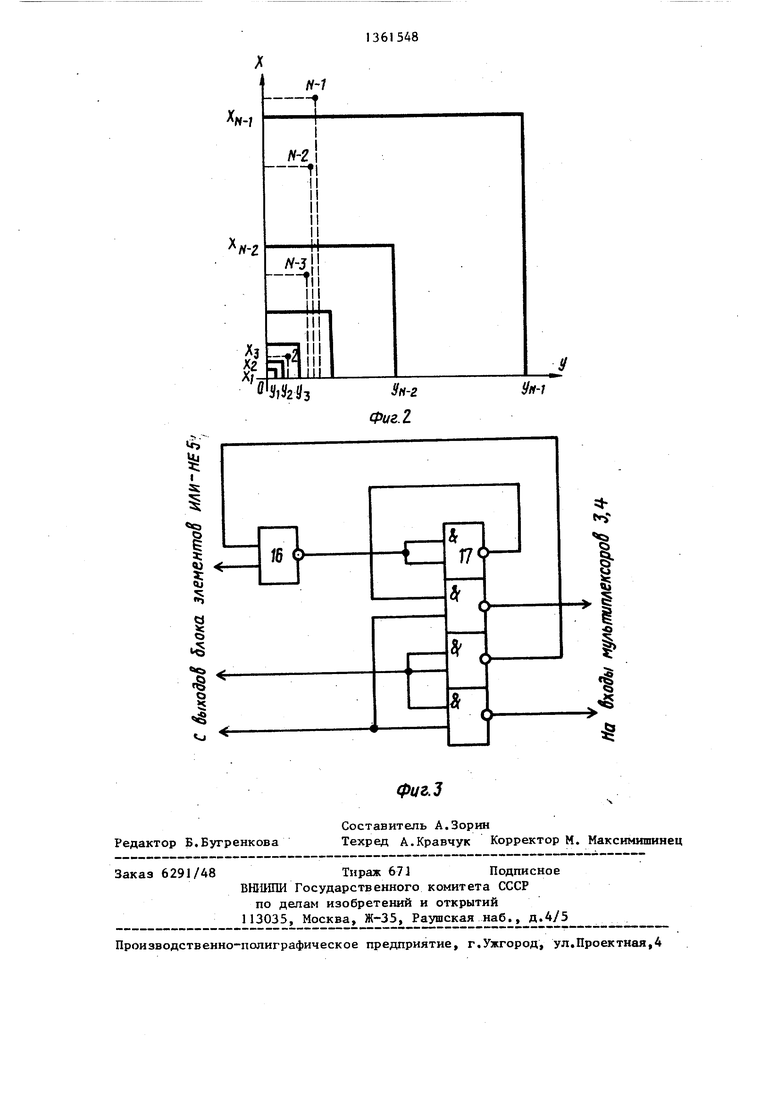

Сигналы с выходов трех старших раз-25 первый вход которого соединен с выхорядов регистров 1 и 2 прямоугольных координат (Х., и Yn-t , и Y,-2, Xy.j и Yy-j) поступают на входы группы элементов ИЛИ-НЕ 5 и далее на входы шифратора 6. На выходах шифратора 6 формируются адреса значащих разрядов первого и второго мультиплексоров 3 и 4. Таблица истинности работы шифратора 6 представлена в табл.1.

В соответствии с фиг.1 значащими разрядами для адреса АО А1 0 являются Ху-л; Xf.j-;; Х2; XI и

YH-S 5Y2, Yl , а для адреса АО

А1 . 1 - Xv-i; X;v-a; Х5; Х4 .

и YWM; Y/v-a;... Y5, Y4.

Таким образом, на выходах первого и второго мультиплексоров 3 и 4 сформируются значения кодов значащих разрядов прямоугольных координат X и Y.

Блок 7 памяти запрограммирован значениями кода угла полярных координат в объеме первого квадранта, т.е. значениями младших разрядов, начиная с третьего. Если точка находится в первом и третьем квадрантах, значение кода угла полярных координат с выходов блока 7 памяти проходят через группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 без изменения. Если точка находится во втором или четвертом квадрантах значение кода угла полярных координат изменяется на инверсное.

На приведенной функциональной схеме шифратора 6 ( фиг.З) изображены

35

40

дом элемента И, первый вход которого соединен с выходом N-ro разряда первого регистра кодов прямоугольных координат и вторым входом элемента ИСКЛЮ30 ЧАЮЩЕЕ ИЛИ, выход N-ro разряда второго регистра кодов прямоугольных координат соединен с вторым входом второго элемента РШИ, выходы первого и второго элементов ИЛИ-НЕ соединены с вторыми входами соответственно первого элемента ИЛИ и элемента И, выходы первого и второго элементов ИЛИ соединены с выходом старших разрядов устройства, отличающееся тем, что, с целью повьш1ения быстродействия, в него введены два мультиплексора, группа элементов ИЛИ-НЕ, шифратор, третий элемент ИЛИ и группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы разрядов с i-ro по (N-n(i-l)-й первого и второго регистров кодов прямоугольных координат, где i 1, 2, ...,(N - п), п - количество старших разрядов кода прямоугольных координат , соединены с первого по п-й разрядами it-й группы информационных входов соответственно первого и второго мультиплексоров, выходы с первого по п-й которых соединены с соотсс ветствующими разрядами соответственно первого и второго адресных входов блока памяти, выходы которого соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы и вторые

45

50

8

элемент КЛИ-НЕ J6 и четыре элемента И-НЕ 17, соединенные функционально.

Пример программирования блока 7 памяти, используемо го в опытном образце, приведен в табл.2.

Таким образом, по сравнению с известным устройством быстродействие увеличено в () раза, где m - разрядность кода угла полярных координат

Формула изобретения

Устройство для вычисления поляр- ных координат, содержащее два N-раз- рядных регистра кодов прямоугольных координат, где N - разрядность кодов координат, два элемента НЛИ-НЕ, элемент И, элемент ИСКЛЮ -ШОЩЕЕ ИЛИ, два элемента ИЛИ, блок памяти, причем

первый вход первого элемента ИЛИ со- единен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом второго элемента ИЛИ,

5

0

дом элемента И, первый вход которого соединен с выходом N-ro разряда первого регистра кодов прямоугольных координат и вторым входом элемента ИСКЛЮ0 ЧАЮЩЕЕ ИЛИ, выход N-ro разряда второго регистра кодов прямоугольных координат соединен с вторым входом второго элемента РШИ, выходы первого и второго элементов ИЛИ-НЕ соединены с вторыми входами соответственно первого элемента ИЛИ и элемента И, выходы первого и второго элементов ИЛИ соединены с выходом старших разрядов устройства, отличающееся тем, что, с целью повьш1ения быстродействия, в него введены два мультиплексора, группа элементов ИЛИ-НЕ, шифратор, третий элемент ИЛИ и группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы разрядов с i-ro по (N-n(i-l)-й первого и второго регистров кодов прямоугольных координат, где i 1, 2, ...,(N - п), п - количество старших разрядов кода прямоугольных координат , соединены с первого по п-й разрядами it-й группы информационных входов соответственно первого и второго мультиплексоров, выходы с первого по п-й которых соединены с соотс ветствующими разрядами соответственно первого и второго адресных входов блока памяти, выходы которого соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы и вторые

5

0

5 13615486

входы элементов которой Соедине1{ы со- дами с первого по (п-1)-й элемен- о Гветственно с выходом младших раз- тов ИПИ-НЕ группы, выходы которых подрядов кода угла устройства и выходом ключены к входу шифратора, выход kg- третьего элемента ИЛИ, первый и вто- торого соединен с адресными входами рой вход которого соединены с выхо- j первого и второго мультиплексоров,выходы которых соединены с входами соответственно первого и второго элементов ИЛИ-НЕ,выходы которых соединены с соответствующими входами соответственно первого элемента ИЛИ и второго элемента ИЛИ-iJE,выходы разрядов с (N - п 4- 1 ) по N-1 первого и второго регистров кодов

прямоугольных координат соединены со-tO дами раэрешения считьшания блока ответртвенно с первыми и вторыми вхо- памяти.

.Таблица

В1 В2

ВЗ

В4

В5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полярных координат | 1987 |

|

SU1449985A2 |

| Устройство для вычисления полярных координат | 1984 |

|

SU1183961A1 |

| Устройство для определения аргумента вектора | 1986 |

|

SU1319024A1 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Цифровой феррозондовый измеритель азимута | 1987 |

|

SU1498913A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Устройство для программного управления электроприводом | 1985 |

|

SU1260919A1 |

| Устройство для регистрации аналогового процесса | 1986 |

|

SU1429171A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах для определения угловых координат объекта. Целью изобретения является повышение быстродействия. Устройство для вычисления полярных координат содержит регистры 1,2 кодов прямоугольных координат (регистр 1 для хранения кода координат X, регистр 2 для хранения кода координат Y), первый мультиплексор 3, второй мультиплексор 4, группу элементов ШТП-НЕ 5, шифратор 6, блок памяти 7, первый элемент ИЛИ-НЕ 8- второй элемент 1-ШИ-НЕ 9, элемент И.10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11,первый элемент ИЛИ 12, второй элемент ИЛИ 13, третий элемент ИЛИ 14, группу элементов ИСКЛЮЧАЮЩЕЕ 1ШИ 15. Цель достигается за счет изменения схемы формирования младших разрядов кода угла полярных координат. Пошаговый выбор значений угла из блока памяти заменен на однократный выбор значений младших разрядов из блока памяти. 3 ил., 2 табл. i (Л СА:) 05 СП « 00

| Патент США № 3952187, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство для вычисления полярных координат | 1984 |

|

SU1183961A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-04—Подача