Изобретение относится к вычислительной технике и может быть использовано в качестве функционального расширителя в вычислительных комплексах с высоким быстродействием.

Цель изобретения - расширение области применения устройства за счет обработки аргументов в форме с плавающей точкой.

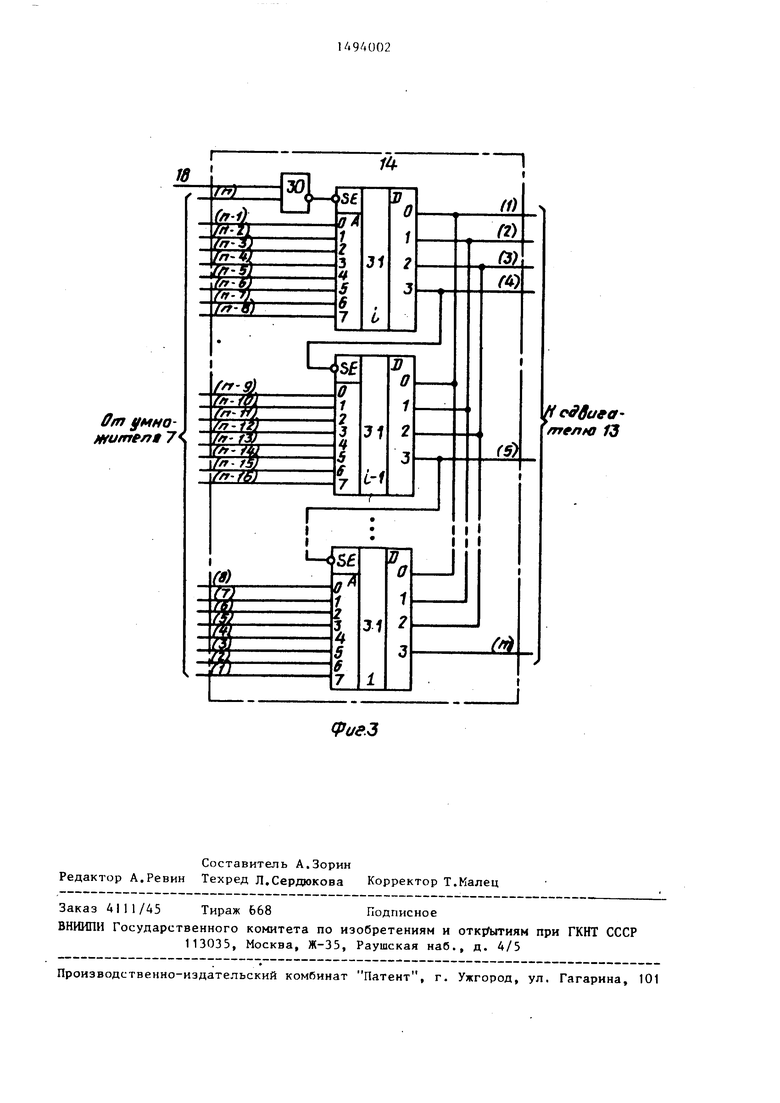

На фиг.1 изображена блок-схема предложенного устройства; на фиг.2 - пример выполнения блока управления; на фиг.З - пример выполнения блока вы- выделения старшей единицы.

Устройство содержит первый регистр 1, первый 2 и нторой 3 блоки памяти, схему 4 сравнения, второй регистр 5,

первый сумматор 6, умножитель-сумматор 7 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8. Совокупность перечисленных блоков представляет собой вычислительный блок 9. Кроме того, устройство содержит первый сдвигатель 10, второй сумматор II, группу элементов И 12, второй сдвигатель 13, блок 14 выделения старшей единицы, третий сумматор 15 и блок 16 выделения квадранта. Вход 17 блока 16 выделения квадранта предназначен для вводл признака вычисляемой функции, а вход 18 - для ввода признака формы аргумента. Выход 19 устройства янляе1ся знаковым, а выход 20 блока 16 выделения квадранта является Buxd/ioj-i признака номера квадранта.

4

СО 4

ЬО

ГО

Блок 16 пыделения квадранта содержит первый 21, второй 22 н третий 23 элементы 2И-ИЛИ, элемент И-НЕ 24, элемент 25 неравнозначности, первый 26, второй 27, третий 28 и четвертый 29 инверторы.

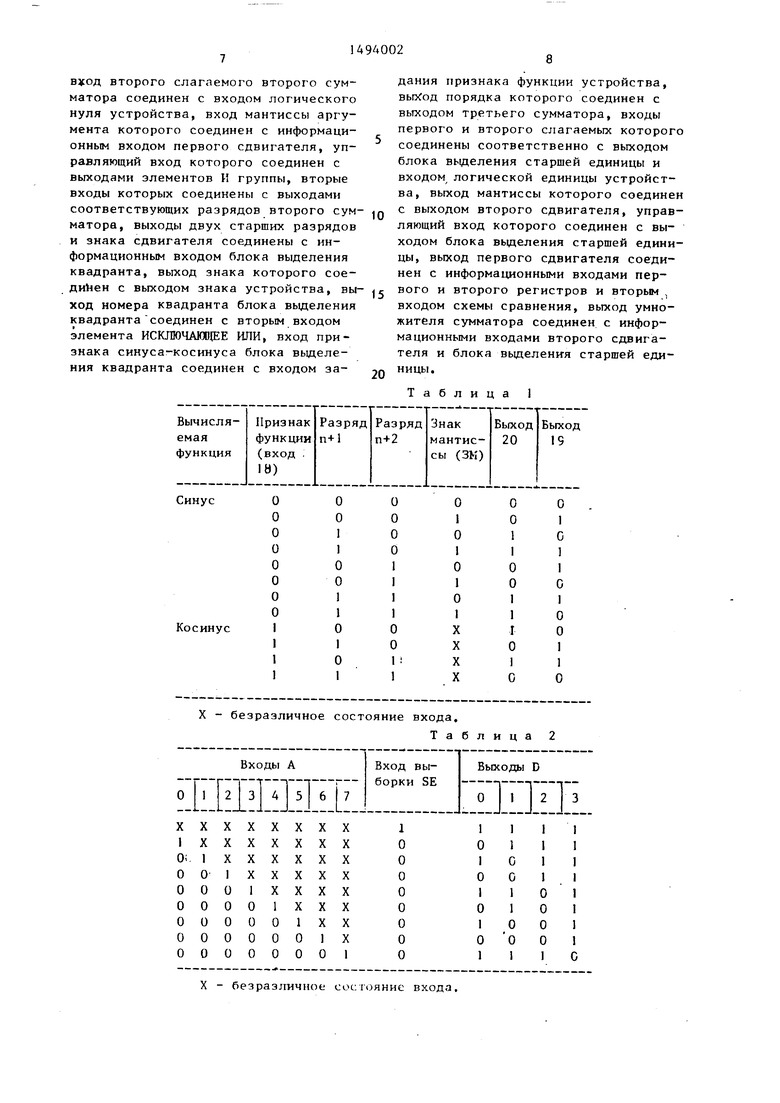

Комбинированные зависимости, pea-- лиауемые блоком 16 выделения квадранта, приведены в табл,1.

Блок 1А выделения старшей единицы содержит элемент И-НЕ 30 и элементы программируемых запоминающих устройств (ПЗУ) 31, число которых определяется числом разрядов мантиссы значения функции. Каждому выходу элементов ПЗУ соответствует разряд кода старшей единицы, номер которого указан в скобках. Блок 1А выдает код положения стар11 ей единицы в инверсном коде. При логическом нуле на входе 1 блок 14 выдает инверсный код нуля. Прог раммирование каждого элемента ПЗУ производится в соответствии с табл. 2.

Входы второго сумматора 11 соединены так, что на входы разрядов первого слагаемого подаются значащие разряды порядка, а входы второго слагаемого заземлены. Знаковый разряд порядка заведен на вход переноса сумматора 11, что обеспечивает при отри1;ательном порядке аргумента выдачу порядка в инверсном коде в соответствии с требованиями управления первым сдвигателем.

Третий сумматор 15 обеспечивает вычитание единицы из инверсного кода

о( - координата оси абсцисс точки пересечения производных двух соседних фиксированных значений. Функция косинуса вычисляется в вы

выдаваемого блоком 14 выделения старшей единицы, чем обеспечивается полу- Ю числительном блоке 9 как функция си- чение на его выходе порядка значения нуса от инверсного кода аргумента на функции. Это достигается путем соединения разрядов инверсного кода, выинтервале

cos(X)sin(l-X) ;:.sin(X)

даваемых блоком 14 выделения старшей един1п;ы, с соответствуюш 1ми входами первого слагаемого третьего сумматора, на входы второго слагаемого ко- торог О подаются сигналы логической единицы.

cos(X)sin(l-X) ;:.sin(X)

45 Поступающая на вход первого регистра 1 с выхода первого сдвигателя 10 старшая часть разрядов аргумента запоминается в нем, а младшая часть разрядов аргумента запоминается во Устройство работает следующим об- 50 втором регистре 5 и одновременно по- разом.дается на второй вход схемы 4 сравнеПри обработке аргумента с плаваю- ния. С выхода первого регистра 1 код щей T04Koii, мантисса которого подает- старшей части разрядов подается на, ся на вход nt pBoto сдвигателя 10, а вход первого сумматора 6 и на адрес- порядок - на вход второго сумматора 5 вход второго блока 3 памяти, где

I1, признак формы аргумента (вход 18 блока 1 б) устанавлинается в состояние логическоГг единицы. При от- риц.тг ельнпп поря;:1ке на вь.гходе сумхранятся значения о(. Выбранньй из второго блока 3 памяти код о подается на второй вход схемы 4 сравнения, 1 д« сравнивается с кодом младших раз

матора 11 образуется обратный код порядка, который поступает на вход первого сдвигателя 10, а при положитель- ном порядке код порядка не изменяет- ся, В сдвигателе 10 производится сдвиг мантиссы так, что порядок обнуляется, т.е. аргумент переводится в форму с фиксированной точкой. Разрядность сдвигателя на два разряда больше разрядности мантиссы, что позволяет при значении аргумента больше первой четверти периода вычисляемых функций определить положение аргумента в пределах периода и определить соответствующие эквивалентные преоб- разовагия приведенного аргумента для первой четверти периода, в пределах которой обрабатывает аргументы вычислительной блок. При обработке чисел с плавающей точкой ключевые элементы группы элементов И 12 открыты. Вычислительный блок 9 выполняет вычисление функций в интервале от О до 1 в соответствии с выражением

f iT

sin X -i--X cosXe, Ри M

sin (Xp-t-2 )(Xc-2 ), при ( ,

где X j. - старшая часть разрядов аргумента;

Х - младшая часть разрядов аргумента ;

о( - координата оси абсцисс точки пересечения производных двух соседних фиксированных значений. Функция косинуса вычисляется в вычислительном блоке 9 как функция си- нуса от инверсного кода аргумента на

числительном блоке 9 как фу нуса от инверсного кода арг

интервале

cos(X)sin(l-X) ;:.sin(X)

ния. С выхода первого регистра 1 код старшей части разрядов подается на, вход первого сумматора 6 и на адрес- вход второго блока 3 памяти, где

хранятся значения о(. Выбранньй из второго блока 3 памяти код о подается на второй вход схемы 4 сравнения, 1 д« сравнивается с кодом младших разрядов. Схема А сравнения вьщает сигнал единицы, если код младшей части разрядов больше значения d, и подает его на суммирующий вход первого сумматора 6, где производится прибавление единицы к коду старшей части разрядов, и через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8 - на вход инвертирования данных второго регистра 5. Преобразованный код старшей части разрядов с выхода сумматора 6 подается на адресный вход первого блока 2 памяти, в

котором хранятся значения sin

tr

iV

и -„- cosXj. Значение - cosX с первого выхода блока 2 памяти подается на первьй вход сомножителя умножителя-сумматора 7, на второй нход сомножителя которого подается код младшей части разрядов аргумента с выхода второго регистра 5, а на вход

ffv слагаемого подается значение sin

В результате на выходе умножителя- сумматора 7 формируется значение функции в соответствии с соотношениями, приведенными выше, Сиг нал, вырабатываемой схемой А сравнения, обеспечивает формирование необходимых значений для реализации указанны соотношений. При вычислении косинуса по выходу 20 блока 16 вырабатываеся сигнал логической единицы, которы обеспечивает необходимую инверсию частей кода аргумента .при их выдаче из первого 1 и второго 5 регистров, Свыхода умножителя-сумматора 7 вычислительного блока 9 результат вычисления функции в форме с фиксированной точкой подается на входы второго сдвигателя 13 и блока 14 выделения старшей единицы. Блок 1А определяет номер старшей единицы результата и выдает его инверсный код. По этому коду во втором сдвигателе производится нормализация вычисленного значения функции, а на выходе третьего сумматора единицы формируется ко порядка вычисленного значения функции. Таким образом, совокупность нор мализованного во втором сдвигателе 13 значения функь.ии, определенного в третьем сумматоре едини порядка функции, и знака функции (выход 19 устройства), вырабатываемого в блоке 16, образует выходное значение функции в форме с плавающей точкой.

0

При обработке чисел с фиксированной точкой признак формы аргумента равен нулю. Группа элементов И 12 выдает код нуля на управляющий вход первого сдвигателя 10, в котором не производится сдвига, подаваемого на его информационный вход аргумента функции с фиксированной точкой. Этот аргумент без изменений подается на соответствующие входы вычислительного блока 9, Нулевой признак формы аргумента запрещает работу блока 14 выделения старшей единицы, который

5 при этом выдает инверсный код нуля, В результате во втором сдвигателе 13 не производится нормализация вычисленного значения функции, а в третьем сумматоре 15 не производится форQ мирование порядка. Таким образом, на входе второго сумматора 1I и парно- - го сдвигателя 10 аргумент с плавающей точкой преобразуется в значение функции с плавающей точкой при еди5 ничном значении признака формы аргумента (вход 18, блока 16), а при нулевом значении признака формы аргумента аргумент с фиксированной точкой на входе устройства преобразуется в значение функции с фиксированной точкой на выходе устройства.

Из выр)еизложенного следует, что предлагаемое устройство (по сравнений с прототипом) имеет расширенную область применения (за счет обработки аргументов с плавающей точкой во всем диапазоне представления чисел),

Формула изобретения

0

Устройство для вычисления функций синуса и косинуса по авт,св. 1 1322272, отличающееся тем что, с целью расширения области примене- g ния за счет обработки аргументов с плавающей запятой, в него введены первый и второй сдвигатели, блок-выделения квадранта, группа элементов И, второй и третий сумматоры и блок, выделения старшей единицы, причем вход признака формы аргумента устройства соединен с первыми входами элементов И группы и входом разрешения работы блока поиска старшей единицы вход порядка аргумента устройства соединен с входом первого слагаемого второго сумматора, вход переноса которого соединен с входом знакового разряда порядка ар1 умента устройства

0

5

0

5

вход второго слагаемого второго сумматора соединен с входом логического нуля устройства, вход мантиссы аргумента которого соединен с информационным входом первого сдвигателя, управляющий вход которого соединен с выходами элементов И группы, вторые входы которых соединены с выходами соответствующих разрядов второго сум матора, выходы двух старших разрядов и знака сдвигателя соединены с информационным входом блока выделения квадранта, выход знака которого сое- с выходом знака устройства, вы ход номера квадранта блока выделения квадранта соединен с вторым входом элемента ИСКЛЮЧАЮВ1ЕЕ ИЛИ, вход признака синуса-косинуса блока выделения квадранта соединен с входом за-

Дания признака функции устройства, выход порядка которого соединен с выходом третьего сумматора, входы первого и второго слагаемых которого соединены соответственно с выходом блока выделения старщей единицы и входом логической единицы устройства, выход мантиссы которого соединен с выходом второго сдвигателя, управляющий вход которого соединен с выходом блока выделения старшей единицы, выход первого сдвигателя соединен с информационными входами первого и второго регистров и вторым , входом схемы сравнения, выход умножителя сумматора соединен с информационными входами второго сдвигателя и блока выделения старшей единицы.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Устройство для вычисления косинуса числа | 1988 |

|

SU1522197A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Устройство для вычисления синуса | 1986 |

|

SU1319025A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

Изобретение относится к вычислительной технике, может быть использовано в качестве функционального расширителя в вычислительных комплексах с высоким быстродействием и является усовершенствованием изобретения по авт.св. N 1322272. Цель изобретения - расширение области использования устройства за счет обработки аргументов с плавающей запятой. Устройство для вычисления функций синуса и косинуса содержит первый, второй и третий сумматоры, первый и второй регистры, первый и второй сдвигатели, первый и второй блоки памяти, схему сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, умножитель-сумматор, блок выделения квадранта, блок выделения старшей единицы и группу элементов И. Введение в устройство для вычисления функций синуса и косинуса второго и третьего сумматоров, первого и второго сдвигателей, блока выделения старшей единицы, блока выделения квадранта и группы элементов с соответствующими связями обеспечивает достижение поставленной цели. 3 ил., 2 табл.

X - безразличное состояние входа,

Таблица 2

X - безразличное сосгояние входа.

Фиг1

От умно Mfumfnt 7

(рие.З

телю 13

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1322272A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-15—Публикация

1987-11-16—Подача