1

1

Изобретение относится к микроэлектронике и предназначено для ис.пользования в цифровых устройствах,

в частности в запоминагощих устройст- вах ЭВМ.

Цель изобретения - повышение степени интеграции элемента памяти.

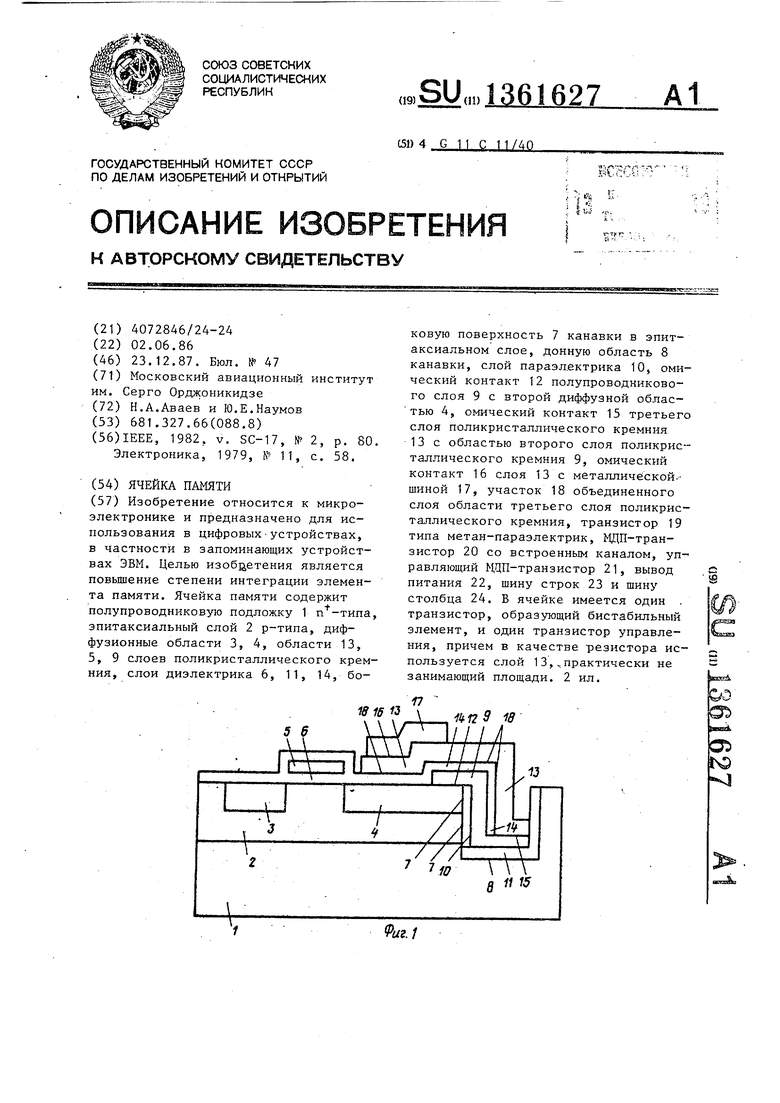

На фиг. 1 показана структура запоминающего- элемента, поперечный разрез, на фиг. 2 - эквивалентная схема запоминающего элемента.

Ячейка содержит полупроводнико- подложку 1 п -типа, эпитаксиаль- ный слой 2 р-типа, первую диффузион-

ную область 3 п -типа, вторую диффузионную область А,.область 5 первого слоя поликристаллического кремния, первый слой 6 диэлектрика, боковую поверхность 7 канавки в эпитаксиаль ном слое, донная область 8 канавки, область второго слоя 9 поликристаллического кремния,, слой 10 параэлект рика, второй слой 11 диэлектрика, омический контакт 12 полупроводнико- вого слоя 9 с второй диффузионной область 4, область третьего слоя 13 поликристаллического кремния, третий слой 14 диэлектрика, омический кон,такт 15 третьего слоя 13 поликристал лического кремния с областью второго слоя 9 поликристаллического кремния, омический контакт 16 третьего слоя 13 поликристаллического kpeмния с металлической шиной 17, участок 18 объединенного слоя области третьего слоя поликристаллического кремния, транзистор 19 типа метан-параэлект- рик - полупроводник (МПП-). ЬЩП-тран- зистор 20 со встроенным каналом, управляющий ЩП-транзистор 21, вывод 22 питания, шину 23 строки и шину 24 столбца.

Ячейка памяти работает следующим образом.,

Подложка 1 .заземляется, а шина 17

соединяется с плюсом источника питания. Электрод затвора 5 соединяется с шиной выборки строки (при создании матричного накопителя он яв-

.ляется частью шины X), а область 3 истока управляющего МДП-транзисто- ра - с шиной столбца (область 3 может являться одновременно шиной столбца). Подложка 1 и область 4 типа образуют исток и сток транзисто ра, затвором которого является полупроводниковый слой 9, канал образуется в слое 2 р-типа у боковой поверх

)

7 углубления и отделен от затвора слоем 10 параэлектрика (транзистор типа металл-параэлектрик - полупроводник). Одновременно в структуре сформирован МДП-транзистор со встроенным каналом п-типа, истоком которого является полупроводниковый слой 9 в месте его контакта 15 со слоем 13, стоком - шина 1.7, затво- ром - слой 9, а канал образуется в слое 13.

В режиме хранения напряжение на шине 23 строки равно нулю, МДП-транзистор 21 закрыт и бистабильный элемент отключен от шины 24 столбца. При записи на шине столбца устанавливается напряжение логического нуля или логической единицы. После этого на шину строки 23 подается им- пульс, отпирающий МДП-транзистор 21. ;При считывании на шине 24 столбца предварительно устанавливают напряжение логической единицы, которое далее поддерживается емкостью шины. После этого подается импульс на шину 23 строки, отпирающий МДП-транзистор 21, в результате чего напряжение, на шине 24 понижается при считывании логического нуля или остается неизменным при считывании логической единицы, что воспринимается усилителем считывания..

)

В предлагаемой ячейке памяти имеется один транзистор, образующий бистабильный элемент, и один транзистор управления, причем в качестве резистора используется слой 13, практически не занимающий дополнительной площади.

Формула изобретения

Яче.йка памяти, содержащая полупроводниковую подложку п -типа проводимости, эпитаксиальный слой р-.ти- па проводимости, расположенный на поверхности полупроводниковой подложки, первую и вторую диффузион.ные области п -типа проводимости, расположенные в приповерхностной области эпитаксиального слоя, первый слой диэлектрика, расположенный на поверхности эпитаксиального слоя, область первого слоя поликристаллического кремния, расположенную на первом слое диэлектрика между первой и второй диффузионными областями n -типа

проводимости, канавку, расположенную в эпитаксиальном слое и приповерхностной области полупроводниковой подложки, одна из сторон канавки при

мыкает к первой диффузионной обласt„ „

ти п -типа проводимости, второй слои

диэлектрика, расположенный внутри канавки, второй слой поликристаллического кремния, располеженньй на поверхности второго слоя диэлектри

ка, третий слой диэлектрика, расположенный на поверхности первого и второго слоев поликристаллического кремния, причем полупроводниковая подложка, первая диффузионная область п -типа проводимости и второй слой поликристаллического кремния образуют соответственно сток, исток и затвор запоминающего МДП-транзис- тора, первая, вторая диффузионные области п -типа проводимости и первый слой поликристаллического кремния образукгг соответственно исток, сток и затвор ключевого МДП-транзис тора, отличающаяся тем, что, с целью повышения степени инJ

20

Редактор В.Петраш

Составитель Б.Венков

Техред М.Дидык Корректор М.Шароши

Заказ 6297/52 Тираж 588 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4.

- g

3616274

теграции ячейки памяти, она содержит слой параэлектрика, расположенный на боковой поверхности канавки, при-.

мыкающей к первой диффузионной облас

10

ти п -типа проводимости, область второго слоя поликристаллического кремния, расположенная на поверхности первой диффузионной области п -типа проводимости, третий слой поликристаллического кремния, первый, второй и третий участки которого расположены соответственно на поверхности второго слоя поликристаллического крем15 нйя, поверхности участка третьего слоя диэлектрика, расположенного на втором слое поликристаллического кремния, и на поверхности участка первого слоя диэлектрика, расположен20 кого на поверхности первой диффузионной области п -типа проводимости, причем первый, третий участки третьего слоя поликристаллического кремния и второй слой поликристалличес25 кого кремния образуют соответственно исток, сток и затвор нагрузочного транзистора.

Г-

тжтг/

I

24

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель для запоминающего устройства | 1986 |

|

SU1361628A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2018994C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| Матричный накопитель для оперативного запоминающего устройства | 1987 |

|

SU1506482A1 |

| ВЕРТИКАЛЬНЫЙ МДП-ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108641C1 |

| МДП-транзистор | 1990 |

|

SU1762342A1 |

| МОЩНЫЙ СВЧ МДП - ТРАНЗИСТОР | 2001 |

|

RU2195747C1 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МДП ИС | 2006 |

|

RU2308119C1 |

| Способ изготовления силового полупроводникового транзистора | 2016 |

|

RU2623845C1 |

Изобретение относится к микроэлектронике и предназршчено для использования в цифровыхустройствах, в частности в запоминающих устройствах ЭВМ. Целью изобцетения является повьшение степени интеграции элемента памяти. Ячейка памяти содержит полупроводниковую подложку 1 п -типа, эпитаксиальный слой 2 р-типа, диффузионные области 3, 4, области 13, 5, 9 слоев поликристаллического кремния, слои диэлектрика 6, 11, 14, боковую поверхность 7 канавки в эпит- аксиальном слое, донную область 8 канавки, слой параэл.ектрика 10, омический контакт 12 полупроводникового слоя 9 с второй диффузной областью 4, омический контакт 15 третьего слоя поликристаллического кремния 13 с областью второго слоя поликрис- таллического кремния 9, омический контакт 16 слоя 13 с металлической.- шиной 17, участок 18 объединенного слоя области третьего слоя поликристаллического кремния, транзистор 19 типа метан-параэлектрик, МДП-тран- зистор 20 со встроенным каналом, уп равляющий ВДП-транзистор 21, вывод питания 22, шину строк 23 и шину столбца 24. Б ячейке имеется один . транзистор, образующий бистабильный элемент, и один транзистор управления, причем в качестве резистора используется слой 13,практически не занимающий площади. 2 ил. с ig

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Электроника, 1979, ti 11, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

Авторы

Даты

1987-12-23—Публикация

1986-06-02—Подача