(Л

ел

о ф 4

оо

1Ю

Изобретение относится к микроэлектронике и предназначено для использования в цифровых устройствах.

Цель изобретения уменьшение потребляемой мощности.

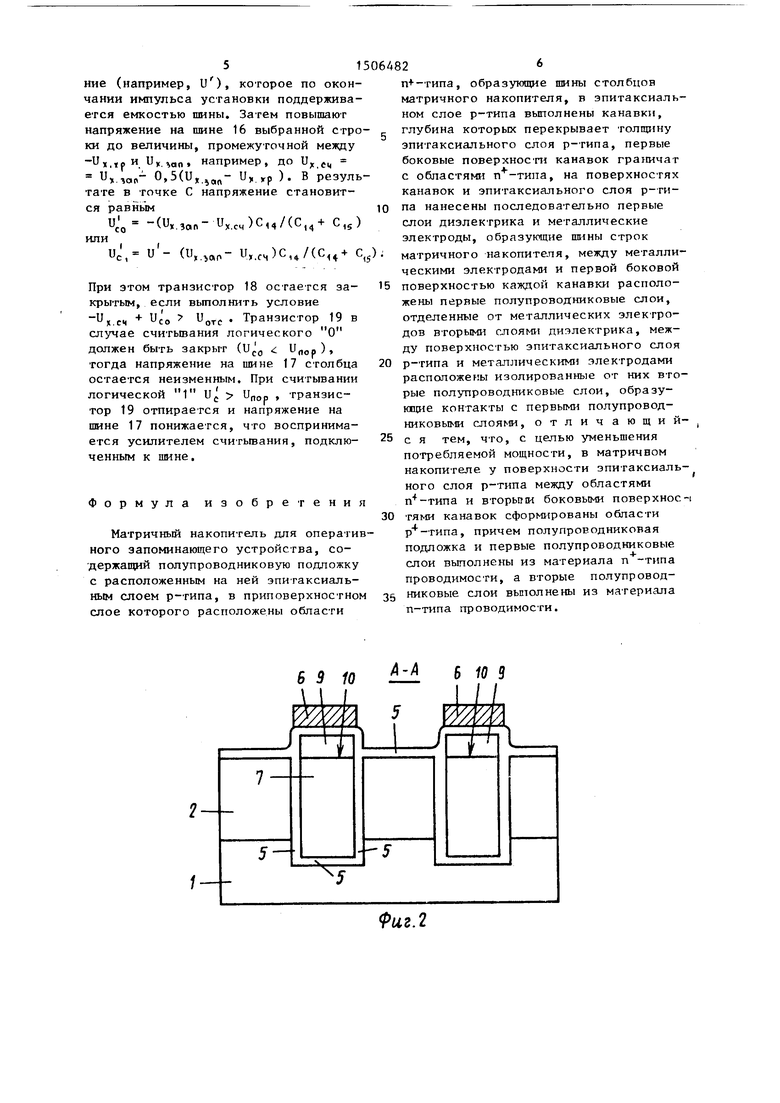

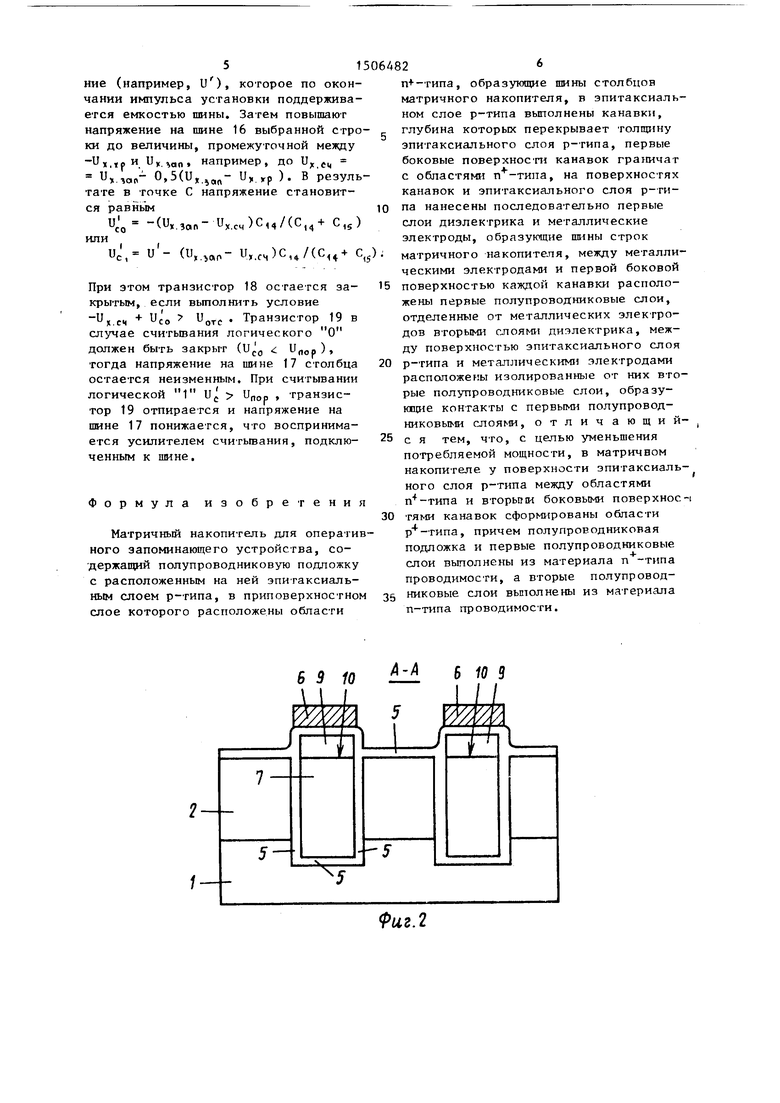

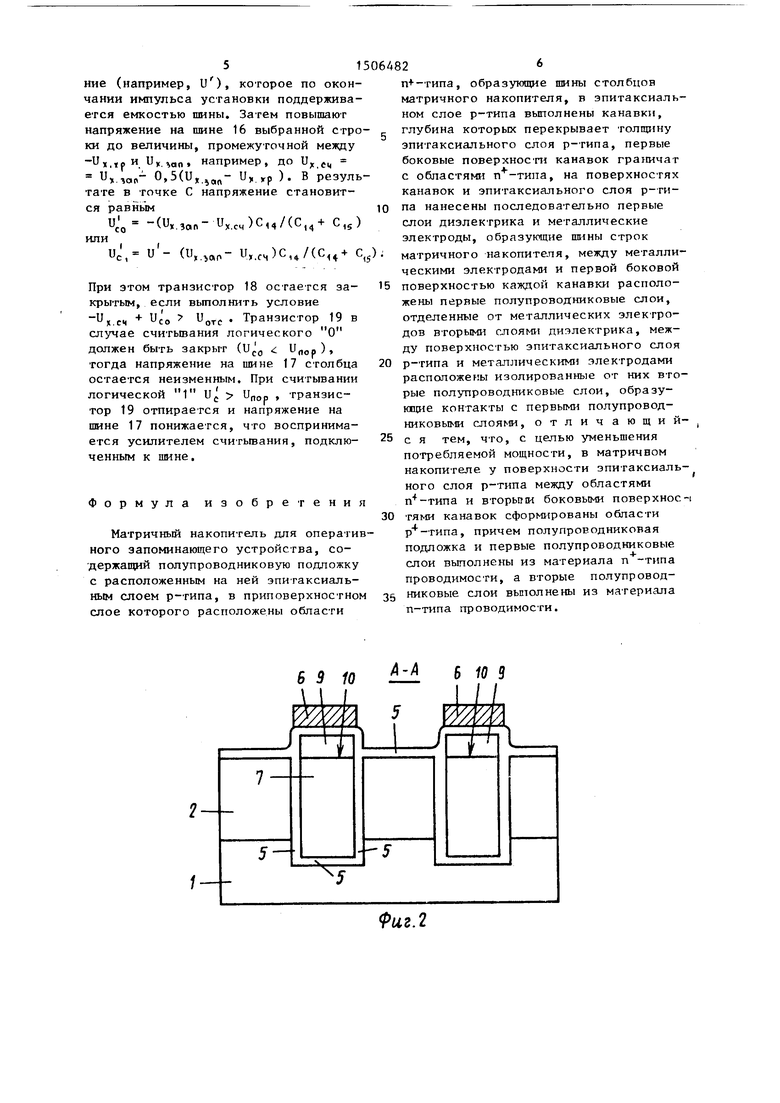

На фиг. 1 представлен матричный накопитель, поперечный разрез структуры, в направлении строки; на фиг. 2 - разрез А-А на фиг. 1; на фиг. 3 - разрез Б-Б на фиг. 1; на фиг. А - эквивалентная схема запоминающего элемента матричного накопителя .

Матричный накопитель содержит полупроводниковую, например, кремниевую подложку 1 п -типа и эпитакси- альный слой 2 р-типа, у поверхности которого содержатся области 3 п -типа, яв.пяющиеся ишнами столбцов. В эпнтаксиальном слое 2 выполнены канавки глубиной не менее толщины слоя 2, первые боковые поверхности 4 которых гран1етат с областями 3. На поверхностях канавок и эпитаксиаль- ного слоя 2 нанесены последовательно первые слои 5 диэлектрика и металлические электроды 6, являющиеся шинамь: строк. Между металлическ1ши злектродаи 1 6 и первой боковой поверхностью 4 каждой канавки содержатся псрчые полупроводниковые слои 7 п -ти1:а, отделенные от металлических электродов 6 вторыми слоями 8

0

5

(частью эпитаксиального слоя) и первым полупроводниковым слоем 7 образуют МДП-транзистор с индуцированным каналом п-типа. Слои 7, 9, 3 и 6 образуют соответственно исток,, канал, сток и затвор второго МДП-транзисто- ра со встроенным каналом п-типа. Слой 13 р -типа предотвращает возникновение паразитной связи между п -област ю 3 и подложкой 1 вдоль поверхности подложки и второй боковой поверхности 12 канавки.

Таким образом, запоминающий элемент имеет эквивалентную схему (фиг. 4)о На схеме обозначено: 14 - запоминающгй конденсатор, образованный слоями 6, 8, 7; 15 - запоминающий конденсатор, образованный слоями 7, 5, 2, 1; 16 - шина строки, 17 - шина столбца, 18 - МДП-транзистор со встроенным каналом п-типа, образованный слоями 7, 9, Зиби предназначенный дня записи информа- ции, 19 - МДП-транзистор 6 с индуцированным каналом п-типа, образованный слоями 1, 2, 3, 7 и предназначенный для считьгоания.

Т5 режиме записи на шину 17 столбца подается либо низкое напряжение лоптеского О (U - 0), либо положительное напряжение логической 1 (и ), а на шину 16 выбранной строки - положительное или нулепое на0

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1986 |

|

SU1361627A1 |

| Матричный накопитель для запоминающего устройства | 1986 |

|

SU1361628A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1983 |

|

SU1105055A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1025259A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1986 |

|

RU1398666C |

Изобретение относится к микроэлектронике и предназначено для использования в цифровых устройствах. Целью изобретения является снижение потребляемой мощности. Поставленная цель достигается за счет того, что в матричном накопителе у поверхности эпитаксиального слоя 2 р-типа между областями 3 N+ -типа и вторыми боковыми поверхностями 12 канавок сформированы области 13 р+ - типа, причем полупроводниковая подложка 1 и первые полупроводниковые слои 7 выполнены из материала р+ - типа проводимости, а вторые полупроводниковые слои 9 выполнены из материала N - типа проводимости. 4 ил.

И1ш) . К ежду поверхностью эпитаксиального слоя 2 и металли тескими элект- родам 6 расположены изолированные от них слоями 5 вторые полупроводнидиэлектрика (iianpn {ep, двуокиси крем- 35 пряжение Uy.jan - ото Д oтc

модуль напряжения отсечки транзистора 18. На невыбранньк immax строк напряжение отрицательно. Б выбранном запоминающем элементе транзис- ковые слои 9 п-типа, образующие оми- 40 тор 18 отпирается и в запом1 нающем

узле С (фиг. 4) устанавливается напряжение и или и . По окончании записи и при переходе в режим хранения на цгине 16 строки скачкообразно ус- областями 3 -типа и вторыми боковы- 45 танавливается отрицательное напряже- ми поверхностями 12 канавок сформированы области 14 р -типа.

Накопитель работает следующим образом.

ческие контакты 10 с первыми полупроводниковыми слоями 7 и омические контакты 11 с областями 3 n -типа. У поверхности эпитаксиального слоя между

ние и.

В

,р о точке С (фиг о 4) напряжение становится равным U. -(U,,an

)C,/(С ,+ 0,5) в случае хранения логического О или Не, U -(и,.,an- и,,,р)С,/(С,+ C,j) в случае хранения логической 1, где Ci5 емкости конденсаторов 14 и 15. Транзистор 18 запирается, для чего достаточно -Uv.xp + Uco отс Транзистор 19 также закрыт, для этого необходимо Uc пор пор о роговое напряжение При считьшании

Подложка и эпитаксиальный слой соединяются с нулевой шиной. Информация в запоминающем элементе хранится в виде напряжения на запоминающих конденсаторах, образованных соответ- ственно слоями 6, 7, 8 и 7, 5, 2, 1. Области 1 и 3 п -типа в каждом запоминающем элементе вместе с расположенной между ними областью р-типа

узле С (фиг. 4) устанавливается напряжение и или и . По окончании записи и при переходе в режим хранения на цгине 16 строки скачкообразно ус- танавливается отрицательное напряже-

ние и.

В

,р о точке С (фиг о 4) напряжение становится равным U. -(U,,an

)C,/(С ,+ 0,5) в случае хранения логического О или Не, U -(и,.,an- и,,,р)С,/(С,+ C,j) в случае хранения логической 1, где Ci5 емкости конденсаторов 14 и 15. Транзистор 18 запирается, для чего достаточно -Uv.xp + Uco отс Транзистор 19 также закрыт, для этого необходимо Uc пор пор о роговое напряжение При считьшании

на щинах 17 столбцов предварительно устанавливают положительное напряжение (например, U ), которое по окончании импульса установки поддерживается емкостью шины. Затем повышают напряжение на шине 16 выбранной строки до величины, промежуточной мезцду -и,,,р и , например, до U и, ,о1р- 0,5(и,„„- и, хр ). В результате в точке С напряжение становится paBHbiM

и, -(и

со

х.эап UX.CM )CH/((4 S

)

или

Ue, и - (U,.,o,o- и,.с,)С„/(С

U С,Р;

При этом транзистор 18 остается закрытым, если выполнить условие -Uj сц + UCQ Ug,. . Транзистор 19 в случае считьгоания логического О должен быть закрыт (11 и„(,р), тогда напряжение на шине 17 столбца остается неизменным. При считывании логической 1 и и„ор , транзистор 19 отпирается и напряжение на шине 17 понижается, что воспринимается усилителем считьшания, подключенным к шине.

Формула изобретения

Матричный накопитель для оперативного запоминающего устройства, содержащий полупроводниковую подпожку с расположенным на ней эпитаксиаль- ным слоем р-типа, в приповерхностном слое которого расположены области

6 3 10

;

п- --типа, образующие шины столбцов матричного накопителя, в эпитаксиаль- ном слое р-типа выполнены канавки, глубина которых перекрывает толщину эпитаксиального слоя р-типа, первые боковые поверхнос П канавок граничат с областями n -типа, на поверхностях канавок и эпитаксиального слоя р-ги10 па нанесены последовательно первые слои диэлектрика и металлические

электроды, образующие шины строк матричного накопителя, между металлическими электродами и первой боковой

15 поверхностью каждой канавки расположены первые полупроводниковые слои, отделенные от металлических электродов вторыми слоями диэлектрика, между поверхностью эпитаксиального слоя

20 р-типа и металлическими электродами расположены изолированные от них вторые полупроводниковые слои, образу- кщие контакты с первыми полупроводниковыми слоями, отличающий25 с я тем, что, с цепью уменьшения потребляемой мощности, в матричном накопителе у поверхности эпитаксиального слоя р-типа между областями п -типа и вторыпи боковыми поверхнос-i

30 тями канавок сформированы области p -типа, причем полупроводниковая подложка и первые полупроводниковые слои выполнены из материала п -типа проводимости, а вторые полупровод35 никовые слои вьтолнены из материала п-типа проводимости.

А-А В 10 9

иг.2

Г4:

f

1

фие.З

18

17

rt

фиеЛ

| Аваев Н.А., Наумов Ю.Е | |||

| Элементы сверхбольших интегральных схем.- М.: Радио и связь, 1986 | |||

| Матричный накопитель для запоминающего устройства | 1986 |

|

SU1361628A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-09-07—Публикация

1987-05-25—Подача