Изобретение относится к вычислительной технике и может быть использовано, в частности, при построении оперативных запоминающих устройств.

Цель изобретения - повышение степени интеграции.

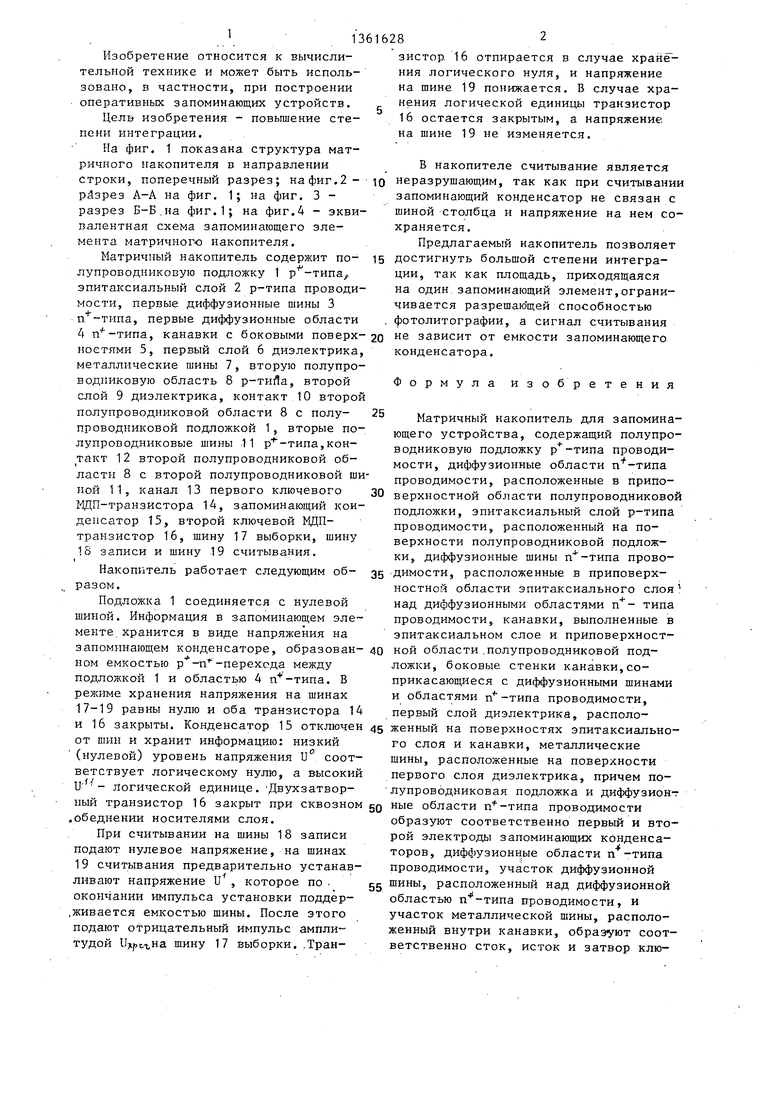

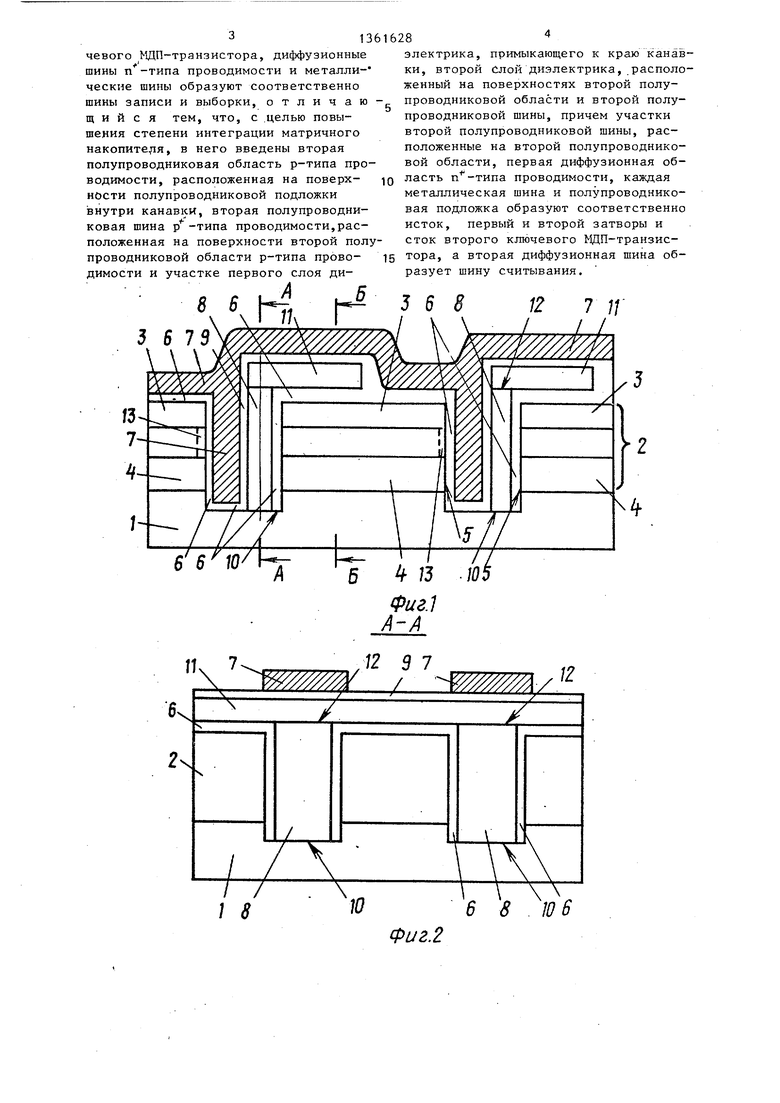

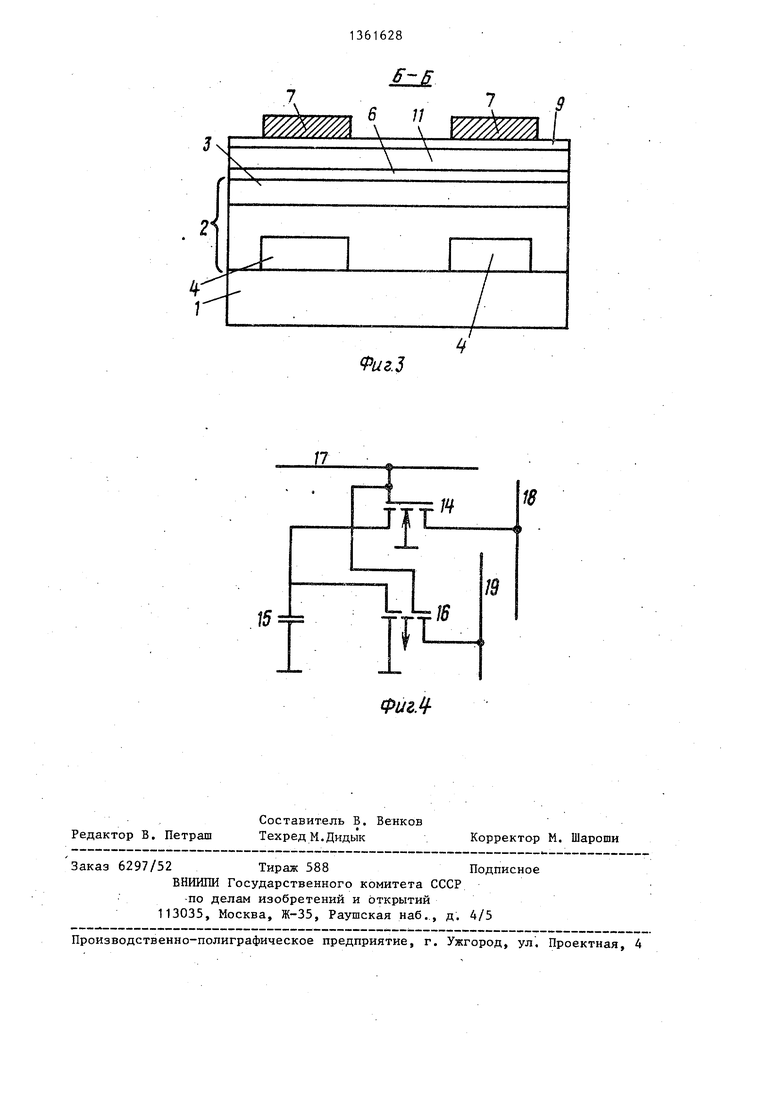

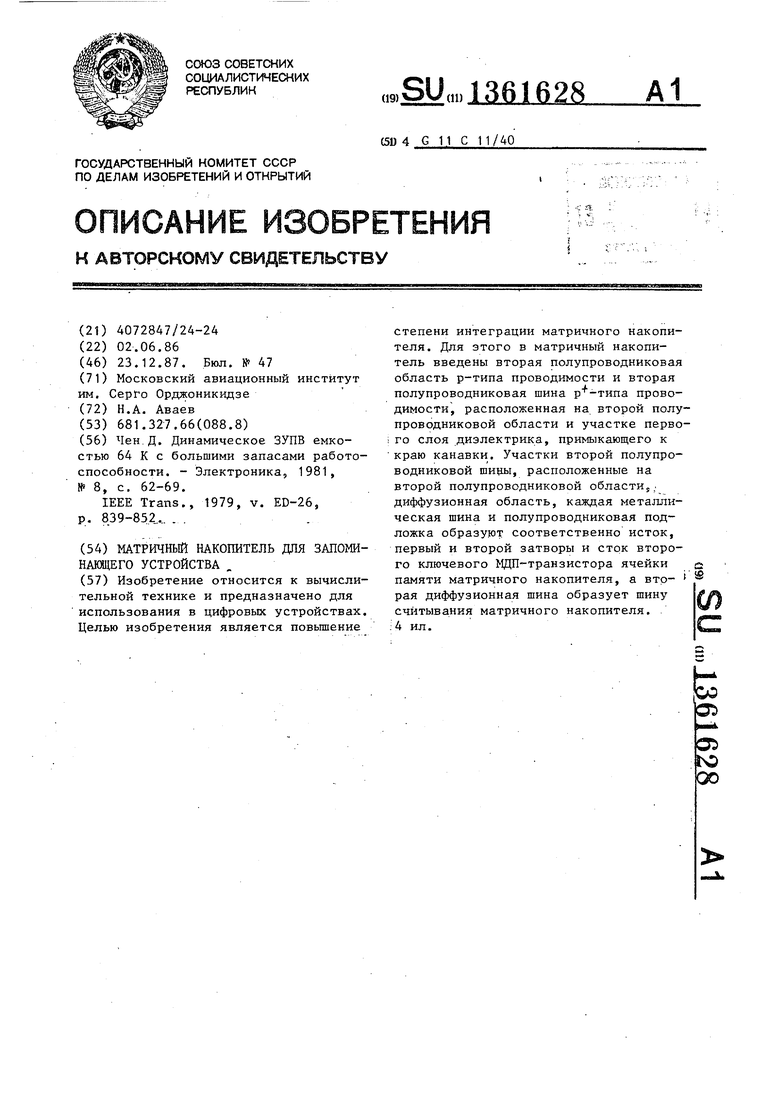

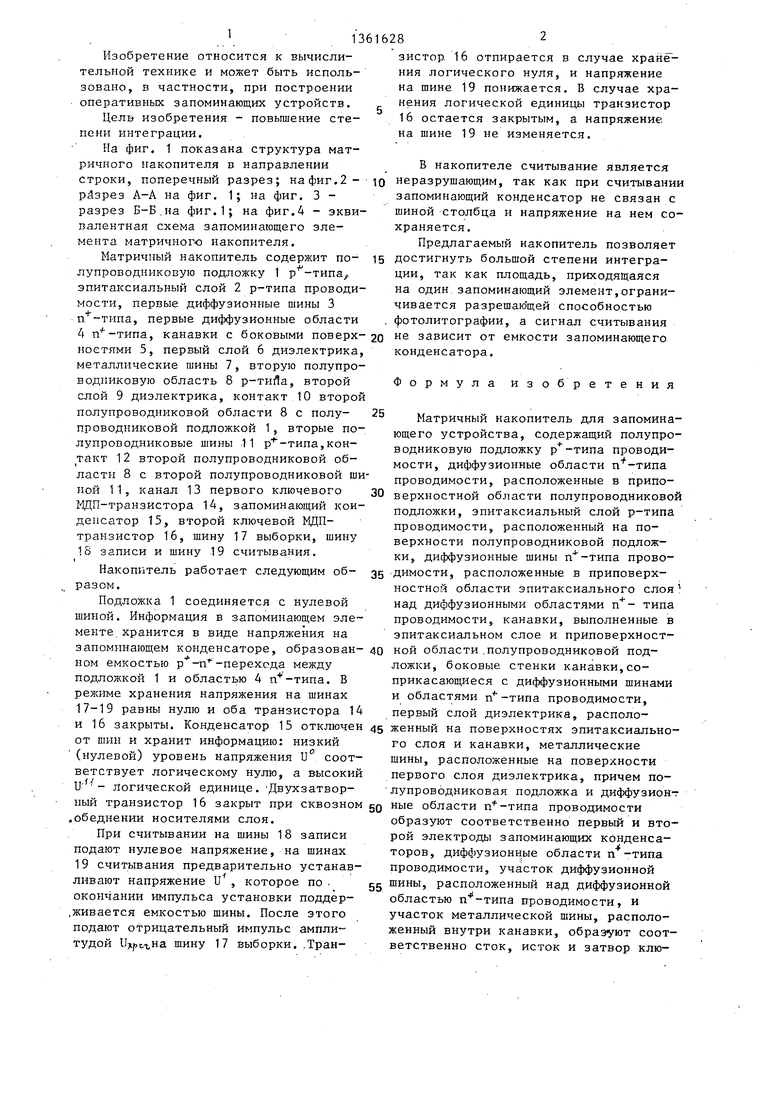

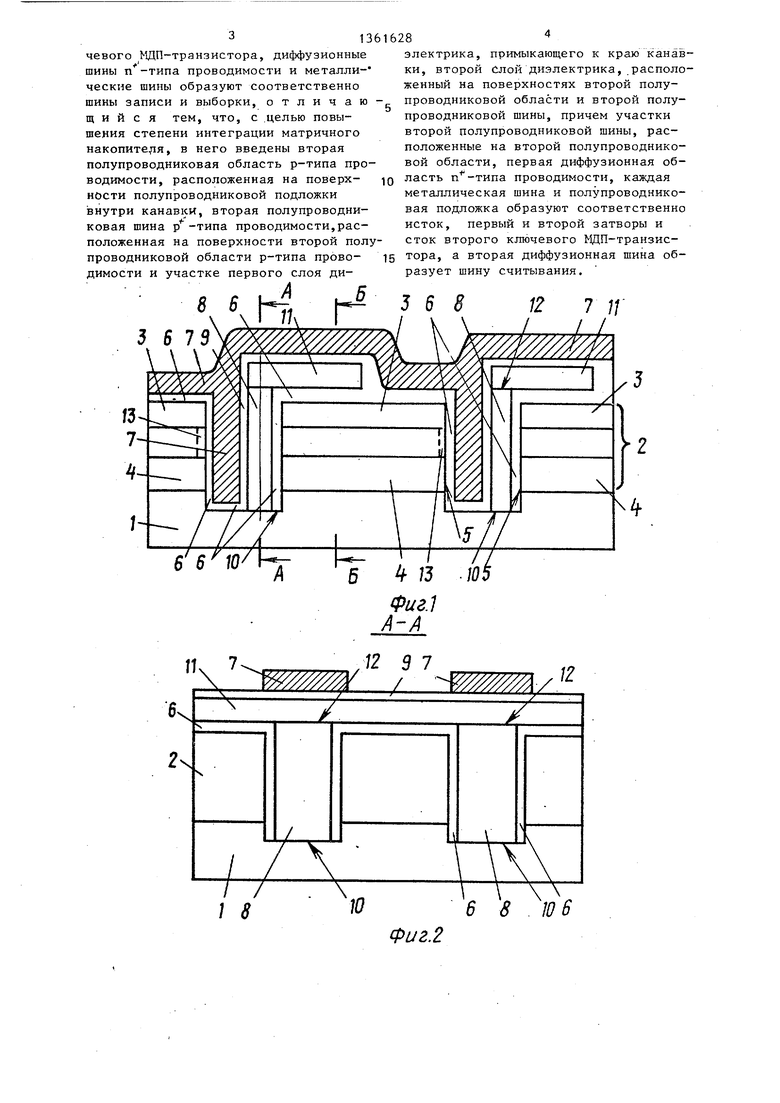

На фиг. 1 показана структура матричного накопителя в направлении строки, поперечный разрез; на фиг.2 - рйзрез А-А на фиг. 1; на фиг. 3 - разрез Б-Б.на фиг.1; на фиг.4 - эквивалентная схема запоминающего элемента матричного накопителя.

Матричный накопитель содержит полупроводниковую подложку 1 p -типа, эпитаксиальный слой 2 р-типа проводимости, первые диффузионные шины 3 n -типа, первые диффузионные области

4 n -типа, канавки с боковыми поверх-2о не зависит от емкости запоминающего иостями 5, первый слой 6 диэлектрика, металлические шины 7, вторую полупроводниковую область 8 р-тиЛа, второй слой 9 диэлектрика, контакт 10 второй полупроводниковой области 8 с полу- 25 проводниковой подложкой 1, вторые поконденсатора.

Формула изобретения

Матричный накопитель для запомина ющего устройства, содержащий полупро водниковую подложку р -типа проводимости, диффузионные области п -типа проводимости, расположенные в приполупроводниковые шины 11 р -типа, конМатричный накопитель для запоминающего устройства, содержащий полупроводниковую подложку р -типа проводимости, диффузионные области п -типа проводимости, расположенные в припотакт 12 второй полупроводниковой области 8 с второй полупроводниковой шиной 11, канал 13 первого ключевого ЗО верхностной области полупроводниковой ВДП-транзистора 14, запоминающий кон- подложки, эпитаксиальный слой р-типа деисатор 15, второй ключевой МДП- транзистор 16, шину 17 выборки, шину 18 записи и шину 19 считывания.

Накопитель работает следующим образом.

Подложка 1 соединяется с нулевой шиной. Информация в запоминающем элементе, хранится в виде напряжения на

запомгшающем конденсаторе, образован- 40 ной области.полупроводниковой под- ном емкостью р -п -перех.ода между ложки, боковые стенки канавки,со- подлолской 1 и областью 4 п -типа. В режиме хранения напряжения на шинах 17-19 равны нулю и оба транзистора 14

и 16 закрыты. Конденсатор 15 отключен 45 женный на поверхностях эпитаксиально- от шин и хранит информацию: низкий го слоя и канавки, металлические (нулевой) уровень напряжения U соответствует логическому нулю, а высокий логической единице. ДвухзатворНЫЙ транзистор 16 закрыт при сквозном gg

.обеднении носителями слоя.

При считывании на шины 18 записи подают нулевое напряжение, на шинах

проводимости, расположенный на поверхности полупроводниковой подложки, диффузионные шины n -типа прово- 35 димости, расположенные в приповерхностной области эпитаксиального слоя над диффузионными областями типа проводимости, канавки, выполненные в эпитаксиальном слое и приповерхностприкасающиеся с диффузионными шинами и областями п -типа проводимости, первый слой диэлектрика, располошины, расположенные на поверхности первого слоя диэлектрика, причем по- лупроводниковая подложка и диффузионт ные области n -типа проводимости образуют соответственно первый и второй электроды запоминающих конденсаторов, диффузионные области п -типа

19 считывания предварительно устанавливают напряжение U , которое по . окончании импульса установки поддер- .живается емкостью шины. После этого подают отрицательный импульс амплитудой ,Ha шину 17 выборки. .Транзистор. 16 отпирается в случае хранения логического нуля, и напряжение на шине 19 понижается. В случае хранения логической единицы транзистор 16 остается закрытым, а напряжение на шине 19 не изменяется.

В накопителе считывание является неразрушающим, так как при считывании запоминающий конденсатор не связан с шиной столбца и напряжение на нем сохраняется.

Предлагаемый накопитель позволяет достигнуть большой степени интеграции, так как площадь, приходящаяся на один запоминающий элемент,ограничивается разрещаю щей способностью фотолитографии, а сигнал считывания

не зависит от емкости запоминающего

конденсатора.

Формула изобретения

Матричный накопитель для запоминающего устройства, содержащий полупроводниковую подложку р -типа проводимости, диффузионные области п -типа проводимости, расположенные в приповерхностной области полупроводниковой подложки, эпитаксиальный слой р-типа

верхностной области полупроводниковой подложки, эпитаксиальный слой р-типа

проводимости, расположенный на поверхности полупроводниковой подложки, диффузионные шины n -типа прово- димости, расположенные в приповерхностной области эпитаксиального слоя над диффузионными областями типа проводимости, канавки, выполненные в эпитаксиальном слое и приповерхностной области.полупроводниковой под- ложки, боковые стенки канавки,со-

женный на поверхностях эпитаксиально- го слоя и канавки, металлические

прикасающиеся с диффузионными шинами и областями п -типа проводимости, первый слой диэлектрика, расположенный на поверхностях эпитаксиально- го слоя и канавки, металлические

шины, расположенные на поверхности первого слоя диэлектрика, причем по- лупроводниковая подложка и диффузионт ные области n -типа проводимости образуют соответственно первый и второй электроды запоминающих конденсаторов, диффузионные области п -типа

55

проводимости, участок диффузионной шины, расположенный над диффузионной областью n -типа проводимости, и участок металлической шины, расположенный внутри канавки, образуют соответственно сток, исток и затвор клю3136

чевого ВДП-транзистора, диффузионные шины п -типа проводи юсти и металли- ческие шины образуют соответственно шины записи и выборки, отличающийся тем, что, с .целью повышения степени интеграции матричного накопите;1я, в него введены вторая полупроводниковая область р-типа проводимости, расположенная на поверхности полупроводниковой подложки внутри канавки, вторая полупроводниковая шина р -типа проводимости,расположенная на поверхности второй полупроводниковой области р-типа проводимости и участке первого слоя ди1628

электрика, примыкающего к краю канавки, второй Слой диэлектрика,.расположенный на поверхностях второй полупроводниковой области и второй полупроводниковой шины, причем участки второй полупроводниковой шины, расположенные на второй полупроводниковой области, первая диффузионная ласть п -типа проводимости, каждая металлическая шина и полупроводниковая подложка образуют соответственно исток, первый и второй затворы и сток второго клк)чевого МДП-транзис15 тора, а вторая диффузионная шина образует шину считывания.

П

12 9 7

/ WMm/

12 9 7

/ Фиг.2

Редактор В. Петраш

Составитель В. Венков Техред М.Дидык

Заказ 6297/52 Тираж 588Подписное

ВНИИПИ Государственного комитета СССР

-по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Л

иг.З

Фиг.

Корректор М. Шароши

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель для оперативного запоминающего устройства | 1987 |

|

SU1506482A1 |

| Ячейка памяти | 1986 |

|

SU1361627A1 |

| Способ изготовления матричного накопителя для постоянного запоминающего устройства | 1989 |

|

SU1607621A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1986 |

|

RU1398666C |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1385872A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1987 |

|

SU1436735A3 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1980 |

|

SU888731A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1983 |

|

SU1105055A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

Изобретение относится к вычислительной технике и предназначено для использования в цифровых устройствах. Целью изобретения является повьшение степени интеграции матричного накопителя. Для этого в матричный накопитель введены вторая полупроводниковая область р-типа проводимости и вторая полупроводниковая шина p -типа проводимости, расположенная на второй полупроводниковой области и участке первого слоя дизлектрика, примыкающего к краю канавки. Участки второй полупроводниковой шицы, расположенные на второй полупроводниковой области5,. диффузионная область, каждая металггш- ческая шина и полупроводниковая подложка образуют соответственно исток, первый и второй затворы и сток второго ключевого МДП-транзистора ячейки памяти матричного накопителя, а втр рая диффузионная шина образует шину считывания матричного накопителя. : 4 ил. ,- 1

| Чен.Д | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| - Электроника, 1981, № 8, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| IEEE Trans., 1979, v | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Паровозный поршень, останавливающийся при езде без пара | 1924 |

|

SU839A1 |

| .. | |||

Авторы

Даты

1987-12-23—Публикация

1986-06-02—Подача