Изобретение относится к преобразованию информации и может найти применение в информационно-измерительных системах, гибридных вычислитель- ных комплексах, системах автоматического управления.

Цель изобретения - по1 ьппение на- дежности за счет упрощения преобразователя.

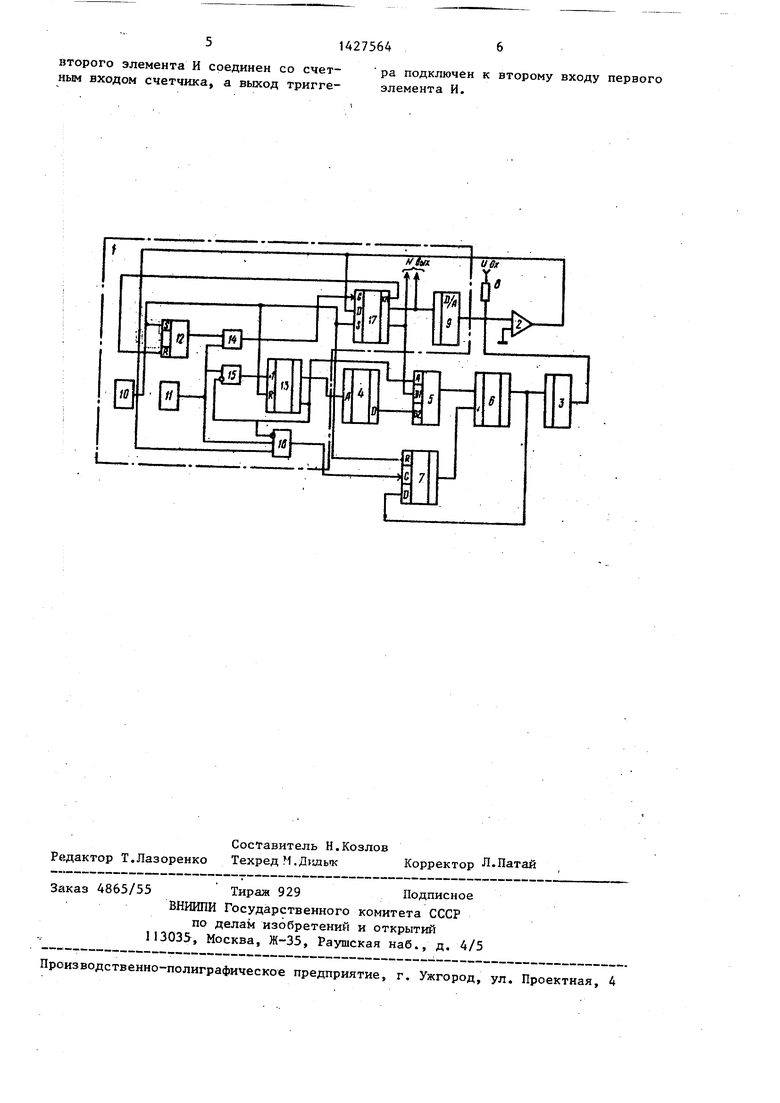

На чертеже приведена схема устройства.

Устройство содержит формирователь 1 компенсирующего напряжения, компаратор 2, первый цифроаналоговый пре- образователь (ЦАП) 3, постоянное запоминающее устройство (ПЗУ) 4, мультиплексор 5, сумматор 6, регистр 7, токоограничивающий элемент (резне тор) 8, причем формирователь ком- пенсирующего напряжения выполнен на втором цифроаналоговом преобразователе (ЦАП) 9, двух генераторах так- товых импульсов (ГТИ) 10 и 11, триггере 12, счетчике 13, трех элементах И 14-16, регистре 17 последовательного приближения (РПП).

Преобразователь работает следующим образом.

В ПЗУ 4 хранятся коды ошибок весо- вых коэффициентов восьми старших разрядов .

Процесс преобразования происходит за 16 тактов по методу последовательного уравновешивания. На цифроанало- говый преобразователь (ЦАП) 9 загружается код восьми старших разрядов, а в первые восемь .тактов преобразования на ЦАП 3 - коды поправок, соотвествующие кодам старших восьми разря- дов. В следующих восьми тактах на ЦАП 3 загружается результирующий код полученный как сумма кодов младших разрядов РПП 17 и сформированного кода поправки, соответствующий стар- шим разрядам РПП 17 и хранящийся в регистре 7.

Отклонения весов разрядов ,от идеальных значений определяются после изготовления кристалла ЦАП и записываются в ПЗУ.

При поступлении импульса первого генератора тактовых импульсов ГТИ 10 происходит установка триггера 12 в единичное состояние, сброс в нулевое состояние счетчика 13 и регистра 7, запуск РПП 17. Сигналом О с четвертого старшего разряда счетчика 13 происходит переключение мультиплек

0

5 0 5

0

Q

0

сора 5 на второй канал и разрешение прохождения тактовых импульсов через второй 15 и третий 16 элементы И, а сигналом с прямого выхода триггера 12 разрешается прохождение тактовых импульсов через первый элемент И 14 на вход синхронизации РПП 17. В первом такте преобразования по тактово- му импульсу с выхода первого элемента И 14 при наличии сигнала ГТИ 10 устанавливается в единичное состояние старший разряд РЩ1 17. Так как в первом такте сигналом ГТИ 10 блокируется импульс, поступающий с выхода второго элемента И 15 на счетный йсод счетчика 13, то счетчик будет находиться в нулевом состоянии, а на первые входы сумматора 6 через второй канал мультиплексора 5 подается код ошибки старшего разряда, считанный из ПЗУ 4 по нулевому адресу.

Код поправки, полученный как сумма кода ошибки старшего разряда и кода с выхода регистра 7, который в первом такте равен нулю, подается на цифровые входы ЦАП 3. В результате в первом такте в суммирующей точке первого входа компаратора 2 формируется аналоговый эквивалент, соответствующий весу старшего разряда и его поправки, который сравнивается со входным током. В зависимости от состояния компаратора 2 следующим тактовым импульсом, который поступает на вход синхронизации РПП 17, происходит сохранение или сброс единицы в старшем разряде РПП 17 и обязательный сдвиг этой единицы на один разряд в сторону младшего. Одновременно этот же тактовый импульс в зависимости от состояния компаратора 2 проходит на вход синхронизации регистра 7 через третий элемент.И 16. При сохранении единицы в текущем разряде РПП 17 в регистре 7 записывается код поправки с выхода сумматора 6, соответствующий коду РПП. Таким образом в регистре 7 сохраняется код поправки, соответствующий коду РПП, полученного в предьщущих тактах. Б результате в каждом такте преобразования в сум 1ирующей точке первого входа компаратора 2 формируется анало- говьй эквивалент, соответствующий коду старших восьми разрядов РПП и его поправки. В девятом такте при появлении сигнала 1 в старшем разряде счетчика 13 происходит переклю .

чение мультиплексора 5 на второй канал, блокировка счетньЕХ импульсов счетчика 13 и прохождения синхросигналов в регистр 7 через третий эле- мент И 16. Код младших .разрядов РГШ через первый канал мультиплексора 5 поступает на первые входы сумматора 6 и складывается с кодовой поправкой, зафиксированной в регистре 7 и соответствующей сформированному коду старших разрядов P11II. Результирующий код подается на ЦАН 3, Таким образом в девятом такте в суммирующей точке первого входа компаратора 2 формируется аналоговый эквивалент, соответствующий коду старших разрядов РПП, и сумма кодов младших разрядов РПП и поправки, который сравнивается со входным током. JB последующие . такты процесс уравновешивания происходит аналогично. По окончании урав новешивания импульс Конец преобразования РПП 17, поступающий на вход сброса триггера 12, сбрасывает его и блокируется поступление тактовьк импульсов на сход синхронизации РПП 17. В результате на выходе РШ1 полу чается преобразованный код входного тока.

По приходу следующего импульса ГТ описанный процесс повторяется.

Шкала ЦАП 3 -выбирается равной 1% от диапазона UAil У с учетом перекрытия его погрешностей. Общая точность аналого-цифрового преобразователя равна 0,005%, что соответствует 14 двоичным разрядам.

Ф.ормула изобретения

1. Аналого-цифровой преобразователь, содержащий компаратор, первый вход которого подключен к первому выходу формирователя компенсирующе- го напряжения и выходу цифроаналого- вого преобразователя, а выход соединен с управляющим входом формировате ля компенсирующего напряжения, второй выход которого соединен с входом постоянного запоминающего устройства отличающийся тем, что, с целью повышения надежности за счет упрощения преобразователя, в него введены мультиплексор, сумматор, ре- гистр и токоограничивающий элемент, вход которого является входной шиной, а выход соединен с первым входом компаратора, второй вход которог

5

0

5

Q

g .

0

5

подключен к общей шине, причем управляющий вход мультиплексора соединен с третьим выходом формирователя компенсирующего напряжения, четвертый выход которого подключен к первому информационному входу мультиплексора, второй информационный вход которого соединен с выходом постоянного запоминающего устройства, а выход - с первым входом сумматора, второй вход которого подключен к выходу регистра, вход сброса и вход синхронизации которого соединены соответственно с пятым и шестым выходами формирователя компенсирующего -напряжения, а информационный вход объединен с входом цифроанапогового преобразователя и подключен к выходу сумматора.

2. Преобразователь по п. 1, отличающийся тем, что формирователь компенсирующего напряжения выполнен на цифроаналоговом преобразователе, -двух генераторах тактовых импульсов, триггере, счетчике, трех элементах И и регистре последовательного приближения, выход конец преобразования которого соединен с входом сброса триггера, вход синхронизации - с выходом первого элемента И, информационный вход является управляющим входом формирователя, вход запуска объединен с входом сброса счетчика, входом уотанов: К триггера, является ПЯТЫМ выходок d-ормирователя и подключен к вд)1хо,,у первого генератора тактовых импульсов, выход старших разрядов - с входом цифроаналогового преобразователя, выход которого является первым выходом формирователя, выход младших разрядов регистра последовательных приближений является четвертым выходом формирователя, вторым выходом которого является первый выход счетчика, второй выход которого соединен с первыми входами-второго и,третьего элементов И и является третьим выходом формирователя, шестглм выходом которого является выход третьего элемента И, второй вход которого объединен с первым входом первого и вторым входом второго элементов И и подключен к выходу второго генератора тактовых импульсов, а третий вход третьего элемента И является управляющим входом формирователя, выход

514275646

второго элемента И соединен со счет- ра подключен к второму входу первого Ным входом счетчика, а выход тригге- элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Многоканальный аналого-цифровой преобразователь | 2023 |

|

RU2815253C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

Изобретение относится к технике преобразования информации и может найти применение в информационно- измерительных системах, гибрвдных вычислительных комплексах, системах автоматического управления. Цель изобретения - повышение надежности за счет упрощения устройства. Устройство содержит два восьмиразрядных цифроаналоговых преобразователя, регистр последовательного приближения, постоянное запоминающее устройство, мультиплексор, сумматор, регистр и компаратор. Наличие дополнительного цифроаналогового преобразователя позволяет производить коррекцию старших разрядов основного цифроаналогового преобразователя, что существенно уменьшает объем цифровой части аналого-цифрового преобразователя. Сущность изобретения состоит в том, что в процессе кодирования формируется напряжение поправки, что обес- печивает высокую точность преобразователя, а аппяратная реализация алгоритма , кодирования - его высокое быстродействие. Компенсация ошибок старших разрядов первого цифроаналогового преобразователя производится аналого-цифровым способом на втором цифроаналоговом преобразователе. 1 з.п. ф-лы, 1 ил. 4; Ю сд О) 4

| Зарубежная радиоэлектроника, 1984, № 2, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Проблемы создания преобразователей формы информации | |||

| Материалы II Всесоюзного симпозиума | |||

| Киев, 1973, с | |||

| Устройство для получения водяного пара и подведения его в толщу горящего топлива | 1921 |

|

SU377A1 |

Авторы

Даты

1988-09-30—Публикация

1985-07-02—Подача