Изобретение относится к вычислительной технике и может быть применено в цифровых измерительных приборах и арифметических устройствах,,

Целью изобретения является повьше- кне быстродействия.

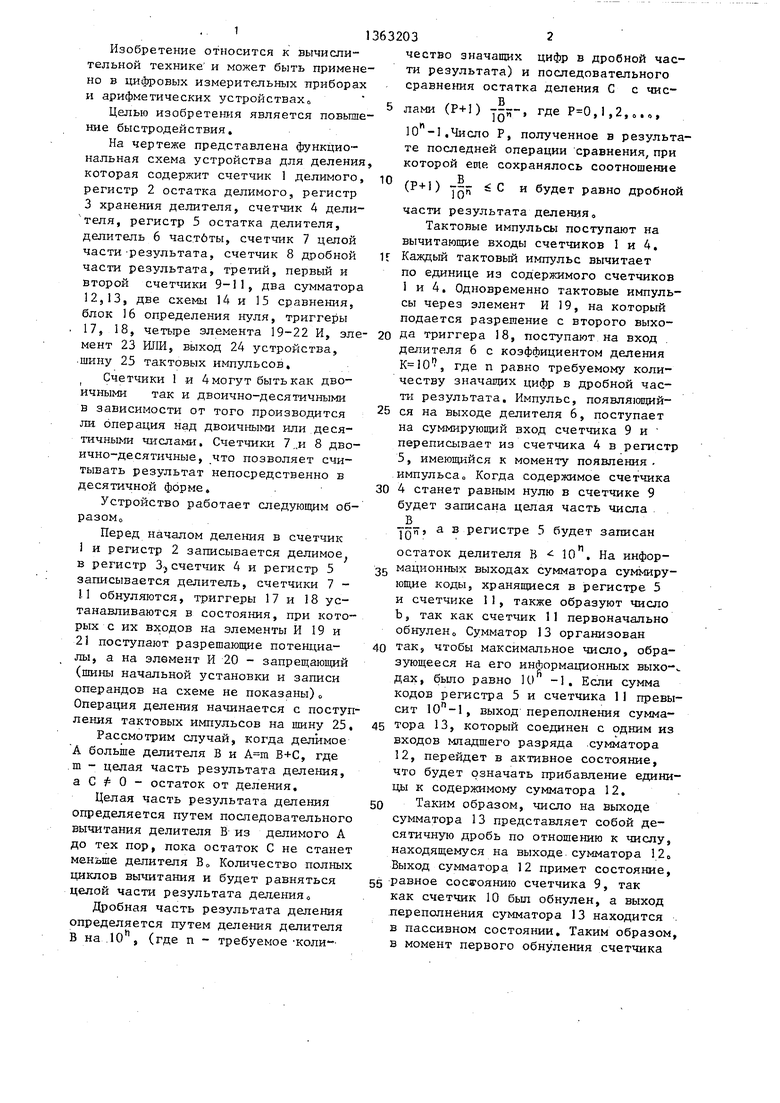

На чертеже представлена функциональная схема устройства для деления, которая содержит счетчик 1 делимого, регистр 2 остатка делимого, регистр 3 хранения делителя, счетчик 4 дели- теля, регистр 5 остатка делителя, делитель 6 частбты, счетчик 7 целой части-результата, счетчик 8 дробной части результата, третий, первый и второй счетчики 9-1, два сумматора 12,13, две схемы lA и 15 сравнения, блок 16 определения нуля, триггеры

честно значащих цифр в дробной ча ти результата) и последовательного сравне шя остатка деления С с чис В

10

,Число Р, полученное в резуль те последней операции сравнения, пр которой еще сохранялось соотношени

лами и

(Р+1) Т, где ,1,2,0.,,

10

(Р-1)т|;т с

и будет равно дробн

IF

части результата деления.

Тактовые импульсы поступают на вычитающие входы счетчиков 1 и 4, Каждьй тактовьй импульс вычитает по единице из содержимого счетчико 1 и 4, Одновременно тактовые импул сы через элемент И 19, на который подается разрешение с второго выхо

17, 18, четьфе элемента 19-22 И, эле- 20 Да триггера 18, поступают на вход

мент 23 ИЛИ, выход 24 устройства, шину 25 тактовых импульсов.

Счетчики 1 и 4 могут быть как двоичными так и двоично-десятичными в зависимости от того производится ли операция над двоич1-1ыми или .десятичными числами. Счетчики 7„и 8 двоично-десятичные, что позволяет считывать результат непосредственно в десятичной форме.

Устройство работает следующим об- разоМо

Перед началом деления в счетчик

Iи регистр 2 записывается дeлимoe в регистр Зп, счетчик 4 и регистр 5 записывается делитель, счетчики 7 IIобнуляются, триггеры 17 и 18 устанавливаются в состоя1шя, при которых с их входов на элементы И 19 и 21 поступают разрешающие потенциалы, а на элемент И 20 - запрещающий (шины начальной установки и записи операндов на схеме не показаны)о Операция деления начинается с поступления тактовых импульсов на шину 25,

Рассмотрим случай, когда делимое А больше делителя В и В+С, где .т - целая часть результата деления, а С 5 О - остаток от деления.

Целая часть результата деления определяется путем последовательного вычитания делителя В- из делимого А до тех пор, пока остаток С не станет меньше делителя В Количество полных циклов вычитания и будет равняться целой части результата деления о

Дробная часть результата делерщя определяется путем деле-ния делителя В на .10 J (где п - требуемое Коли честно значащих цифр в дробной части результата) и последовательного сравне шя остатка деления С с чис- В

10

,Число Р, полученное в результате последней операции сравнения, при которой еще сохранялось соотношение

лами и

(Р+1) Т, где ,1,2,0.,,

10

(Р-1)т|;т с

и будет равно дробной

части результата деления.

Тактовые импульсы поступают на вычитающие входы счетчиков 1 и 4, Каждьй тактовьй импульс вычитает по единице из содержимого счетчиков 1 и 4, Одновременно тактовые импульсы через элемент И 19, на который подается разрешение с второго выхоелителя 6 с коэффициентом деления , где п равно требуемому количеству значаш 1х цифр в дробной части результата. Импульс, появля сш(ийся на выходе делителя 6, поступает на суммирующий вход счетчика 9 и переписывает из счетчика 4 в регистр 5, имеющийся к моменту появления . мпульса о Когда содержимое счетчика

4 станет равным нулю в счетчике 9 будет записана целая часть числа

, а в регистре 5 будет записан

остаток делителя В 10 .На информационных выходах сумматора суммирующие коды, хранящиеся в регистре 5 и счетчике 11, также образуют число Ь, так как счетчик 11 первоначально обнулен Сумматор 13 организован

так, чтобы максимальное число, образующееся на его информационных выхо- дах, было равно 10 -1, Если сумма кодов регистра 5 и счетчика 11 превысит , выход переполнения сумматора 13, который соединен с одним из входов младшего разряда .сумматора 12, перейдет в активное состояние, что будет означать прибавление единицы к содержимому сумматора 12,

Таким образом, число на выходе сумматора 13 представляет собой десятичную дробь по отношению к числу, находящемуся на выходе.сумматора 2о Выход сумматора 12 примет состояние,

равное соса-оянию счетчика 9, так как счетчик 10 был обнулен, а выход переполнения сумматора 13 находится . в пассивном состоянии. Таким образом, в момент первого обнуления счетчика

3 . 1 4 на выходах сумматора 2 и 13 будут находиться значения соответственно целой и дробной частей числа /10. При обнулении счетчика 4 импульс переноса с его выхода поступит на вход триггера 18 и установит его в такое состояние, при котором он одним выходом запретит прохождение тактовых импульсов через элемент II 19 на делитель 6, а другим выходом выдаст разрешение на элемент И 20. Этот же импульс переноса поступит н вход записи счетчика 4 и перепишет в

него из регистра 3 значение В делите- 15 В,

7KF равна 1-гулю С т. ее ля. Одновременно импульс переноса че-

эле мент И 21, который подготовлен для прохождения импульса триггером 17, поступит на суммирующий вход счетчика 7, записав в него единицу, и ла вход записи регистра 2, .записав в него из счетчика 1 значение, равное разности делимого А и делителя В.

Значения регистров 2 и 3 сравниваются в схеме 14 сравнения , Если содержимое регистра 2 больше содержимого регистра 3, произойдет очередное полное вычитание делителя из содержимого счетчика 1 и прибавление единицы к содержимому счетчика 7, Этот процесс будет повторяться до тех пор, пока в регистре 2 не окажется записано число С А - тпВ В, где m - количество полных циклов вычитания делителя из содержимого счетчика 1 делимого. Тс,е, целая часть результата деления о В этом случае схема 14 сравнения вьодаст разрешение на элемент И 20. Схема 15 сравнения сравнивает остаток С с целой частью

Т5

числа ---. которое находится на выходах сумматора 12, Если С меньше цеВлой части числа -г-г с выхода схемы .

15 {выход Меньше) через элемент 1-ШИ 23 на выход 24 устройства поступит сигнал об окончании деления. Если остаток С равен целой части числа

В

ттг, то анализируется состояние выходов сумматора 13, Тоео определяется равна или не равна нулю дробная часть

Т)

числа В случае неравенства нулю

R

дробной части числа Тое, остаток С меньше числа ) блок 16 опре3

1

деления нуля выдаст сигнал на вход элемента И 22, на другой вход которого подается выход схемы 15 (выход Равно) , который находится в активном состоянии. С выхода элемента И 22 через элемент ИЛИ 23 на выход 24 также поступит сигнал об окончании деления. В указанных случаях дробная часть результата деления равна нулю для заданной точности, В том случае , когда остаток С равен целой

В части числа дробная часть числа

,

равна 1-гулю С т. ее

)

и,

сле

довательно, блок 16 не сформирует на выходе сигнал, а также в том случае, когда С больше целой части

В

т, а следовательно и всего числа

В ,с /

Ту i схема 15 своим выходом f выход

Больше-равно) устанавливает разре- шение на входе элемента И 20,

Итак, элемент И 20 пропускает на выход тактовые импульсы, так как на три других его входа поступают разрешения от триггера 18, схем 14 и 15 сравнения, С выхода элемента И 20 первый прошедший тактовый импульс запишет в счетчик 8 единицу, а в счетчики 10 и 11 - соответственно значения сумматоров 12 и 13, Так как выходы счетчиков 10 и 11 поступают соответственно на входы сумматоров 12 и 13, то на выходе сумматоров 12 и 13 образуются соответственно целая и дробная части числа

40 „ в

45

2 -ГрГ. Теперь с остатком С U нулем

будет уже сравниваться соответственно цел-ая и дробная части числа

2 - .

Таким образом, остаток С будет гравкиваться с числами (Р +

,П-1

0

5

В. 10

где Р 0,1, 2,... 10 до тех пор, пока он не станет меньше одного из этих чисел, что приведет к появлению, на выходе элемента l-UTI I 23 сигнала об окончании олерации деления. Прошедшее через элемент И 20 и записанное в счетчике 8 количество Р импульсов, при котором еще сохранярлось соотношение (Р+1) ттс; С, и

будет равно дробной части результа деления.

Необходимо отметить, что если в процессе определения дробной части результата счетчик 1 обнулился, то импульсом переноса он перебросит триггер 17, который своим выходом запретит прохождение через элемент И 21 импульсов переноса с выхода счетчика 4 делителя и не допустит изменения состояния счетчика 7,

Таким образом, дробная часть результата деления вычисляется после определения целой части в течение времени, необходимого для прохождния дополнительного количества имравного - -- ,

л о

где

пульсов,

К 10.

Рассмотрим случай, когда-делимое А меньше делителя В, В этом случае устройство работает аналогичным способом. Однако счетчик 7 останется в нулевом состоямии, так как счетчик

1обнулится раньше счетчика 4 и импульс переноса с выхода счетчика 1 перебросит триггер 17, который запртит прохождение импульсов переноса счетчика 4 через элемент И 21. По этой же причине содержимое регистра

2не будет меняться в течение всей операции делеьшяо

Время, в течение которого определяется результат деления, и teющeгo только дробную часть, равно време ш прохождения количества импульсов

Р В +

КГ в + --. в частности,

если для заданного п результат деления равен нулю, количество Р импульсов, будет пе больше величины В, так как по крайней мере к моменту обнуления счетчика 4 на выходах сумматоров 12 и 13 окажется число, превосходящее содержимое регистра 2 и с выхода схемы 15 сравнения или выхода элемента И 22 через элемент РШИ 23 поступит сигнал об окончании деления о

Накопец, рассмотрим случай, когда делитель В укладывается в делимом А целое число раз, а остаток С равен нулю, т.ео А ппБ. Б этом случае

40

45

50

чика, два сумматора и блок определения пуля, причем выходы счетчиков делимого и делителя соединены с информационными входами регистров остатка делимого и делителя .соответственно, выход регистра остатка делимого соединен с входами первого числа первой и второй схем сравнения, выход регистра хранения делителя соединен с информационным входом счетчика делителя и входом второго числа первой схемы сравнения, выход которой соединен с третьим входом второго элемента И, четвертый вход которого соединен с выходом Больше - равно второй схемы сравнения, выход

операция деления окончится сразу пос- Меньше которой соединен с первым

ле определения .целой части результа-входом элемента ИЛИ, второй вход

та ТоВо последний импульс, посту-которого соединен с выходом четвертопающий на вход счетчика 7, целой час-го элемента И, первый вход которого

ти результата запишет в регистр 2 остатка делимого нуль и схема 15 сравнения через элемент ИЛИ 23 выдаст на выход устройства сигнал об окончании деления о

Формула изобретения

Устройство для деления, содержащее счетчики делимого и делителя, регистр хранения делителя, делитель частоты, счетчики целой и дробной частей результата, два триггера,

четыре элемента И, элемент ИЛИ, причем шипа тактовых импульсов устройства соединена с первыми входами первого и второго элементов И и вычитающими входами счетчиков делимого и

делителя, выход -первого элемента И соединен с входом делителя частоты, выход переноса счетчика делимого соединен с входом сброса первого триггера, выход которого соединен с

первым входом третьего элемента И, второй ВХОД которого соединен с выходом переноса счетчика делителя, выход третьего элемента И соединен, со счетным входом счетчика целой части результата, прямой и инверсный выходы второго триггера соединены с вторыми входами первого и второго элементов И, выход элемента ИЛИ является выходом признака окончания деления устройства, отличаю- щ е е с я тем, что, с целью noBbmie- ния быстродействия, в него введены регистры остатков делимого и делителя, две схемы сравнения, три счет

0

5

0

чика, два сумматора и блок определения пуля, причем выходы счетчиков делимого и делителя соединены с информационными входами регистров остатка делимого и делителя .соответственно, выход регистра остатка делимого соединен с входами первого числа первой и второй схем сравнения, выход регистра хранения делителя соединен с информационным входом счетчика делителя и входом второго числа первой схемы сравнения, выход которой соединен с третьим входом второго элемента И, четвертый вход которого соединен с выходом Больше - равно второй схемы сравнения, выход

Меньше которой соединен с первым

13632038

соединен с выходом Равно второй которого соединен с входом разреше- схемы сравнения, вход второго числа ния записи счетчика делителя и вхо- которой соединен с выходом суммы дом сброса второго триггера, выход первого сумматора и информационным делителя частоты соединен с входом входом первого счетчика, вход разреше- разрешения записи регистра остатка ния записи которого соединен с выхо- делителя и счетным входом третьего дом второго элемента И, счетным вхо- счетчика, выход которого соединен дом счетчика дробной ,части результа- с первым информационным входом пер- та и входом разрешения записи второ- ю вого сумматора, второй информацион- го счетчика, информационный вход кото- ный вход которого соединен с выходом рого соединен с выходом суммы второ- первого счетчика, вход переноса пер- го сумматора и входом блока опреде- вого сумматора .соединен с выходом лёния нуля, выход которого соединен переноса второго сумматора, первый с вторым входом четвертого злемента 15 и второй информационные входы которо- И, вход разрешения записи регистра го соединены с выходами регистра ос- остатка делимого соединен с выходом татка делителя и второго счетчика со- третьего злемента ,И, второй вход ответственное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления | 1988 |

|

SU1532921A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для деления | 1983 |

|

SU1164698A1 |

Изобретение Относится к вычислительной технике и может быть применено в цифровых измерительных приборах и арифметических устройствах. Цель изобретения - повышение быстродействия устройства Устройство содержит счетчик 1 делимого, регистр 2 остатка делимого, регистр 3 га хранения делителя, счетчик 4 делителя, регистр 5 остатка делителя, делитель 6 частоты импульсов, счетчик 7 целой части результата, счетчик 8 дробной части результата, три счет- чика 9-11, два сумматора 12-13, две схемы 14-15 сравнения, блок 16 оп ределения нуля, два триггера 17-18, чётьфе элемента И 19-21, элемент ИЛИ 23, Повышение быстродействия ется за счет уменьшения времени определения дробной части результата, которая вычисляется путем деления делителя .В на 10 и сравнения остатка от деления с числами (Р + }) В т п, где п - заданное количество значащих цифр в дробной части результата деления, Р 0,1 ,2,, ,. ,п-1« 1 ил. ё

| Устройство для деления | 1974 |

|

SU512468A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-13—Подача