(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

19 «Запуск начальной установки триггера управления.

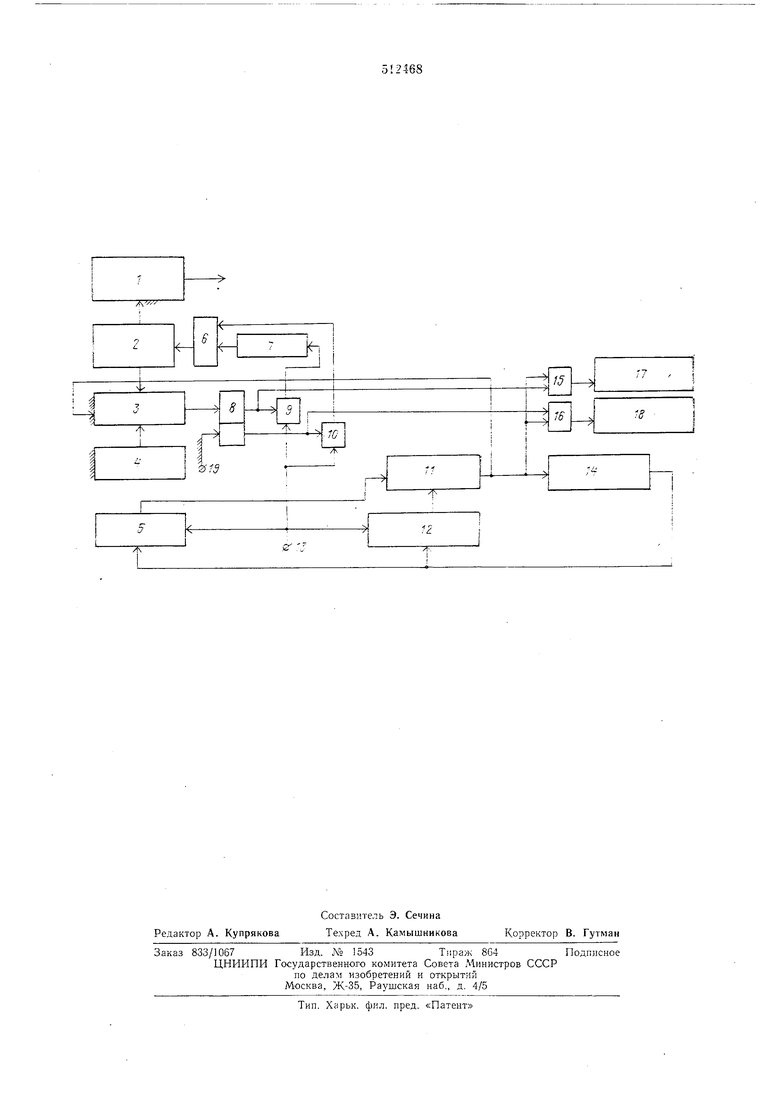

Работа устройства происходит следующим образом.

Перед началом цикла Вычисления в регистр 2 делимого записывается делимое, в регистр 4 памяти и iB регистр 5 дел-ителя - делитель, буферный регистр 12 приводится в нулевое состояние.

Сигнал «а входе 19 «Запуск устанавливает триггер 5 в такое состояние, при котором элемент «И W -подготовлен для пропускавия импульсов с входа 13 устройства, а эле.мент «И 9 закрыт для пропускания этих импульсов. Триггер 14 реверса находится в состоянии, iKOTOipoe в,ключает .в регистре 5 дел;ителя вычитающий вход, а в буферном регистре 12 сум.мирующлй вход.

11|мпульсы, поступающие па вход 13, поступают На .вычитание в регистр 5 делите тя, на суммирование в буферный репистр 12; па в.ход элемента «И 10 и через элемент «ИЛИ 6 на вычитание в репистр 2 дел имого.

После того, как блок // обнаружит ;нулеiSoe состояние регистра 5 делителя, он выдает импульс, «оторый мЗМенит состояние триггера 14 (реверса, поступит на разрешающий вход блока 5 сравнения (кодов), поступит на вход элемента «И 16.

После этого момента регистр 5 делителя начнет работать на суммирование, буферный репистр 12 - на вычитание.

Бло;к 5 сравибния про:из1водит сравнение кодов регистра 4 памяти (де тителя) и регистра 2 делимого. Блок 3 .сравнения выдает на выход сигнал только в том случае, если число в репистре 4 памяти больше числа в регистре 2 делимого и на выходе блока // .присутствует импульс.

В противном случа-е на его в,ыходе сигнал jfie появляется т. е. до тех пор, пака не определена целочисленная часть частного, блок 5 сравнения не срабатывает.

На вход счетчика 18 целого результата через элемент «И 16 поступит импульс, поскольку на второй ВХОД этого элемента «И поступает разрешающий сигнал с выхода триггера 8 упра;вления. Запрещающий сигнал указанного триггера запирает элемент «И /5. Таким образом, делимое уменьщается на величину делителя. Затем по мере Поступления импульсов иа вход логиче ский обнаружит обнуление буферного регистра 12. Импульс с выхода бло,ка // повторит уже описанный путь, после чего делимое в регистре 2 ВНОВЬ уменьшится на величину делителя.

Этот процесс будет продолжаться столько раз, сколько раз делитель целиком уложится в делимом. Это количество определит целочислениую часть частного.

Когда число в регистре 2 дели.мого впервые окажется (меньше, чем число в 1регистре 4 памяти, а иа выходе бло,ка 11 появится очередной |Импульс, блол 3 сравнения выдает импульс, который изменяет состояние триггера

8 управления, после чего элемент «И 10 и элемент «И 16 закрыты для прохождения импульсов, а элемент «И 9 и эле.мент «И 15 подготовлены для пропускания соответствующих

сигналов.

Теперь импульсы с входа 13 устройства через эле.мент «И 9 поступают на вход делителя 7, поэтому на вход релистра 2 делимого поступают импульсы, частота которых в К раз

меньше, чем частота и.М1пульсов на входе 13 устройства. На входах регистра 5 делителя, буферного регистра 12 частота импульсов остается неизменной.

Далее .процесс продолжается таким же образо.м, ка.к описано выше, за исключением того, что и.мпульсы с выхода блока // через эле.мент поступают на вход счетчика 17 дробного результата. Процесс деления будет продолжаться до тех пор, пока .не сработает

блок 1 выявления -нулевого состояния регистра делимого.

Рассмотрим, iKaiKoe ч.исло 0:кажется в счетчике дробного результата по окончан1ии олерации деления.

Время, 3 течение которого счетчик /7 будет заполняться импульсами, разно:

(I)

t К is

где / - время заполнения счетч.ика /7;

Л - коэффициент деления делителя 7; .V - делимое (число, записанное в регистре дели.мого 2); /Уц - целая часть частного, записанная

в счетчике 18; fв - период сле:дова:ния импульсов на

входе устройства 13.

За это время на входе счетчика 17 появится число импульсо-в

)

/ .м

/вх-Л д

Rv ;т

,,)

(П) N,

где Лд - делитель (число, записанное з регистрах 4, 5).

Из формулы II ВИДНО, что увеличивая ДО можно добиться любой необходимой точности частного.

П р и .м е р. Пусть делимое 20, делитель 6; необ.ходи.мо получить частное с точностью до двух знаков после запятой. - Выбираем К 100.

После запуска устройства по 1входу 19 «ЗаinycK на выходе логического блака 11 появится три импульса, которые через открытый элемент «И 16 поступят на счетчик /8 целого результата.

После появления третьего импульса блок 3 сравнения выдает сигнал, поскольку к этому моменту :в регистре 2 делимого записано число 2, а 3 регистре памяти 4 - число б; триггер 8 изменяет свое состояние.

;В соответстзии с формулой II з С4етчи.л /7 дробного результата поступит «др ч::сло импульсов, а именно:

100(20-18)

: 00

6

Таким образом, частное определится как показания обоих счетчиков, отделенные запятой, а именно 3,33.

За это время через вход устройства поступит 33x6 198 импульсов, т. е. после поступления еще двух импульсов, 1которые уже не влияют на полученный результат, блок / зарегистрирует нулевое состояние регистра 2 и выдаст сигнал на оконча.ние деления;

Задавшись К 1000, можно получить три 3)На,ка после залятой и т. д.

Формула изобретения

Устройство для деления, содержащее счетчик целого результата, элементы «И, «ИЛИ, регистр делимого, первый выход которого соединен с блоком .выявления нулевого состояния репистра делимого, регистр делителя, выход которого через блок оиределения нулевого состояния регистра делителя и буферного регистра и триггер резерса соеди.ке;н с первым входам буферного регистра и первым входом

регистра делителя, второй вход лоторого соединен со входом устройства и со вторым входом буферного регистра, выход которого соединен с соотззтствующнм входом блока оиределания нулевого состояния регистра делителя и буферного регистра, отличающееся тем. что, с целью повыщения точности устройства, В него введены счетчик дробного результата, делитель, триггер управления, регистр

памяти и блсхк сразиенля, первый вход которого соединен с регистром памяти, второй вход -соединен со входом триггера реверса и с первыми входами первого и второго элемента «И выходы которых соответствеино соединены

ico счетчиками дробного и целого результатов, вторые входы первого и второго эле.ментов «И соединены с первы.м и вторым выходами триггера управления и с первыми входами третьего и четвертого элементов «И, вторые входы которых соединены с входом устройства, выход третьего элемента «И соединен с входом делителя, выход которого соединен с первым входо;. элемента «ИЛИ, второй в.ход которого -соединен с выходом четвертого элемента «И,

выход которого соединен с входом регистра делимого, зторой выход которого соединен с третьим входом блока сравнения, выход которого соединен с первым .входом триггера улзазления, второй вход .которого соединен с

шиной начальной установки триггера управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Устройство для деления | 1977 |

|

SU693372A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления | 1980 |

|

SU903867A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Устройство для деления | 1979 |

|

SU809176A1 |

| Устройство для деления | 1986 |

|

SU1363203A1 |

| Устройство для умножения и деления | 1975 |

|

SU600555A1 |

/

A-.

Авторы

Даты

1976-04-30—Публикация

1974-05-23—Подача