г|истр 4 делителя, регистр 5 остатка Делимого, дополнительный регистр 6, qflBHraranym регистр 7, первый и второй сумматоры 8, 9, коммутатор 10, счетчик 11 результата, состоящий из (п+1) параллельно включенных счетчиков 11-1, 11-2, 11-3,. о., П-(п+1), первый и второй элементы 12, 13 задержки, элемент НЕ 14, первый и второй элементы ИЛИ 15, 16, элемент И 17, схему 18 сравнения, дешифратор 19 нуля, преобразователь 20 кода,шину 21 управления, вход 22 тактовой частоты, шину 23 1 и выход 24, соединенные между собой функционально. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1980 |

|

SU928344A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1983 |

|

SU1130860A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

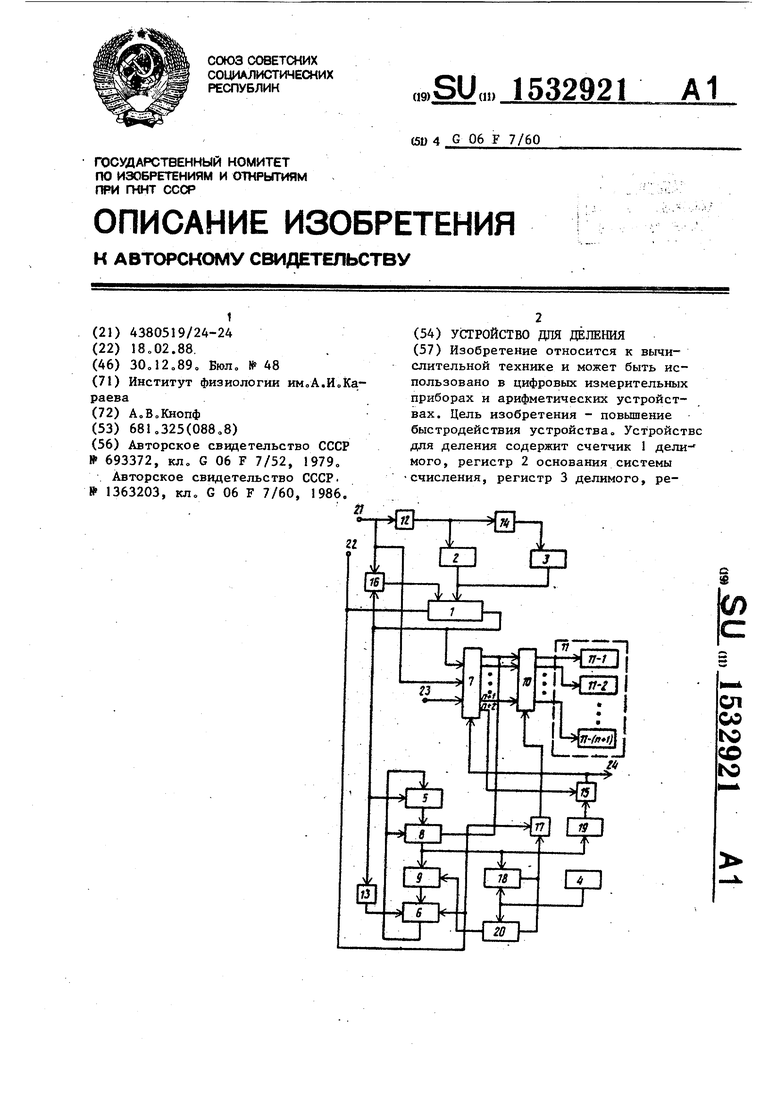

Изобретение относится к вычислительной технике и может быть использовано в цифровых измерительных приборах и арифметических устройствах. Цель изобретения - повышение быстродействия устройства. Устройство для деления содержит счетчик 1 делимого, регистр 2 основания системы счисления, регистр 3 делимого, регистр 4 делителя, регистр 5 остатка делимого, дополнительный регистр 6, сдвигающий регистр 7, первый и второй сумматоры 8, 9, коммутатор 10, счетчик 11 результата, состоящий из N + 1 параллельно включенных счетчиков 11-1, 11-2, 11-3, ... 11-(N+1), первый и второй элементы 12, 13 задержки, элемент НЕ 14, первый и второй элементы ИЛИ 15, 16, элемент И 17, схему 18 сравнения, дешифратор 19 нуля, преобразователь 20 кода, шину 21 управления, вход 22 тактовой частоты, шину 23 логической единицы и выход 24, соединенные между собой функционально. 1 ил.

Изобретение относится к вычисли- тельной технике и может быть использовано в цифровых измерительных при- (jiopax и арифметических устройствах.

Цель изобретения - повышение быстродействия.

На чертеже представлена функциональная схема устройства.

Устройство для деления содержит счетчик 1 делимого, регистр 2 основания системы счисления, регистр 3 делимого, регистр 4 делителя, регистр 5 остатка делимого, дополнительный регистр 6, сдвигающий регистр 7, первый 8 и второй 9 сумматоры, коммута- гор 10, счетчик 11 результата, состоящий из (п+1) параллельно включенных счетчиков 11-1, 11-2,.„.11(п+1) , первый 12 и второй 13 элементы за держки, элемент НЕ 14, первый 15 и второй 16 элементы ИЛИ, элемент И 17, схему 18 сравнения, дешифратор 19 нуля, преобразователь 20 кода, шину 21 управления, вход 22 тактовой частоты, шину 23 1 и выход 24, соединенные между собой функционально„ Регистры 2 и 3 выполнены с тремя состояниями на выходе ,,

Устройство работает следующим образом

Перед началом деления в регистр 2 записывается код основания В системе счисления, в которой осуществляется деление чисел, в регистр 3 - делимое М, в регистр 4 - делитель N, счетчики 1,11-1, 11-2,0ос,11-(п+1) и регистры 5, 6 и 7 обнуляются (шины начальной установки и записи операндов на схеме не показаны)„ Пока на шине 21 управления не установлен актив ный сигнал, на управляющий вход регистра 2 основания системы счисления поступает запрещающий уровень, при котором выход регистра 2 находится в третьем (высокоимпедансном)

0

5

0

5

Q

5

0

5

состоянии, а на управляющий вход регистра 3 делимого через элемент НЕ 14 поступает разрешающий уровень, т.е. содержимое регистра 3 поступает на информационный вход счетчика 1 делимого о

Операция деления начинается с установки активного уровня на шине 21, который поступает на вход записи сдвигающего регистра 7 и переписывает единицу с шины 23 в первый разряд этого регистра. Одновременно сигнал с шины 21 через элемент ИЛИ 16 поступает на вход записи счетчика 1 и переписывает в него делимое из регистра 3„ Элемент 12 задержки задерживает распространение сигнала с шины 21 на время, достаточное для записи делимого в счетчик 1, после чего выход регистра 3 делимого переходит в третье состояние, а код основания В системы счисления с выхода регистра 2 поступает на информационный вход счетчика 1„

После установки активного уровня на шине 21 на вход 22 начинают поступать импульсы тактовой частоты Каждый тактовый импульс вычитает единицу из содержимого счетчика 1 и запись в регистр 6, Сумматор 8 суммирует содержимое регистра 5, которое пока равно нулю, с содержимым регистра 6, которое меняется с приходом тактовых импульсов, и единичным кодом, поступающим с первого выхода сдвигающего регистра 7. Выходной код сумматора 8 через сумматор 9 поступает на информационный вход регистра 60 Таким образом, содержимое регистра 6 и код на выходе сумматора 8 увеличиваются на единицу с приходом каждого тактового импульса, причем код на выходе сумматора 8 все время на единицу больше содержимого регистра 6.

Рассмотрим случай, когда делимое М больше делителя N.

Схема 18 сравнения сравнивает код на выходе сумматора 8 с кодом делителя, записанным в регистре 4. Как только эти коды становятся равными, выход схемы 18 сравнения переходит в активное состояние и разрешает преобразование прямого кода делителя в дополнительный код, которое осуществляет преобразователь 20 кода. При пассивном состоянии выхода схемы 18 сравнения на выходе преобразователя 20 находится нулевой код.

Дополнительный код делителя поступает на второй вход сумматора 9, на первый вход которого поступает выходной код сумматора 8„ Таким образом, сумматор 9 вычитает делитель из выходного кода сумматора 8, который также равен делителю, Toe на информационный вход регистра 6 поступает нулевой код

Очередной тактовьй импульс через элемент И 17, открытый активным уровнем выхода схемы 18 сравнения, поступает на информационный вход коммутатора Ю„ На первый управляющий вход коммутатора 10 с первого выхода сдвигающего регистра 7 поступает единичный уровень, поэтому тактовьй импульс с информационного входа коммутатора 10 поступает на его первый выход, а затем - на счетный (суммирующий) вход счетчика 11-1,

По этому же тактовому импульсу в регистр 6 записывается нулевое значение , после чего выход схемы 18 сравнения переходит в пассивное состояние, закрывает элемент И 17 и устанавливает нулевой код на выходе преобразователя 20 кода„

Описанный цикл повторяется до тех пор, пока содержимое счетчика 1 делимого не станет равным нулю Как. только это происходит, на выходе . счетчика 1 формируется импульс, который поступает на вход сдвига регистра 7 и сдвигает единицу с его первого выхода во второй, отключая счетный вход счетчика 11-1 и подключая информационный вход коммутатора 10 к счетному входу счетчика 11-2„ Одновременно импульс с выхода счетчика 1 поступает на его вход записи через элемент ИЛИ 16, что приводит к перезаписи из регистра 2 в этот счетчик основания В системы счисления„ Этот

же импульс осуществляет перезапись содержимого регистра 6 в регистр 5 и обнуление регистра 6 с некоторой задержкой, достаточной для этой пе- резаписИо Задержку обеспечивает элемент 13 задержки.

Таким образом, после обнуления

0 счетчика 1 делимого в счетчике 11-i записывается целая часть результата деления, а в регистре 5 - некоторая величина С ,, являющаяся остатком делимого после определения целой части

5 результата деления 0

Теперь на выходе сумматора 8 формируются суммы: С1+С,2С, ; ЗС,; .,, , (0+1)0,, где , 2, 3„ Как только величина (т+ОС

0 становится равной или большей делителя, выход схемы 18 сравнения переходит в активное состояние, на выходе сумматора 9 формируется разность (m+l)C -N, элемент И 17 открывает5 ся0 Очередной тактовый импульс запи- сьцзается в счетчик 11-2, разность Г(т+1)С,-к - в регистр 60

Далее процесс продолжается до тех пор, пока вновь не обнулится счет0 чик 1. Очевидно, что к этому моменту в счетчике 11-2 записано число, равное целой части отношения , т.е. значение первого после запятой разряда дробной части результата деления М на N. После обнуления счет- чика 1 в регистре 5 записана некоторая величина С2, являющаяся остатком делимого после определения первого дробного разряда результата деления,

л В сдвигающем регистре 7 единичный уровень сдвигается на третий выход, т.е. теперь импульсы с информационного входа коммутатора 10 поступают на счетный вход счетчика 11-3, в ко5 тором подсчитывается значение второго после запятой разряда дробной части результата деления„

Операция деления продолжается до тех пор, пока единичный уровень не

0 окажется на (п+2)-м выходе сдвигающего регистра 7, где п - заданное количество разрядов в дробной части результата деления , Через элемент ИЛИ 15 активный сигнал с (п+2)-го

е выхода регистра 7 поступает на выход 24 устройства для считывания результата и завершения операции деления,, Этим же сигналом сдвигающий регистр 7 обнуляется

5

715

В том случае, когда делимое М меньше делителя N, на этапе определения целой части результата деления счетчик 1 делимого обнуляется раньше, чем на выходе схемы 18 сравнения формируется активный уровень, и в счетчике 11-1 целой части результата остается записанным нулевое значе- ние.

Дешифратор 19 нуля позволяет ус- к4рить вычисление, так как если на выходе сумматора 8 устанавливается нулевое значение, т.е. остаток делимого на каком-то промежуточном эта1- пе равен нулю, на выходе дешифратора 19 формируется импульс, который че- рбз элемент ИЛИ 15 проходит на выход 24 устройства, и операция деления заканчивается„

Фо-рмула изобретения

Устройство для деления, содержащее счетчик делимого, регистр остатка делимого, дополнительный регистр, первый и второй сумматоры, схему сравнения, регистр делителя, дешифратор нуля, счетчик результата, первый элемент- ИЛИ, элемент И и вход тактовой частоты устройства, соеди- ненный с первым входом элемента И и счетным входом счетчика делимого, вЫход первого сумматора соединен с- входом дешифратора нуля, выход второго сумматора соединен с информационным входом дополнительного регистра, выход регистра делителя соединен с первым входом схемы сравнения, выход которой соединен с вторым входом элемента И, а выход первого элемента ИЛИ является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр делимого регистр основания системы счисления, сдвигающий регистр, коммутатор, преобразователь кода, второй элемент ИЛИ, первый и второй элементы задержки s элемент НЕ, шина логической единицы и шина управления, которая сое- динена с первым входом второго элемента ИЛИ, входом записи сдвигающего регистра и входом первого элемента

0

5 0 Q 5 -п

5

18

задержки, выход которого соединен с входом управления регистра основания системы счисления и входом элемента НЕ, выход которого соединен с входом управления регистра делимого, выход которого соединен с выходом регистра основания системы счисления и информационным входом счетчика делимого, выход второго элемента ИЛИ соединен с входом записи счетчика делимого, выход импульса обнуления которого соединен с входом сдвига сдвигающего регистра, вторым входом второго элемента ИЛИ, входом записи регистра остатка делимого и входом второго элемента задержки, выход которого соединен с входом обнуления дополнительного регистра, вход записи которого соединен с входом тактовой частоты устройства, а выход дополни- тельного регистра соединен с первым входом первого сумматора и информационным входом регистра остатка делимого, выход которого соединен с вторым входом первого сумматора,третий вход которого соединен с первым разрядным выходом сдвигающего регистра, а выход первого сумматора соединен с первым входом второго сумматора и вторым входом схемы сравнения, выход регистра делителя соединен с информационным входом преобразователя кода, выход которого соединен с вторым входом второго сумматора, а вход управления - с выходом схемы сравнения, шина логической единицы устройства соединена с информационным входом сдвигающего регистра (п+1) разрядных выходов которого соединены соответственно с уп- , равляющими входами коммутатора, а (п+2)-й разрядный выход соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом дешифратора нуля, а выход первого элемента ИЛИ соединен с входом обнуления коммутатора, счетчик ре-. зультата содержит (п+1) счетчиков, счетные входы которых соединены соответственно с (п+1) выходами коммутатора, информационный вход которого соединен с выходом элемента И.

| Устройство для деления | 1977 |

|

SU693372A1 |

| Я | |||

Авторы

Даты

1989-12-30—Публикация

1988-02-18—Подача