Изобретение относится к автоматике и вычислительной технике и может быть использовано в управляющих и вычислительных системах повышенной надежности.

Цель изобретения - расширение области применения, повышение помехозащищенности и быстродействия устройства.

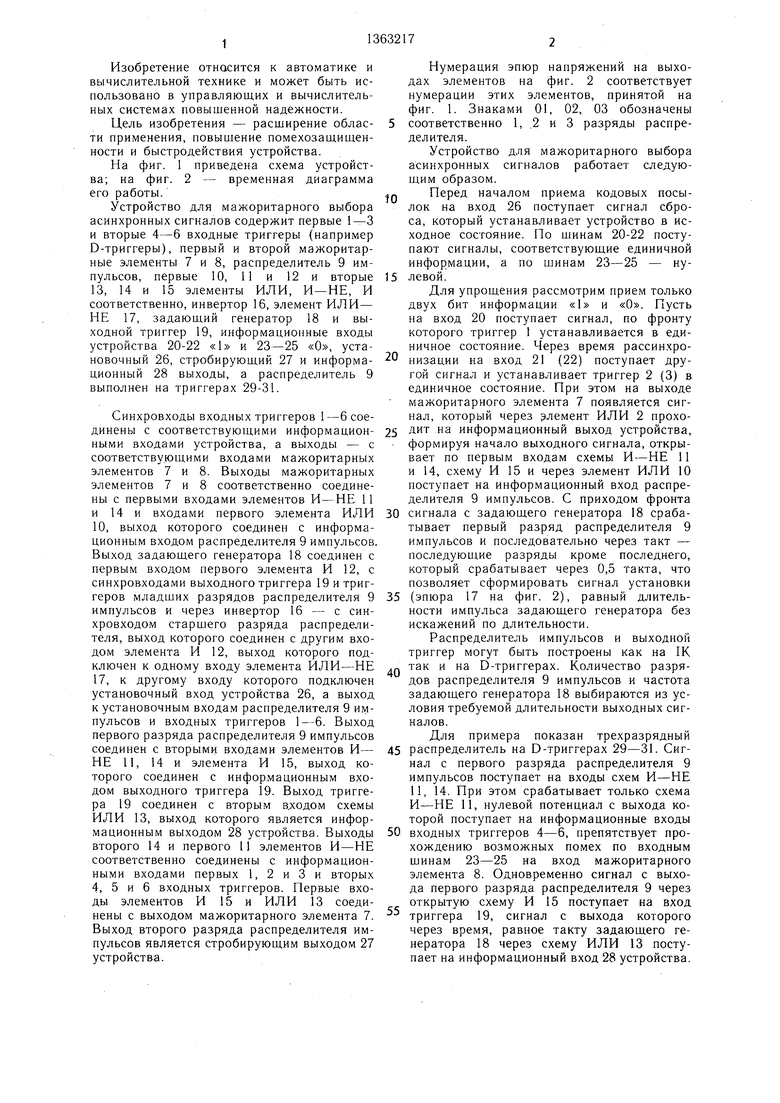

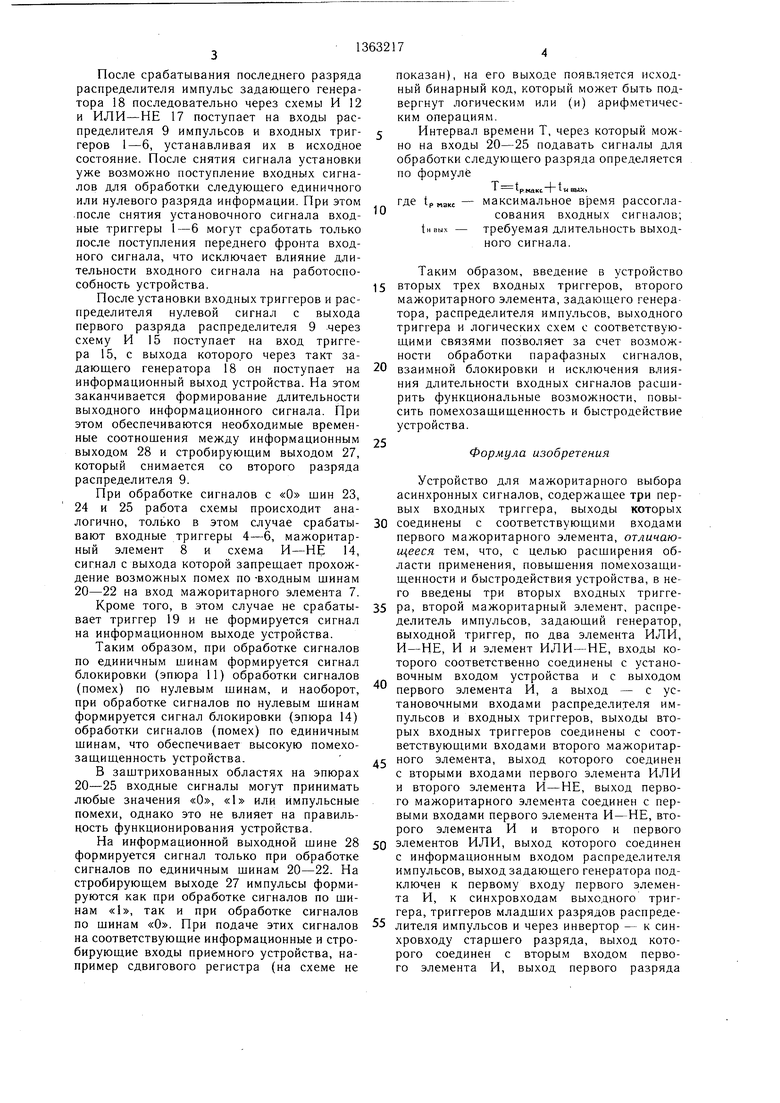

На фиг. 1 приведена схема устройства; на фиг. 2 - временная диаграмма его работы.

Устройство для мажоритарного выбора асинхронных сигналов содержит первые и вторые 4-6 входные триггеры (например D-триггеры), первый и второй мажоритарные элементы 7 и 8, распределитель 9 импульсов, первые 10, 11 и 12 и вторые 13, 14 и 15 элементы ИЛИ, И-НЕ, И соответственно, инвертор 16, элемент ИЛИ- НЕ 17, задающий генератор 18 и выходной триггер 19, информационные входы устройства 20-22 «1 и 23-25 «О, установочный 26, стробирующий 27 и информационный 28 выходы, а распределитель 9 выполнен на триггерах 29-31.

Синхровходы входных триггеров 1-6 соединены с соответствующими информационными входами устройства, а выходы - с соответствующими входами мажоритарных элементов 7 и 8. Выходы мажоритарных элементов 7 и 8 соответственно соединены с первыми входами элементов И-НЕ 11 и 14 и входами первого элемента ИЛИ 10, выход которого соединен с информационным входом распределителя 9 импульсов. Выход задающего генератора 18 соединен с первым входом первого элемента И 12, с синхровходами выходного триггера 19 и триггеров младших разрядов распределителя 9 импульсов и через инвертор 16 - с син- хровходом старшего разряда распределителя, выход которого соединен с другим входом элемента И 12, выход которого подключен к одному входу элемента ИЛИ-НЕ 17, к другому входу которого подключен установочный вход устройства 26, а выход к установочным входам распределителя 9 импульсов и входных триггеров 1-6. Выход первого разряда распределителя 9 импульсов соединен с вторыми входами элементов И- НЕ 11, 14 и элемента И 15, выход которого соединен с информационным входом выходного триггера 19. Выход триггера 19 соединен с вторым влодом схемы ИЛИ 13, выход которого является информационным выходом 28 устройства. Выходы второго 14 и первого 11 элементов И-НЕ соответственно соединены с информационными входами первых 1, 2 и 3 и вторых 4, 5 и 6 входных триггеров. Первые входы элементов И 15 и ИЛИ 13 соединены с выходом мажоритарного элемента 7. Выход второго разряда распределителя импульсов является стробирующим выходом 27 устройства.

Нумерация эпюр напряжений на выходах элементов на фиг. 2 соответствует нумерации этих элементов, принятой на фиг. 1. Знаками 01, 02, 03 обозначены

соответственно 1, .2 и 3 разряды распределителя.

Устройство для мажоритарного выбора асинхронных сигналов работает следующим образом.

Перед началом приема кодовых посылок на вход 26 поступает сигнал сброса, который устанавливает устройство в исходное состояние. По щинам 20-22 поступают сигналы, соответствующие единичной информации, а по щинам 23-25 - ну5 левой.

Для упрощения рассмотрим прием только двух бит информации «1 и «О. Пусть на вход 20 поступает сигнал, по фронту которого триггер 1 устанавливается в единичное состояние. Через время рассинхро0 низации на вход 21 (22) поступает другой сигнал и устанавливает триггер 2 (3) в единичное состояние. При этом на выходе мажоритарного элемента 7 появляется сигнал, который через элемент ИЛИ 2 прохо5 дит на информационный выход устройства, формируя начало выходного сигнала, открывает по первым входам схемы И-НЕ 11 и 14, схему И 15 и через элемент ИЛИ 10 поступает на информационный вход распределителя 9 импульсов. С приходом фронта

0 сигнала с задающего генератора 18 срабатывает первый разряд распределителя 9 импульсов и последовательно через такт - последующие разряды кроме последнего, который срабатывает через 0,5 такта, что позволяет сформировать сигнал установки

5 (эпюра 17 на фиг. 2), равный длительности импульса задающего генератора без искажений по длительности.

Распределитель импульсов и выходной триггер могут быть построены как на IK

„ так и на D-триггерах. Количество разрядов распределителя 9 импульсов и частота задающего генератора 18 выбираются из условия требуемой длительности выходных сигналов.

Для примера показан трехразрядный

5 распределитель на D-триггерах 29-31. Сигнал с первого разряда распределителя 9 импульсов поступает на входы схем И-НЕ 11, 14. При этом срабатывает только схема И-НЕ 11, нулевой потенциал с выхода которой поступает на информационные входы

0 входных триггеров 4-6, препятствует прохождению возможных помех по входным шинам 23-25 на вход мажоритарного элемента 8. Одновременно сигнал с выхода первого разряда распределителя 9 через открытую схему И 15 поступает на вход

триггера 19, сигнал с выхода которого через время, равное такту задающего генератора 18 через схему ИЛИ 13 поступает на информационный вход 28 устройства.

После срабатывания последнего разряда распределителя импульс задающего генератора 18 последовательно через схемы И 12 и ИЛИ-НЕ 17 поступает на входы распределителя 9 импульсов и входных триг- 5 геров 1-6, устанавливая их в исходное состояние. После снятия сигнала установки уже возможно поступление входных сигналов для обработки следующего единичного или нулевого разряда информации. При этом .после снятия установочного сигнала входные триггеры 1-6 могут сработать только после поступления переднего фронта входного сигнала, что исключает влияние длительности входного сигнала на работоспособность устройства.

После установки входных триггеров и распределителя нулевой сигнал с выхода первого разряда распределителя 9 через схему И 15 поступает па вход триггера 15, с выхода которого через такт за10

показан), на его выходе появляется исходный бинарный код, который может быть подвергнут логическим или (и) арифметическим операциям.

Интервал времени Т, через который можно на входы 20-25 подавать сигналы для обработки следующего разряда определяется по формуле

1 1р,щ,кс-)-Тивых,

где (р„акс - максимальное время рассогласования входных сигналов; 1нвых - требуемая длительность выходного сигнала.

15

Таким образом, введение в устройство вторых трех входных триггеров, второго мажоритарного элемента, задающего генератора, распределителя импульсов, выходного триггера и логических схем с соответствующими связями позволяет за счет возможности обработки парафазных сигналов,

дающего генератора 18 он поступает на 20 взаимной блокировки и исключения влия- информационный выход устройства. На этомния длительности входных сигналов расшизаканчивается формирование длительностирить функциональные возможности, повывыходного информационного сигнала. Присить помехозащищенность и быстродействие

этом обеспечиваются необходимые времен-устройства,

ные соотнощения между информационным 25 выходом 28 и стробирующим выходом 27,

Формула изобретения

который снимается со второго разряда распределителя 9.

При обработке сигналов с «О щин 23, 24 и 25 работа схемы происходит анаУстройство для мажоритарного выбора асинхронных сигналов, содержащее три первых входных триггера, выходы которых

логично, только в этом случае срабаты- 30 соединены с соответствующими входами

вают входные триггеры 4-6, мажоритарный элемент 8 и схема И-НЕ 14, сигнал с выхода которой запрещает прохождение возможных помех по -входным щинам 20-22 на вход мажоритарного элемента 7.

первого мажоритарного элемента, отличающееся тем, что, с целью расщирения области применения, повыщения помехозащищенности и быстродействия устройства, в него введены три вторых входных триггеКроме того, в этом случае не срабаты- 35 ра. второй мажоритарный элемент, распревает триггер 19 и не формируется сигнал на информационном выходе устройства.

Таким образом, при обработке сигналов по единичным шинам формируется сигнал блокировки (эпюра 11) обработки сигналов (помех) по нулевым щинам, и наоборот, при обработке сигналов по нулевым щинам формируется сигнал блокировки (эпюра 14) обработки сигналов (помех) по единичным шинам, что обеспечивает высокую помехозащищенность устройства.

В заштрихованных областях на эпюрах 20-25 входные сигналы могут принимать любые значения «О, «1 или импульсные помехи, однако это не влияет на правильность функционирования устройства.

40

делитель импульсов, задающий генератор, выходной триггер, по два элемента ИЛИ, И-НЕ, И и элемент ИЛИ-НЕ, входы которого соответственно соединены с установочным входом устройства и с выходом первого элемента И, а выход - с установочными входами распределителя импульсов и входных триггеров, выходы вторых входных триггеров соединены с соответствующими входами второго .мажоритар- д5 ного элемента, выход которого соединен с вторыми входами первого элемента ИЛИ и второго элемента И-НЕ, выход первого мажоритарного элемента соединен с первыми входами первого элемента И-НЕ, второго элемента И и второго и первого

На информационной выходной щине 28 50 элементов ИЛИ, выход которого соединен формируется сигнал только при обработкес информационным входом распределителя

сигналов по единичным щинам 20-22. На стробирующем выходе 27 импульсы формируются как при обработке сигналов по щинам «1, так и при обработке сигналов по щинам «О. При подаче этих сигналов 55 на соответствующие информационные и стро- бирующие входы приемного устройства, например сдвигового регистра (на схеме не

импульсов, выход задающего генератора подключен к первому входу первого элемента И, к синхровходам выходного триггера, триггеров младших разрядов распределителя импульсов и через инвертор - к син- хровходу старщего разряда, выход которого соединен с вторым входом первого элемента И, выход первого разряда

показан), на его выходе появляется исходный бинарный код, который может быть подвергнут логическим или (и) арифметическим операциям.

Интервал времени Т, через который можно на входы 20-25 подавать сигналы для обработки следующего разряда определяется по формуле

1 1р,щ,кс-)-Тивых,

где (р„акс - максимальное время рассогласования входных сигналов; 1нвых - требуемая длительность выходного сигнала.

Формула изобретения

Устройство для мажоритарного выбора асинхронных сигналов, содержащее три первых входных триггера, выходы которых

первого мажоритарного элемента, отличающееся тем, что, с целью расщирения области применения, повыщения помехозащищенности и быстродействия устройства, в него введены три вторых входных тригге ра. второй мажоритарный элемент, распре

делитель импульсов, задающий генератор, выходной триггер, по два элемента ИЛИ, И-НЕ, И и элемент ИЛИ-НЕ, входы которого соответственно соединены с установочным входом устройства и с выходом первого элемента И, а выход - с установочными входами распределителя импульсов и входных триггеров, выходы вторых входных триггеров соединены с соответствующими входами второго .мажоритар- ного элемента, выход которого соединен с вторыми входами первого элемента ИЛИ и второго элемента И-НЕ, выход первого мажоритарного элемента соединен с первыми входами первого элемента И-НЕ, второго элемента И и второго и первого

элементов ИЛИ, выход которого соединен с информационным входом распределителя

импульсов, выход задающего генератора подключен к первому входу первого элемента И, к синхровходам выходного триггера, триггеров младших разрядов распределителя импульсов и через инвертор - к син- хровходу старщего разряда, выход которого соединен с вторым входом первого элемента И, выход первого разряда

распределителя импульсов соединен с вторыми входами элементов И-НЕ и второго элемента И, .выход которого подключен к информационному входу выходного триггера, а его выход - к второму входу второго элемента ИЛИ, выходы второго и первого элементов И-НЕ соответственно соединены с информационными входами первых

и вторых входных триггеров, синхровходы которых соединены с соответствующими единичными и нулевыми информационными входами устройства, выходы второго элемента ИЛИ и второго разряда распределителя импульсов соответственно соединены с информационным и стробирующим выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора асинхронных сигналов | 1988 |

|

SU1554153A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1580383A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Многоканальное устройство для тестового контроля группы цифровых блоков | 1984 |

|

SU1238084A1 |

| Устройство для сопряжения | 1983 |

|

SU1156083A1 |

| Устройство микропрограммного управления с контролем | 1990 |

|

SU1805466A1 |

| Многоканальное устройство синхронизации | 1988 |

|

SU1642473A1 |

| Распределитель импульсов с обнаружением ошибок | 1980 |

|

SU955074A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в управляющих и вычислительных системах. Целью изобретения яв0м 7 ляется расширение функциональных возможностей, повышение помехозащищенности и быстродействия устройства за счет обработки парафазных сигналов, взаимной блокировки прохождения возможных помех при обработке единичных и нулевых сигналов и исключения влияния длительности входных сигналов. Устройство содержит входные триггеры 1-6, мажоритарные элементы 7-8, распределитель импульсов 9, элементы ИЛИ, И-НЕ и И 10-15, инвертор 16, элемент ИЛИ-НЕ, задающий генератор 18 и выходной триггер 19. В устройстве максимальное время рассогласования входных сигналов не зависит от длительности входных сигналов, за счет чего и повышается быстродействие устройства. 2 ил. 26 о ш (Л со С5 OJ ьо

| Устройство для мажоритарного выбора асинхронных сигналов | 1982 |

|

SU1062707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1983 |

|

SU1160419A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-28—Подача