Изобретение относится к автоматй ке и вычислительной технике и может быть использовано в качестве устройства для тестового контроля дискретных блоков и выбора работоспособной конфигурации цифровых систем повышенной надежностио ,

Целью изобретения является повышение достоверности контроля.

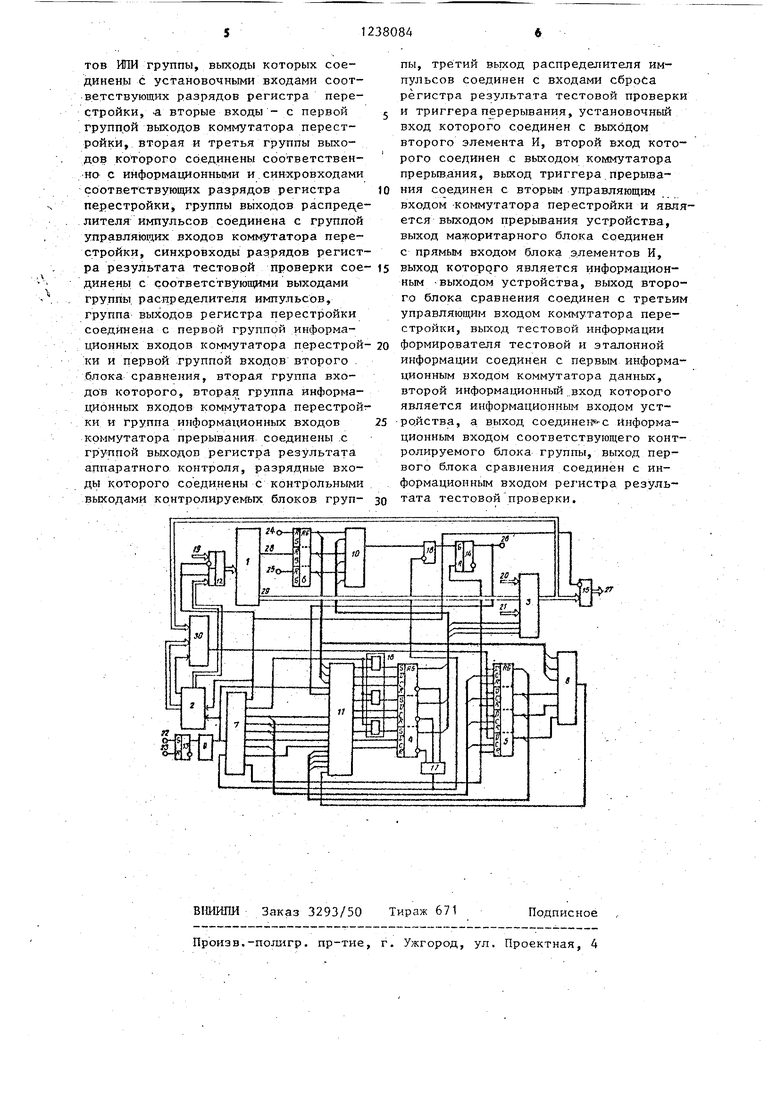

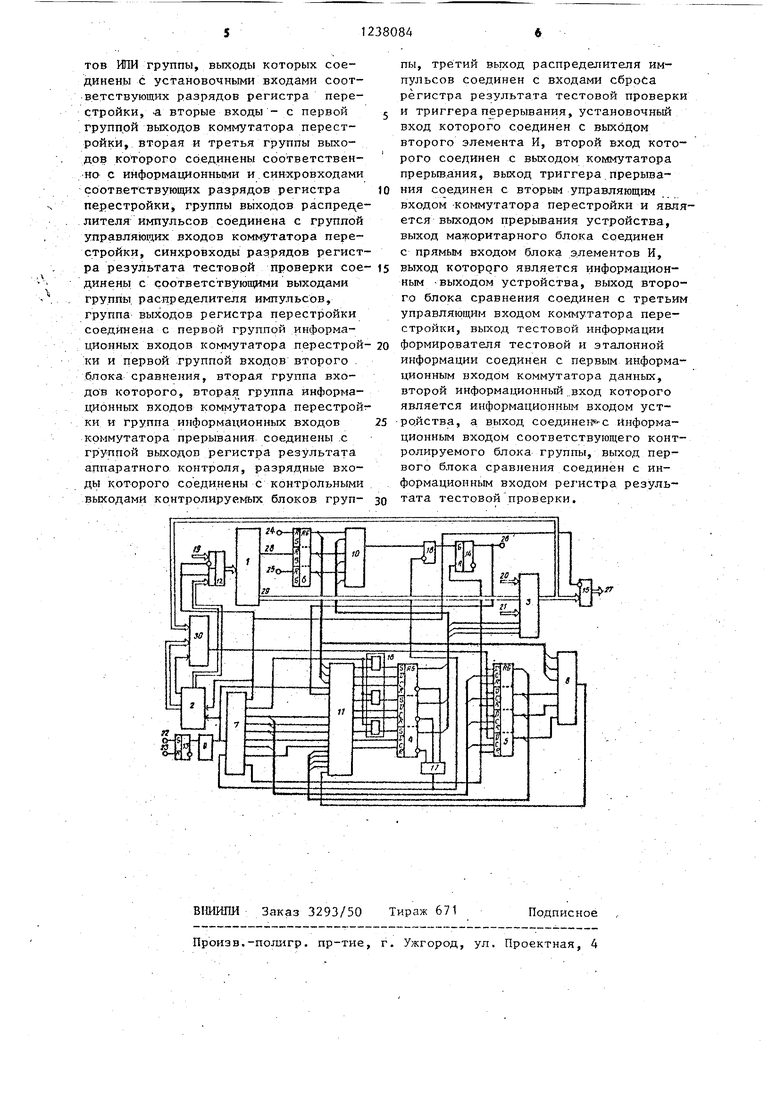

На чертеже приведена функциональная схема устройства.

Функциональная схема устройства срдержит контролируемьй блок 1, формирователь 2 тестовой и эталонной информации, мажоритарньй блок 3, регистр 4 перестр.ойки, регистр 5 результата тестовой проверки и регистр 6 результата аппаратного контроля, распределитель 7 импульсов, второй блок 8 сравнения, генератор 9 импульсов, коммутаторы прерывания 10, перестройки 11 и данных 12, триггеры управления 13 и прерывания 14, блок 15 элементов И, группу элементов ИЛИ 16, первый 17 и второй 18 элементы И, информационный вход 19, пер- вьй 20 и второй 21 информационные входы соседних каналов, входы пуска 22 и останова 23, первьй 24 и второй 25 входы аппаратного контроля, выход 26 прерывания и информационный выход 27 устройства, контрольный выход 28 и информационньй выход 29 контролируемого блока 1, первый блок 30 сравнения,

Устройство функционирует в трех основных режимах:- рабочем режиме (основное функцион фопание), режиме тестового контроля, режиме выбора работоспособной конфигурации.

Б исходном состоянии все триггеры регистров 6 и 4, а также последний разряд распределителя 7 импульсов находятся в единичном состоянии, все остальные элементы памяти обнулены. Ра:бочий режим. По приходу на вход

.23 устройства команды Пуск триггер 13 устанавливается в 1 и разрешает работу генератора 9 импульсов. Импульсы проходят на вход рдспределите.ля 7 и осуществляют сдвиг единичного сигнала в распределителе 7. При этом информация с выхода 29 блока 1 и входов 20 и 21 устройства поступает в блок 3, где мажоритируется, поскольку регистр 4 находится в единичном состоянии. С выхода блока 3 информация через открытый блок 15

элементов И поступает на-выход 27 устройства. На вход контролируемого блока 1 информация проходит через коммутатор 12 данных с входа 19 уст-

ройства,

При появлении сигнала ненормы по одному из входов аппаратурного контроля 24 и 25 или выходу 28 обнуляется соответствующий разряд регистра

6, появляется сигнал прерьгоания, который .через элемент И 18 записьгоает- ся в триггер 14, С выхода триггера 14 этот с.игнал вьздается на выход 26 прерьюания устройства и поступает в

коммутатор 11 перестройки, Очередньм тактовым импульсом, проходящим через коммутатор 11, в регистр 4 перестройки заносится код, содержащийся в регистре 6.

При записи нуля в любой из разрядов регистра 4 мажоритарная конфигурация системы Сохраняется и устройство продолжает работать в этом режиме аналогично описанному до тех

пор, пока не изменится содержимое регистра 6, при этом код из регистра 6 перепишется в регистр 4 и устройство перестроит систему в соответствующую конфигурацию (устройство продол.жает работу в этом режиме), или появится сигнал на Лервом выходе рас- пределителя 7 импульсов. По этому сигналу устройство переходит в режим контроля,

Режим тестового контроля. При появлении сигнала на первом выходе распределителя 7 импульсов коммутатор 12 настраивается на передачу информа тдии с выхода формирователя 2, бло

кируется выдача информации через

блок 15 элементов И на выход 27 устройства, включается формирователь 2,

Очередным сигналом с второго вы- . хода распределителя 7 импульсов в

регистр 4 через элементы ИЛИ 16 записывается код 111 и начинается проверка системы в мажоритарной конфигурации « При этом тесты с выхода формиро - вателя 2 подаются на контролируемьй

блок, а реакция с выхода блока 3 поступает на информационный вход блока 30 сравнения. .

Затем сигналом с выхода распределителя 7 в соответствуюищй разряд регистра 5 заносится результат проверки, в регистр 4 записывается код конфигурации с перестройкой на другой канал и начинается проверка сиетемы в данной конфигурации. Запись езультата тестового контроля произ- одится по сигналу с выхода распре - елителя 7 импульсов.

Проверка системы в двух других од- j ноканальных конфигурациях осуществляется по описанному алгоритму. После записи- резуль атов контроля устройство переходит в режим выбора работоспособности конфигурации.

Режим выбора работоспособной конигурации. По тактовому импульсу с выхода распредепителя 7 в регистр 4 заносится код конфигурации системы, который зависит от .результатов ап- .fs паратного и тестового контроля, наичия сигнала прерывания

Возможны следующие варианты выбоа конфигурациио .

АО Если ранее был сформирован сиг- 20 нал прерьшания, цо результатам тестоого контроля система нормально функционировала в мажоритарной конфигурации и результаты тестового и ап- паратного контроля совпадают, то в 25 регистр 4 перестройки заносится код 000 аварийной мажоритарной конфигурации,

В этом случае появляется единичный сигнал на выходе элемента И 17, кото д ый блокирует работу аппаратных и тестовых средств проверки, запрещает . вьщачу сигналов распределителя 7. Вследствие этого триггер 14 прерывания остается в единичном состоянии.

Б. Если ранее не был сформирован сигнал прерывания, а сигналы с выходов регистра 5 и блока 8 равны 1, то в регистр 4 заносится код 111 мажоритарной конфигурации. Тогда сигнал на выходе элемента И 17 остается равным О и следующим импульсом с выхода распределителя 7 произойдет обнуление триггера 14 и регистра 5. Затем устройство перейдет в рабочий режим функционирования.

В, Если результаты аппаратного и тестового контроля не совпадают, т.е. сигнал с выхода блока 8 равен О, или, если он равен 1, а сиг- 50 нал с выхода регистра 5 равен О, то в регистр 4 заносится код конфигурации, который получается путем поразрядной коньюнкции кодов, записанных в регистрах 6 и 5. В зависи- 55 мости от результата операции коньюнкции устройство далее работает так, как описано для случая А.

35

40

45

- j

.fs

- 20 25

й д .

50 5535

40

45

Фо рмул аизо б р е т е н ия

Многоканальное устройство для тестового контроля группы цифровых блоков, содержащее в каждом канале формирователь тестовой и эталонной информации, мажоритарный блок, регистр перестройки, регистр результа- - та тестовой.проверки, первый и второй блоки сравнения, генератор импульсов, два элемента И,, коммутатор прерьшания, причем выход генератора импульсов соединен с первым синхро- входом формирова.тедя тестовой и эта- лонной информации, информационные входы мажоритарного блока соединены с информационными выходами контролируемых блоков группы, вькод мажоритарного блока соединён с первым информационным входом первого блока сравнения, второй информационный вход и синхровход которого соединены с : ; выходом эталонной информации и синх- ровходом формирователя тестовой и эталонной информации, группа прямых разрядных выходов регистра перестройки соединена с группой разрешающих входов мажоритарного блока и группой управляющих входоэ коммутатора пре- рывания, выход nejjBoro элемента И соединен с инверсным входом второго элемента И, отличающееся тем, что, с цепью повышения достоверности контроля, в каждьй канал введены регистр результата аппаратного контроля, распределитель импульсов, коммутатор перестройки, коммутатор данных, триггер управления, триггер прерывания, блок элементов И, группа, элементов ШШ, причем входы пуска и останова устройства соединены соответственно с единичным и нулевым входами триггера управления, выход которого соединен с входом генератора импульсов, выход которого соединен с первым управляющим входом коммутатора перестройки и синхровходом распределителя импульсов, первый выход которого соединен с вторым синхровходом формирователя тестовой и эталонной информации, управляющим входом коммутатора данных и инверсным входом блока элементов И, группа инверсных выходов регистра перестройки соединена с группой входов первого элемента И, выход которого соединен с разрешающим входом распределителя импульсов, второй выход которого соединен с первыми входами элемен-

тов ИПИ группы, выходы которых соединены с установочными входами соответствующих разрядов регистра перестройки, .а вторые входы с первой группой выходов коммутатора перестройки, вторая и третья группы выходов которого соединены соответственно с информационными и.синхровходами соответствующих разрядов регистра перестройки, группы выходов распределителя импульсов соединена с группой управляющих входов коммутатора перестройки, синхровходы разрядов регистра результата тестовой проверки соединены с соответствующими выходами группы, распределителя импульсов, группа выходов регистра перестройки соединена с первой группой информационных входов коммутатора перестрой :ки и первой группой входов второго . блока сравнения, вторая группа входов которого, вторая группа информационных входов коммутатора перестроит ки и Группа информационных входов коммутатора прерывания соединены .с группой выходов регистра результата аппаратного контроля, разрядные входы которого соединены с контрольнь ми выходами контролируе1. блоков груп-

пы, третий вькод распределителя импульсов соединен с входами сброса регистра результата тестовой проверки 5 и триггера перерывания, установочньй вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом коммутатора прерьш.ания, выход триггера, прерыва10 ния соединен с вторым управляющим

входом -коммутатора перестройки и является выходом прерьшания устройства, выход мажоритарного блока соединен с прямым входом блока элементов И,

15 выход которого является информационным -выходом устройства, выход второго блока сравнения соединен с третьим управляющим входом коммутатора перестройки, выход тестовой информации 20 формирователя тестовой и эталонной

информации соединен с первым информационным входом коммутатора данных, второй информационный.вход которого является информационным входом уст25 -ро.йства, а. выход соединеннее Информационным входом соответствующего контролируемого блока группы, выход первого блока сравнения соединен с информационным входом рет истра резуль30 тата тестовой проверки.

1 {)

Zjj.

-ГГ7Г-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Устройство контроля и управления реконфигурацией | 1984 |

|

SU1213554A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Многоканальное устройство для обмена данными микропроцессорной системы | 1985 |

|

SU1264193A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Устройство для управления переключением резервных блоков | 1989 |

|

SU1635186A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в качестве устройства контроля и выбора работоспособной конфигурации цифровых систем повьшгенной надежности. Целью изобретения является повышение достоверности контроля. Устройство со- держит формирователь тестовой и эталонной информации, мажоритарный блок, регистр перестройки, регистр результата тестовой проверки, регистр результата аппар атного контроля, распределитель импульсов, два блока. сравнения, генератор импульсов, коммутаторы прерывания перестройки и данных, элементы И, ИЛИ, выходные сигналы контролируемых блоков поступают в мажоритарньй блок, с выхода которого - на первый блок сравнения, где сравниваются с эталонной информацией. Выходной сигнал блока сравнения записывается в регистр результата тестовой проверки, выход которого управляет коммутатором перестройки „ 1 ил.... о ф ел

| 1972 |

|

SU411455A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления реконфигурацией резервированной системы | 1982 |

|

SU1040632A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-09-17—Подача