ьатора соединен с первым входом третьего Апсмента И, второй и третий входы которого соединены соответственно с прямыми выходами первого и второго триггеров, нулевые входы которых соединены с четвертым выходом дешифратора и первым входом четвертого элемента И выход которого соединен с нулевым входом третьего триггера, инверсный выход которого соединен с . установочным входом . счетчика, группа выходов которого соединена соответственно с входами дешифратора, счет ный вход счетчика соединен с выходом пято О .элемента И, первый вхоД которого сое хинен с прямым выходом третьего триггера.

единичный вход которого является управляю щим входом узла управления, синхровходкоторого соединен с вторым входомпятого элемента И и вторым входом четвертого элемента И, прямой и инверсный выходы знакового разряда сумматора соединены с втоРЫ.МИ входами соответственно первого и второго элементов И, выход элемента ИЛИ соединен с входом переноса младшего разряда сумматора, выходы второго регистра соединены, соответственно с вторыми входами элементов ИЛИ группы, выход третьего элемента И является, выходом узла управления, выход первого элемента И соединен с единичным входом второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1291953A1 |

| Устройство для синхронизации вычислительной системы | 1986 |

|

SU1363172A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1149235A1 |

| Устройство для синхронизации вычислительной системы | 1987 |

|

SU1495773A1 |

| Устройство для синхронизации вычислительной системы | 1988 |

|

SU1529205A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1226428A1 |

| Устройство для синхронизации вычислительной системы | 1990 |

|

SU1765812A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее задающий генератор, блок выра ботки синхросигналов, который содержит счетчик, регистр, два элемента И, два триггера, узеЛ сравнения, узел управления, де; шифратор, две группы элементов И, причем синхровход узла управления соединен со счетным входом счетчика, выходы которого соединены с первой групг1ой входов узла сравнения, с входами дешифратора, выходы которого соединены соответственно с первыми входами элементов И первой группы, вы,ходы элементов И с первого по (п-1)-.й (где п - число выходов устройства) первой группы являются выходами с первого по (п-1)-й устройства, группа прямых выходов регистра соединена соатветственно с рторой группой входов узла сравнения, пря)йой выйод первого триггера соединен с первым входом первого элемента И, причем узел управления содержит первый элемент И, отличающееся тем, что, с целью увеличения точности синхронизации, в блок выработки синхросигналов введены два элемента ИЛИ, причем выход задающего генератора соединен со счетным входом счетчика, установочный вход счетчика соединен с выходом перво го элемента ИЛИ, первый вход которого соединен с п-ым выходом дешифратора, с первым входом второго элемента И, выход которого соединен с единичным входом первого триггера, нулевой вход которого соединен .р Бторым входом первого элемента ИЛИ {тервым уходом второго элемента ИЛИ, установоч11ым входом регистра и выходом вого ьлемента И, второй вход которого coei динен с выходом узла сравнения, группа инверсных выходов регистра соединена с группой информационных входов узла упрабления, выход которого соединен с единичным входом второго триггера, нулевой йход котсфого соединен с прямым выходом, первого триггера, инверсный выход которого соединен с вторыми входами элементов И с первого по (п-1)-й первой группы элементов И, выход первого элемента И первой группы соединен с управляющим входом узла управления, выход ri-ro элемента И первой группы соединен с вторым входом второго элемента ИЛИ, выход которого является п-м выходом устройства, стробирующий. вход которого соединен с первыми входами элементов И второй группы, вторые входы W которых соединены соответственно с выходами счетчика, выходы элементов И второй группы соединены с единичными входами регистра, инверсный выход второго триггера соединен с вторым входом п-го элемента И . первой группы, прямой выход второго триггера соединен с вторым входом второго элемента И, причем в узел управления введены сумматор, два регистра, группа элементов Од ИЛИ, элемент ИЛИ| счетчик, дешифратор, 00 второй, третий, четвертыйи пятый элемен :о ты И, три триггера, причем группа информаIN9 ционных входов узла управления соединена |С первой группой информационных входов сумматора, вторая группа информационных входов которого соединена с выходами эле ментов ИЛИ группы, первые входы которых соединены соответственно с выходами первого регистра, управляющий вход которого соединен с первым выходом дешифратора, первым входом первого элемента И, с первым входом элемента ИЛИ, второй вход которого соединен с вторым выходом дешифратора, с управляющим входом второго ре.гистра и первым входом второго элемента Н, выход которого соединен с единичным входом первого триггера, третий выход дешиф

1- .

Изобретение относится к вычислительной технике и может быть спользовано при построении вычислительных систем на базе нескольких -однотипных цифровых вычислительных машин.

Известно устройство для синхронизации вычислительной системы, содержащее генератор тактовых импульсов, распределитель тактовых импульсов по числу процессоров в системе, блоки управления и первые элененты -И по числу управляемых процессоров в. системе, причем выход генератора Тактовых импульсов соединен с входом распределителя импульсов управляющего процессора и с первыми входами первых элементов И, выходы которых соединень с входами распределителей импульсов управляемых процессоров, группы входов блоков управления- соединены с группой выходов соответствуюиХего. распределителя импульсов, первые входы распределителей импульсов управляемых процессоров соединены с выходами соответствующего элемента И 1.

Недостатком устройства является большой объем оборудования, а также низкая надежность, обусловленная наличием «го.i«OK в логических цепях, которыеприводят к. уменьшению длительности отдельных так,ТдвЫх. импульсов и к появлению ложных импульсов.

Наиболее близким по технической сущности к предлагаемому является устройство для синхронизации вычислительной системы, содержащее задающий геиер1атор, две .группы элементов задержки, блок переключателей, блок выработки сигналов начальной установки, блок формирования сигналов управления режимами, блок управления, группу блоков выработки- синхросигналов, каждый из которых содержит счетчик, эле мент НЕ, два регистра сдрига, шесть триг frepoB, селектор, узел дент фрации и сравне;нйя логического состояния, узел удравле- ния, дешифратор, две группь элементов И, ;два элемента И, причем группа выходов за,|р,ающего генератора соединена с входами, с

Первого по п-й (где п - число каналов) элементов задержки первой группы, входы с (п + 1)-го по-2п-й элем-ентов задержки первой группы соединены соответственно с выходами блока выработки сигналов начальной

установки, вход KOtoporo соединен с дополнительным выходом задающего генератора, группа выходов блока переключателей соединена соответственно с входами блока формирования сигналов управления режимами, выходы элементов задержки с первого по

п-й соединены соответственно в каждом бло.ке выработки синхросигналов с сияхровходом счетчика, с синхровходом первого регистра сдвига, с сийхровходом второго регист-. ра сдвига, с синхровходом первого триггера, ,с синхровходом второго триггера, с синхрозходом узла управления, с первыМи входа- -«и элементов И первой группы, с первыми

рходами элементов И второй группы каждого .блока выработки сийхросигналов, вход

элемента НЕ каждого блока выработки

:инхросиг налов соединен с выходом соот- ретствУющего элемента задержки с- (п+1)го по 2п-й первой группы, выход элемента НЕ соединен свходом сброса счетчика каждого блока выработки, синхросигналов и в каждом блоке выработки синхросигналов

выходы счетчика соединены соответственно

/с входами дещифратора, с входами селекстора и с первой группой входоё узла дешиф-;

рации и сравнения логического состояния,

вторые выходы которых с( шинёнЫ cooTseTcf

енно с выходами первого регистра сдвига,

-информационный вход которого соединей с «нверсным выходом второго разряда счет ика, управляющий вход первого регистра Сдвига соединен с выходом узла управления Мс йторыми входами элементов И второй группы, первый выход дешифратора соединен с вторым входом первого члемента И первой группы н с третьим входом первого элемента И второй группы, второй выход дешифратора соединен с вторым входом вто-рого элемента И первой группы и с третьим входом второго элемента И второй группы, третий выход дешифратора соединен с вторьп,1 входом третьего элемента И первой группы и с третьим входом третьего элемен-. та И второй группы, четвертый выход де :шифратора соединен с вторым входом четвертого элемента И первой группы и с тре:Тьим входом четвертого элемента И BTOpofr группы, с управляющими входами перуправляю-. вого и второго триггеров и с щим входом второго регистра сдвига,прямой и инверсный выходы селектора сое динены соответственно свторыми входами. пятого н шестого элементов И первой группы выход узла дешифрации и сравнения логи- ческого состояния соединен с первым информационным входом узла управления, второй информационный вход которого соединен с вь1ходом первого триггера, выход второго триггера соединен с третьим информационным входом узла управления, четвертый информационный вход которого соединен с прямым выходом первого разряда второго регистра сдвига, инверсный выход второго разряда второго регистра сдвига соединен с пятым информационным входом узла ;управления, выходы блока формирования сигналов управления режимами соединен соответственно с информационными входами первого триггера, второго триггера, второго |регистра сдвига блоков выработки синхроi сигналов управления режимами соединены Зторой групп блоков выработки сиихросигРиалов соединены соответственно с входами, элементов задержки второй группы, выходы которых являются выходами устройства 2. В известном устройстве синхронизируют-, ся только тактовые импульсы ЦВМ вычисли-: тельной системы. Для повышения точности выполнения управляемых задач необходимо все ЦВМ вы числительной системы синхронизировать с сигналами точного времени общей системы; отсчета. Цель изобретения - увеличение точноети синхронизации вычислительной системы. . Поставленная цель достигается тем, что в устройстве для синхронизации вычисли /тельной системы, содержащем задающий генератор, блок выработки сиихросигнаЛов.я . который содержит счетчик, регистр, два , элемента И, два триггера, узел сравнений; .узел управления, дешифратор, две группы. /элементов И, причем синхровход узла управления соединен со счетным входом счетчика, выходы которого соединены с первой группой входов узла сравнения, с входами дешифратора, выходы которого соединены соответственно с первыми входами элементов И первой группы, выходы элементов И с первого по (п-1)-й (где п - число выходов устройства) первой группы являются выходами с первого по (п-1)-й устройства/, группа прямых выходов регистра соединена соответственно с второй группой Входбй узла сравнения, прямой выход первого триггера соединен с первым входом первого элемента И, причем узел управления содержит первый элемент И, в блок выработки синхросигналов введены два элемента ИЛИ, при-, чем выход задающего генератора соединенсо счетным входом счетчика, установочный вход счетчика соединен с выходом п ервого элемента ИЛИ, первый вход которого соединен с п-м выходом дешифратора, с первымвходом второго элемента И, выход которого: соединен с единичным входом первого триг-, гера, нулевой вход которого соединен с вто-i рым входом первого элемента ИЛИ, с пер-: ВЫЛ входим второго элемента ИЛИ, с устано вочным входом регистра и с выходом первого; элемента И, второй вход которого соединен с -.ыходом узла сравнения, группа инверсных выходов регистра соединена с группой информационных входов узла управления, выход которого соединен с единичным входом второго триггера, нулевой вход которого соединен с прямым -выходом первого триггера, инверсный выход которого соединен с вторыми входами элементов И с первого по (п-1)-й первой группы элементов И, выход первого элемента И первой группы; соединен с управляющим входом узла управления, выход п-го элемента И первой группы соединен с в.орым входом второго элемента ИЛИ, выход которого является п-м .выходом устройства, стробирующий вход; которого соединен с первыми вхо.т.ами элементов И второй группы, вторые входыу которых соединены соответственно с выходами счетчика, выходы элементов И второй группы соединены с единичными входами регистра, инверсный выход второго триггера соединен с вторым входом п-го элемента И первой , прямой выход второго триггера соединен с вторым входом второго элемента И, причем в узел управления введены сумматор, два регистра, группа элементов ИЛИ, элемент ИЛИ, счетчик, дешифратор, второй, третий, четвертый и пятый эдемситы И, три триггера, причем группа информационных входов узла управления соединена с первой группой инфо.рмационных входов сумматора, вторая группа информационных входов которого соединена с выходами элементов ИЛИ группы, первые входь которых соединены соответственно с вы-; ходами первого регистра, управляющий вход которого соединен с .первым выходом .дешифратора, с первым входом первого эле йента И, с первым входом э-пемеита ИЛИ, второй вход которого, соединен с вторым выходом дешифратора; с управляющим вхоlOM второго регистра и с первым входов второго элемента И, выход которого соедирен с единичным входом первого триггера, третий выход дешифратора соединен с первым входом третьего элемента И, второй и третий входы которого соединены соответственно с прямыми выходами первого и второгр триггеров, нулевые входы Которых соединены с четвертым .выходом дешифраго|за и с первым входол четвертого элемента И выход которого соединен с нулевым входом третьего триггера, инверсный выход которого соединен с установочным входом счетчика, группа выходов которого соединена соответственно с входами дешифратора, счетный вход счетчика соединен с выходом пятого элемента И, первый вход которого соеди|нен с прямым выходом, третьего .триггера, единичный вход которого является управляющим входом узла управления, синхровход которого соединен с вторым входом пятого элемента И и с вторым аходом четвертого элемента И, прямой и инверсный выходы знакового разряда сумматора соединены с вторыми входами соответственно первого и второго элементов И, выход элемента ИЛИ соединен с входом переноса младшего, разряда сумматора, выходы второгорегистра соединены соответственно с вторыми входа ми элементов ИЛИ группы, выход третьего :элeмe lтa И является выходом узла управления, выход первого элемента И соединен с единичным входом второго триггера.

Это обеспечивает синхронизацию вычислительной системы с сигналами точного времени общей системы отсчета.

При этом производится надежная синхронизация вычислительной системы при разовом появлении сигнала точного времени путем запоминания величины несинхронноеitt на специальном регистре до момента санкционированной синхронизации.

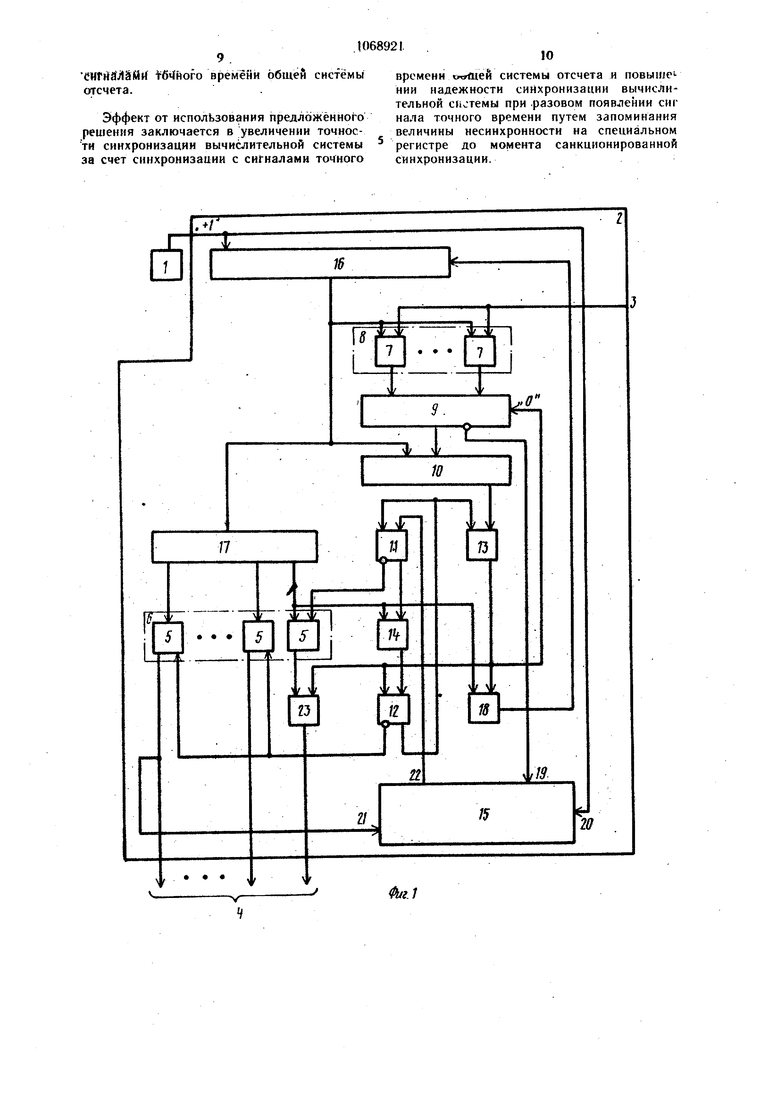

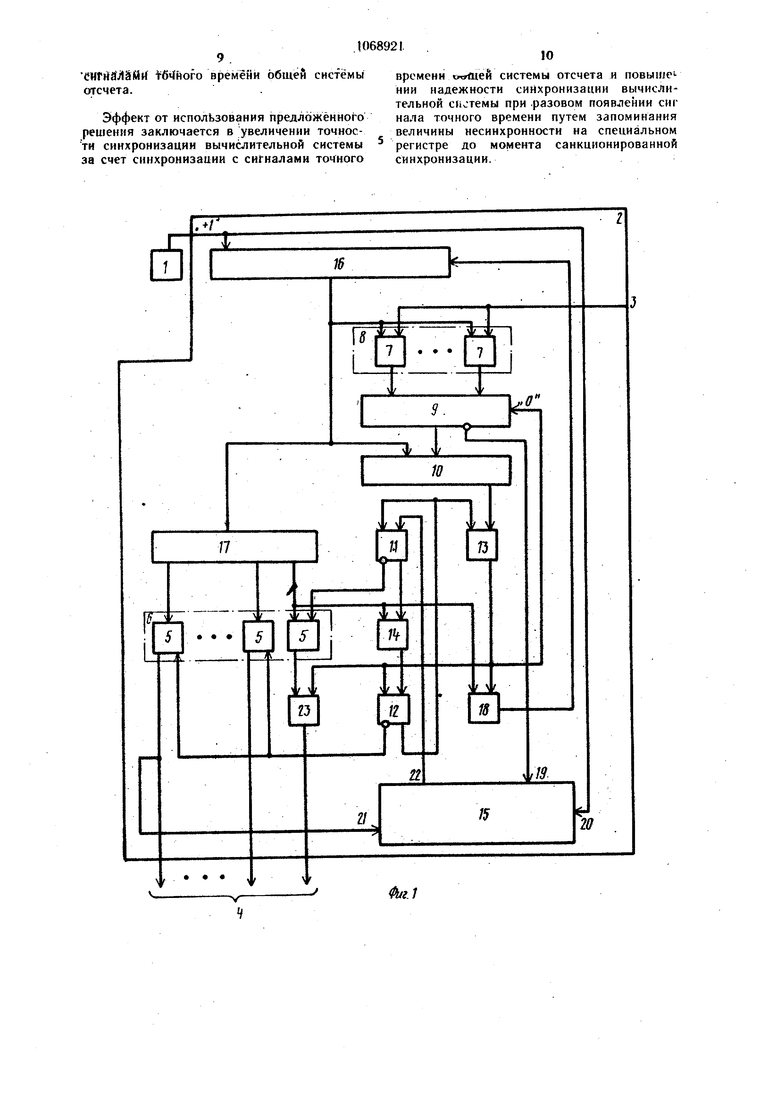

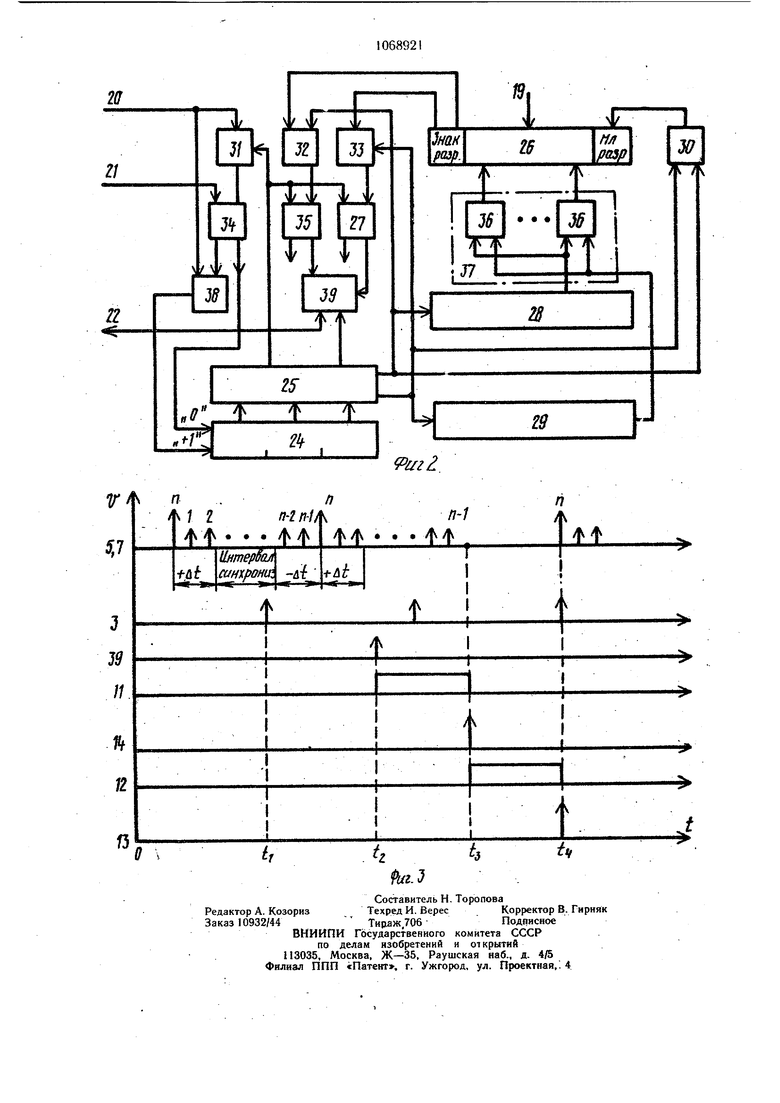

На фиг. 1 приведена схема.предлагаемого устройства; на фиг. 2 - схема узла управления; на фиг. 3- временная диаграм; ма работы устройства.

Устройство содержит задающий генерагтор I, блок 2 вУработки синхросигналов, стробирующий вход 3 устройства и выходь1 4 устройства.

, Влок 2 выработки синхросигналов содержит элементы И 5 первой группы б, элементы И 7 второй группы 8, регистр 9, узел 10 .сравнения, триггеры 11 и 12, элементы И 13 :И 14, узел 15 управления, счетчик 16, дешифратор 17, элемент ИЛИ 18, группу 19 1нформационных входов узла 15 yпpaвлeнияJg синхровход 20 узла 15 управления, управляю.ший вход 21 узла 15 управления, выход 22 .узла 15 управления и элемент ИЛИ 23. Узел 15 управления содержит счетчик 24, дешифратор 25, сумматор 26, триггер 27, регистры 28 и 29, элемент ИЛИ 30, элеменJbi И 31-33, триггеры 34 и 35, элементы }ИЛИ 36 группы 37 и элементы И 38 и 39.

Устройство Ьинхрояизирует каждунз ЦВМ вычислительной системы с сигна,пами; точного времени, поступающими по строби-рующему входу 3 с точностью п±Д..е. в узле 15 управления производится допуско-, вый контроль величины несинхронности.

В регистре 28 хранится значение , в регистре 29 - значение (п-д1).

Устройство работает следующим образом..

Задающим генератором 1 формируется серия тактовых. 1 мпульСов, которая поступает на счетный вход счетчика 16. По состояниям счетчика 16 на выходе дешифрато.ра 17 формируются выходные сигналы. Выходные сигналы через группу 6 элементов И 5 и элемент ИЛИ 23 поступают на группу 4 выходов устройства. По появлению пос.леднего сигнала на выходе дешифратора 17

.и прохождению его через элемент ИЛИ 18 производится установка в ноль счетчика 16,

.т.е. переход на следующий цикл выработкн сигналов.

При. допустимом расхождении пос- леднего сигнала на выходе дешифратора 17с появлением сигнала точного времени по CTpoi бирующему входу 3 цикл выработки сигналов является постоянным. При недопустимом расхождении вышеуказанных сигналов цикл выработки сигналов (цикл подсинхронизации) удлиняется на величину несинхронности данных сигналов. При этом последний управляющий сигнал цикла переносится на конец цикла подсинхронизации, т.е. количество управляющих сигналов в цикле ос:Тается неизменным. Величина несинхрон„ности хранится в регистре 9 до момента появления сигнала точного времени по стробирующему входу 3. В узле 10 сравниваются значения регистра 9 и счетчика 16. На выходе элемента И 14 вырабатывается сигнал начала режима подсинхронизации. При этом триггер 12 устанавливается в единичное состояние, инверсный выход которого в режиме подсинхронизации запрещает выработку управляющих сигналов. На выходе элемента И 13 формируется сигнал окончания режима подсинхронизации (цикла подсинхронизацни). При это.м вырабатывается последний сигнал цикла.

Допусковый контроль величины несинхронности в узле 15 управления произво-. дится следующим образом.ч

В начале цикла выработки у.правляющих сигналов (1, 2,..., И ) сигнал с выхода первого элемента И 5 группы 6 элементов И, поступает на устаиовочный вХод триггера 34,

После переключения триггера 34 тактовые импульсы с выхода задающего генератора 1 через элемент И 38 поступают на счетный вход счетчика 24. По .состояниям счетчика 24 на выходе дешифратора 25 формируются четырепоследовательных сигнала, которые управляют работой узла 15 упра.вления. При : наличии Сигнала на четвертом выходе дешифратора 25 и поступлении пятого тактеЭого импульса с выхода задающего генератора 1 на выход элемента И 31 сигнал с выхйда элемента И 31 поступает на нулевой вход триггера 34. После переключения триггера 34 сигнал с ,его инверсного выхода поступает на нулевой вход счетчика 24 Счетчик 24 находится в нуле до появления первого, сигнала на единичном входе триггера 34 в следующем цикле выработки сигналов. Рассмотрим работу узла 15 управления при попадании величины несинхронности в интервал синхронизации. Полный цикл работы узла 15 управления происходит за четыре такта.На .первом такте на первом выходе дешифратора 25 появляется управляющий сиг нал, по которому величина At из регистра 28 в прямом коде через группу элементов ИЛИ 36 подается на входы сумматора 26. При этом на другие входы сумматора 26 подается величина несинхронности из .ретистра 9 в инверсном коде, а на вход переноса младшего разряда сумматора 26 через элемент ИЛИ 30 - единица, т, е. на сумматоре 26 производится вычитание в дополнительном коде. Результат вычитания „получается отрицательным. Сигнал с единичного выхода знакового разряда сумматора 26 элемент И 32 за,носится в триг.гер 35. На втором такте на втором выходе дешифратора 25 появляется управляющий сигнал, по которому величина из регистра 29 в прямом коде через группу 37элементов ИЛИ 36 подается на входы сумматора 26 и производится вычитание в дополнительном коде. Результат вычитания получается положительным. Сигнал из нулевого выхода зна.кового разряда сумматора 26 через элемент ИЛИ 33 заносится в триггер 27. На третьем такте на третьем выходе дешифратора 25 появляется управляющий сигнал, по которому с учетом сигналов на единичных выходах триггеров 27 и 35 на выходе элемента И 39 вырабатывается сигнал требования подсинхронизации. На четвертом такте на четвертом выходе дешифратора 25 появляется управляющий сигнал, по которому производится ус:тановка в ноль триггеров 27 и 35. Рассмотрим работу устройства на временной диаграмме (фиг. 3). В момент времени tj во время появления сигнала точного времени по стробирующему входу 3 состояние .счетчика 16 (величина несинхронности) через группу 8 элементов И 7 переписывается на зегистр 9. Затем величина несинхронности из регистра поступает на первые входы сумматора 26, на вторые входы которого поступают предельные величины несинхронности из ретистров 28 и 29. В узле 15 управления производится допусковый контроль величины песинхронности и при попадании данной величины в интервал синхронизации на выходе, узла 15 управления вырабатывается сигнал требования подсинхронизации.; В момент времени t (начало режима подсинхронизации) сигнал из элемента И 39 поступает на единичный вход тригера II. В момент времени tj (конец режимй; подсинхронизации) на последнем выходе дещифратора 17 формируется сигнал, который через элемент И 14 поступает на единичный вход триггера 12 и через элемент ИЛИ 18 - на нулевой вход счетчика 16 Прохождение данного сигнала через последний элемент И 5 и ИЛИ 23 на последний выход устройства запрещается на эле{ менте И 5 отсутствием сигнала на инверс ном выходе триггера II. Сигнал с прямого выхода триггера 12 поступает на нулевой вход триггера II и на вход элемента И 13; В интервале времени выходные сигналы из дешифратора 17 запрещаются ни элементах И 5 отсутствием сигнала на инверсном выходе триггера 12. I В момент времени t,, в момент сравне-; ния величины несинхропности на регистре ,9 и состояния счетчика 16, на выходе узла 10 сравнения вырабатывается сигнал; который через элементы И 13 и ИЛИ 23 поступает на последний выход устройства (синхронно с появлением сигнала точного времени по стробирующему входу 3). Сиг-; нал с элемента И 13, кроме того, поступае на нулевые входы триггера 12, регистра 9, а также через элемент ИЛИ 18 - на нулевой вход счетчика 16 и переходит на следующий цикл выработки сигналов пос-. ле его установки в ноль. ° i На фиг; 2 представлена аппаратурная реализация узла 15 управления, выполняющая задачу допускового контроля величины несинхронности. Пр.актически целесообразно данную задачу выполнять по программе из ЦВМ, имеющуюся в вычислительной системе.; Рассогласование последнего сигнала уст-, ройства и сигнала точного времени, поступающего по стробирующему входу 3, вызванное нестабильностью генераторов тактовых импульсов, устраняется автоматичес ки без участия оператора. Использование предлагаемого устройст... ч за для синхронизации вычислительной сис-V темы обеспечивает по сравнению с иэвест- ными увадичение точности синхронизации и повышение, ее надежности. Предлагаемое устройство увеличивает точность синхронизации вычислительных .систем, работающих в реальном масштабе времени, и позволяет си.нхронизировать. ра-боту всех ЦВМ вычислительнойСистемы с еИГй1ЙЛайК t6 JBofo времени общей системы отсчета. Эффект от использования предложенного решения заключается в увеличении точности синхронизации вычислительной системы за счет синхронизации с сигналами точного времени о«щей системы отсчета и повыше НИИ надежности синхронизации вычислительной с(1отемы при .разовом появлении сиг нала точного времени путем запоминания величины несинхронности на специальном регистре до момента санкциоиированной синхронизации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для суммирования | 1972 |

|

SU458825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 997546, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-23—Публикация

1982-09-03—Подача