(21)4481375/24-24

(22)06.09.88

(46) 23.07.90. Бюл. № 27 (72) А.А.Лоскутов, Р.А.Кулиев и Г.М.Ладыгина

(53)681.325(088.8)

(56) Авторское свидетельство СССР № 1081639, кл. G 06 F 13/00, 1982.

Авторское свидетельство СССР № 1238093, кл. & 06 F 13/00, 1986.

(54)УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ

(57) Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными между источниками и приемниками информации. Целью изобретения является повышение помехозащищенности за счет обеспечения аппаратной селекции ложных синхроимпульсов. Устройство содержит блок памяти, регистр информации, регистр адреса, коммутатор, три триггера, два элемента задержки, дна одновибратора, два элемента И-НЕ., элемент ИЛИ-НЕ, элемент И-ИЛИ, элемент НЕ. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными между источниками и приемниками информации. Целью изобретения является повышение помехозащищенности за счет обеспечения аппаратной селекции ложных синхроимпульсов. Устройство содержит блок памяти, регистр информации, регистр адреса, коммутатор, три триггера, два элемента задержки, два одновибратора, два элемента И - НЕ, элемент ИЛИ - НЕ, элемент И - ИЛИ, элемент НЕ. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными между источниками и приемниками информации .

Цель изобретения - повышение по-- мехозащйщенности за счет обеспечения аппаратной селекции ложных синхроимпульсов .

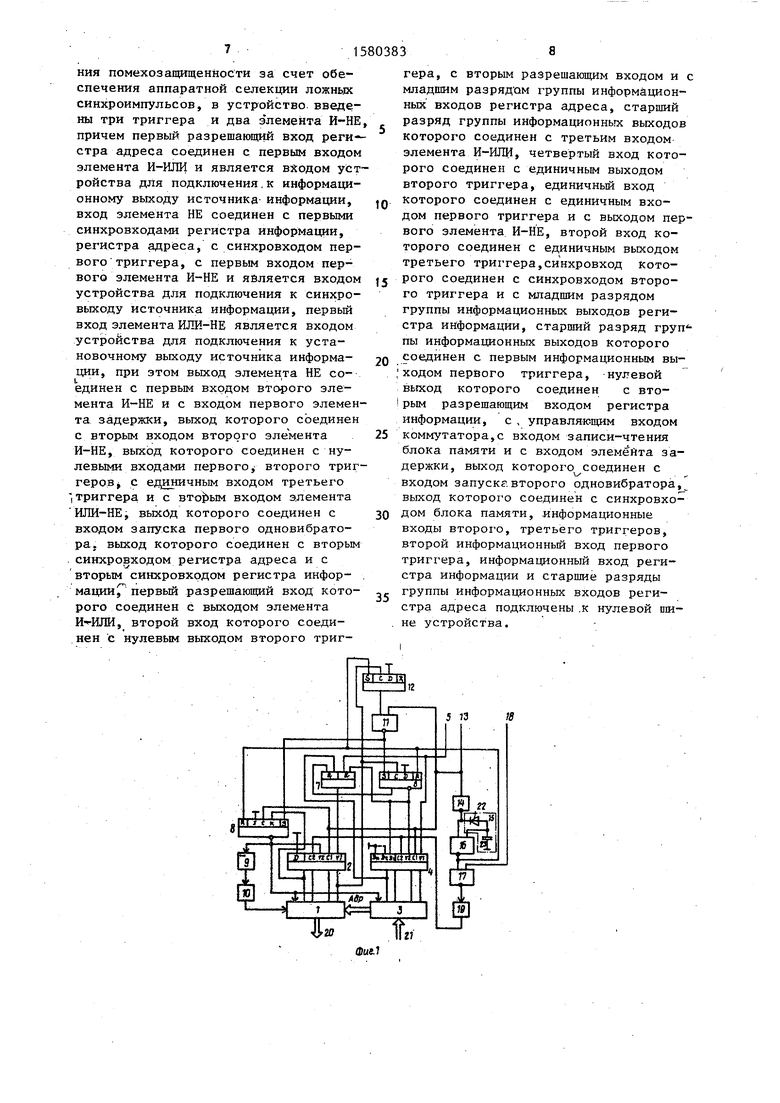

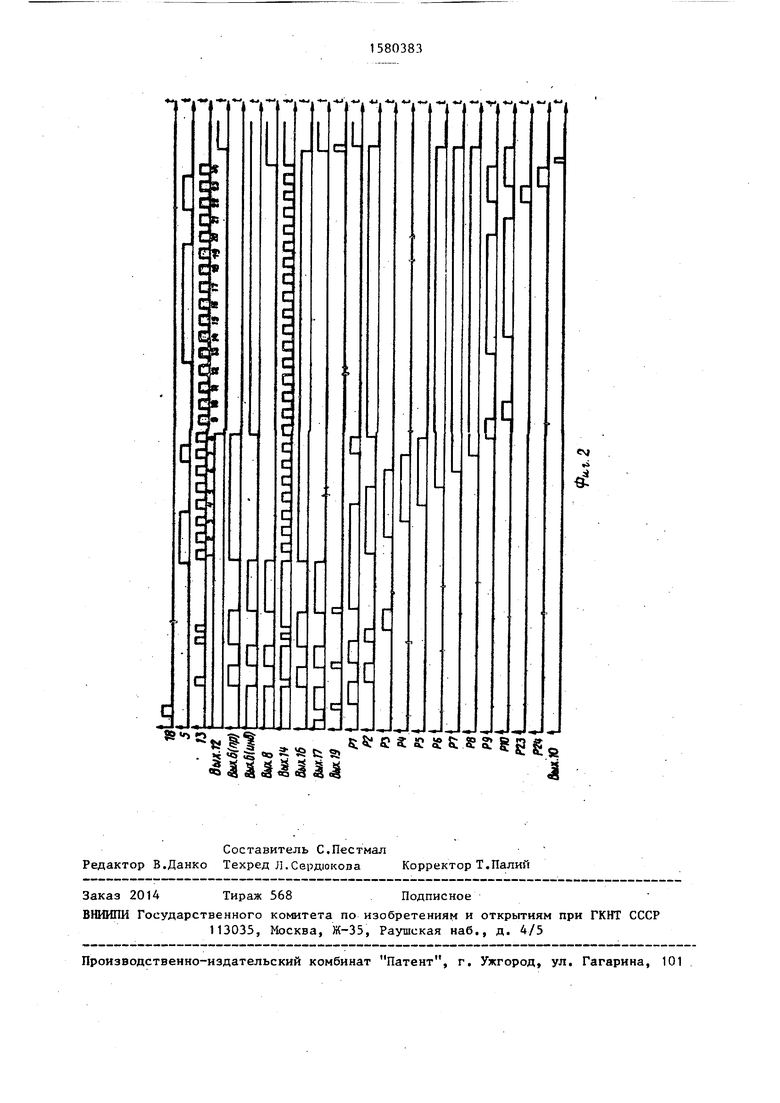

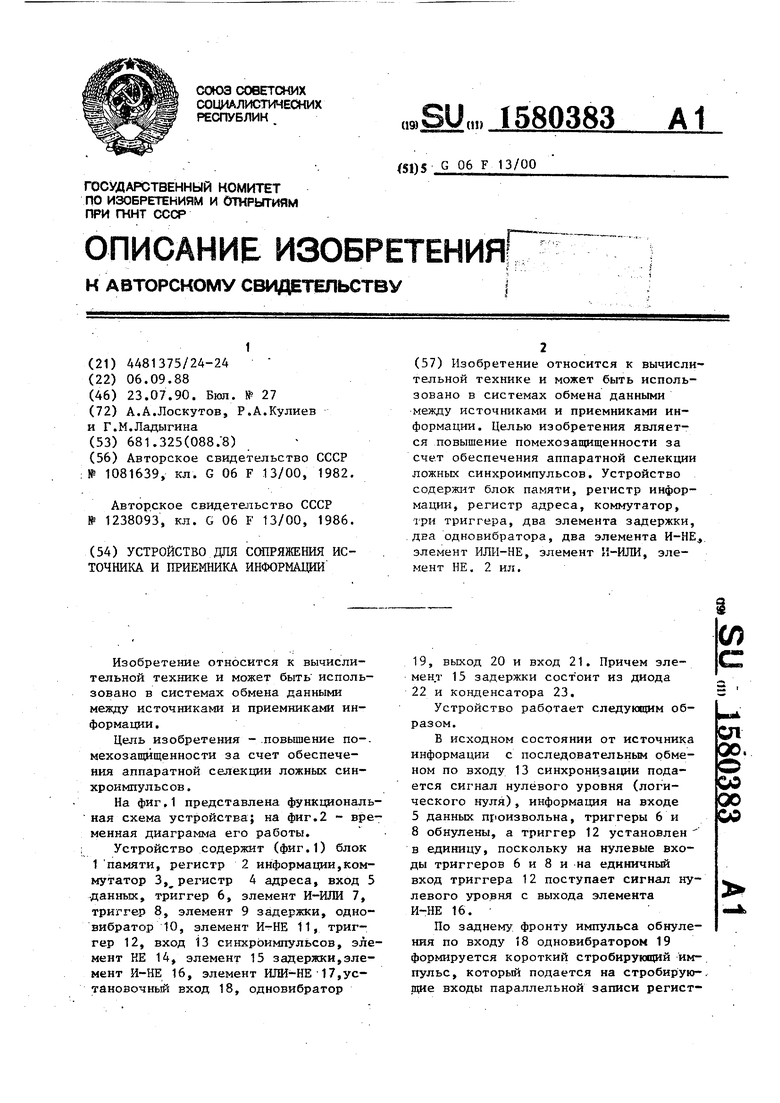

На фиг,1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма его работы.

Устройство содержит (фиг.1) блок 1 памяти, регистр 2 информации,коммутатор 3,регистр 4 адреса, вход 5 данных, триггер 6, элемент И-ИЛИ 7, триггер 8, элемент 9 задержки, одно- вибратор 10, элемент И-НЕ 11, триггер 12, вход 13 синхроимпульсов, элемент НЕ 14, элемент 15 задержки,элемент И-НЕ 16, элемент ИЛИ-НЕ .установочный вход 18, одновибратор

I

(Л

19, выход 20 и вход 21. Причем элемент 15 задержки состоит из диода 22 и конденсатора 23.

Устройство работает следующим образом.

В исходном состоянии от источника информации с последовательным обменом по входу 13 синхронизации подается сигнал нулевого уровня (логического нуля), информация на входе 5 данных произвольна, триггеры 6 и 8 обнулены, а триггер 12 установлен в единицу, поскольку на нулевые входы триггеров 6 и 8 и на единичный вход триггера 12 поступает сигнал нулевого уровня с выхода элемента И-НЕ 16.

По заднему фронту импульса обнуления по входу 18 одновибратором 19 формируется короткий стробирующий импульс, который подается на стробирую- щие входы параллельной записи регист-

ел

00,

о

ОЭ 00 00

ров 2 и 4. Во все разряды этих регистров, кроме первого (младшего) разряда регистра 4, при этом записывается нулевая информация, поскольку н входах разрешения параллельной запис регистров 2 и 4 в это время держатся сигналы единичного уровня, поступающие с нулевых выходов соответственно триггеров 8 и 6. На информационных входах триггера 8 находятся сигналы нулевого уровня, запрещающие срабатывание триггера 8 по стробирующему входу. Логическая единица, записанная в первый разряд регистра 4 адре- са по стробу параллельной записи, в дальнейшем,при последовательном приеме информации используется как маркер. Под действием сигнала единичного уровня, снимаемого с нулевог выхода триггера 8, блок 1 находится в режиме записи информации по адресу, поступающему через коммутатор 3 с выходов регистра 4 адреса.

Для записи информации в регистры

4и 2 по .входу 13 синхронизации передается пачка синхроимпульсов, число которых равно разрядности адресной и информационной частей принимаемого слова, вместе взятых (для примера, при 8-разрядном адресе и 16-разрядном информационном слове 24 синхроимпульса).

Под каждый синхроимпульс по входу

5информации передается информация соответствующего разряда, которая записывается последовательным кодом

в регистры 4 и 2. Подобная система передачи информации уязвима от помех по входу синхронизации, так как импульс помехи воспринимается как импульс синхронизации. Устройство решает задачу помехозащищенности в таких системах обмена.

Допустим, что в период ожидания приема по входу 13 синхронизации устройством был принят импульс помехи (фиг.2). По переднему фронту импульса помехи триггеры 6 и 8 перейдут в единичное состояние, запрещая па- раллельный и разрешая последовательный ввод информации в регистры адреса 4 и информации 2, а также переводя блок 1 в режим считывания информации по адресам, поступающим через коммутатор 3 с адресного входа 21. По заднему фронту импульса помехи информация, которая была в этот момент на входе 5 (логический

ноль на временной диаграмме), будет принята в первый разряд регистра 4 адреса, а маркер из первого разряда переместится во второй разряд этого регистра.

По окончании импульса помехи выход элемента И-НЕ 16 не сможет принять состояние логического нуля до тех пор, пока конденсатор 23 входным вытекающим током не будет заряжен до напряжения, соответствующего уровню срабатывания элемента И-НЕ .Дальнейшая работа устройства будет зависеть от того, через какой интервал времени придет следующий импульс по входу 13 синхронизации. Если этот интервал времени превысит время заряда конденсатора 23 до напряжения, соответствующего уровню срабатывания элемента И-НЕ 16, что практически всегда выполняется при приеме импульсов помех, то устройство будет возвращено в исходное состояние нулевым уровнем сигнала с выхода элемента И-НЕ 16 и стробирующим импульсом с выхода одновибратора 19, формируемым по заднему фронту сигнала с выхода элемента ИЛИ-НЕ 17 (первый одиночный импульс помехи на временной диаграмме). Если же интервал времени между импульсами не превысит время заряда конденсатора 23 до напряжения, соответствующего уровню срабатыванияэлемента И-НЕ 16,то будет принята информация, по следующему импульсу помехи, поступившему по входу 13 (второй и третий импульсы помехи, следующие один за другим на временной диаграмме), а конденсатор 23 за время действия импульса разрядится до нулевого уровня через диод 22 и выход элемента НЕ 14, По заднему фронту 3-го импульса помехи маркер перепишется в третий разряд регистра 4 адреса. По окончании третьего импульса помехи конденсатор 23 будет заряжаться, сработает элемент И-НЕ 16 и устройство вновь возвратится в исходное положение.

Таким образом, регулируя выбором величины емкости конденсатора 23 время задержки заднего фронта импульса синхронизации, можно обеспечить как уверенный прием информации, стробиру- емой регулярно следующими импульсами синхронизации, так и надежную очистку регистров 4 и 2 от ложной инфорнации, стробируемой случайными импульсами помех.

Прием информации происходит следующим образом.

По переднему фронту первого импульса синхронизации, поступившего по входу 13,триггеры 6 и 8-устанавливаются в единичное состояние, разрешая нулевым уровнем сигнала вторым разрешающим входам регистров 2 и 4 последовательный прием информации, а также переводя блок 1 в режим считывания информации.

По заднему фронту синхроимпульсов входная информация будет последовательным кодом записываться в регистр 4 адреса, а маркер перемещаться в сторону старших разрядов (при приеме старшими разрядами вперед). По 8-му импульсу синхронизации через элемент И-ИЛИ 7 маркер запишется в девятый разряд регистров (первый разряд регистра 2 информации), что приведет к сбросу по стробиругощему входу триггеров 6 и 12, и, следовательно, к запрету сигналом единичного уровня по второму разрешающему входу последовательного приема информации в регистр 4 адреса. Этим же сигналом единичного уровня с нулевого выхода триггера 6 будет разрешён через элемент. И-ИЛИ 7 прием информации по входу 5 непосредственно в регистр 2 информации.

По заднему фронту 23-го синхроимпульса маркер, т.е. сигнал единичного уровня, поступит на первый ин- формационный вход триггера 8, подготавливая условия для сброса этого триггера по заднему фронту 24-го синхроимпульса. Срабатывание триггера 8 приведет к-запрету последовательного приема информации в регистр 2, обеспечит через коммутатор 3 подключение выходов регистра 4 адреса к адресным входам блока 1, переведет блок 1 в режим записи информации,при этом с задержкой, обусловленной элементом 9 задержки, по переднему фронту сигнала с выхода этого элемента одновибратором 10 будет сформирован стробирующий импульс для записи информации в блок 1, по заднему фронту которого содержимое регистра 2 информации будет записано в соответствующую принятому адресу ячейку блока 1.

Так как интервал времени между пачками синхроимпульсов больше ин0

5

0

5

0

5

0

S

0

тервала времени между синхроимпульсами в пачке, то по окончании пачки синхроимпульсов конденсатор 23 зарядится до напряжения, соответствующего уровню срабатывания элемента И-НЕ 16, при срабатывании которого примут исходное состояние триггеры 6 и 8, а одновибратором 19 будет сформирован стробирующий импульс записи исходного состояния в регистры адреса 4 и информации 2.

Следует отметить, что задержка сигнала элементом 9 задержки должна быть меньше задержки срабатывания элемента И-НЕ 16 по .заднему фронту импульса синхронизации, что необходимо для того, чтобы успеть записать информацию из регистра 2 в блок 1 до , установки регистра 2 в исходное состояние. С момента установки исходного состояния устройство готово к приему следующего слова.

Таким образом, устройство по отношению к известному обладает повышенной надежностью за счет улучшения помехозащищенности канала последовательной передачи, а использование маркера позволяет отказаться от счетчика синхроимпульсов в схеме формирования адреса блока 1

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее блок памяти, регистр информации, регистр адреса, коммутатор, два од- новибратора, два элемента задержку элемент ИЛИ-НЕ,элемент НЕ,элемент И-ИЛИ,причем первая группа информационных входов коммутатора и /группа информационных выходов блока памяти образуют группу входов и выходов устройства для подключения соответственно к группе адресных выходов и к группе информационных входов приемника информации, при этом группа информационных выходов регистра адреса соединена с второй группой информационных входов коммутатора, группа информационных выходов Которого соединена с группой адресных входов блока памяти, группа информационных входов которого соединена с группой информационных выходов регистра информации, отличающееся тем, что, с целью повышения помехозащищенности за счет обеспечения аппаратной селекции ложных синхроимпульсов, в устройство введены три триггера и два элемента И-НЕ причем первый разрешающий вход регистра адреса соединен с первым входом элемента И-ИЛИ и является входом устройства для подключения,к информационному выходу источника информации, вход элемента НЕ соединен с первыми синхровходами регистра информации, регистра адреса, с синхровходом первого триггера, с первым входом первого элемента И-НЕ и является входом устройства для подключения к синхро- выходу источника информации, первый вход элемента ИЛИ-НЕ является входом устройства для подключения к установочному выходу источника информации, при этом выход элемента НЕ соединен с первым входом второго элемента И-НЕ и с входом первого элемента задержки, выход которого соединен с вторым входом второго элемента И-НЕ, выход которого соединен с нулевыми входами первого, второго триггеров, с единичным входом третьего , триггера и с вторым входом элемента ИЛИ-НЕ, выход которого соединен с входом запуска первого одновибрато- ра, выход которого соединен с вторым синхровходом регистра адреса и с вторым синхровходом регистра информации первый разрешающий вход которого соединен с выходом элемента ИЧ1ЛИ, второй вход которого соединен с нулевым выходом второго тригТ 1

Фиг.)

5

0

5

0

5

гера, с вторым разрешающим входом и с младшим разрядом группы информационных входов регистра адреса, старший разряд группы информационных выходов которого соединен с третьим входом элемента И-ИЛИ, четвертый вход которого соединен с единичным выходом второго триггера, единичный вход которого соединен с единичным входом первого триггера и с выходом первого элемента И-НЕ, второй вход которого соединен с единичным выходом третьего триггера,синхровход которого соединен с синхровходом второго триггера и с младшим разрядом группы информационных выходов регистра информации, старший разряд груп пы информационных выходов которого соединен с первым информационным вы- ходом первого триггера, нулевой выход которого соединен с вто- iрым разрешающим входом регистра информации, с , управляющим входом коммутатора,с входом записи-чтения блока памяти и с входом элемейта задержки, выход которого соединен с входом запуске второго одновибратора, выход которого соединен с синхровходом блока памяти, информационные входы второго, третьего триггеров, второй информационный вход первого триггера, информационный вход регистра информации и старшие разряды группы информационных входов регистра адреса подключены к нулевой шине устройства.

Авторы

Даты

1990-07-23—Публикация

1988-09-06—Подача