(5) АРИ МЕТИЧЕСКОЕ УСТРОЙСТВО ПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для быстрого преобразования Фурье | 1984 |

|

SU1231513A1 |

| Арифметическое устройство для быстрого преобразования фурье | 1984 |

|

SU1234846A1 |

| Многоканальный цифровой фильтр | 1990 |

|

SU1751781A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1984 |

|

SU1211750A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Конвейерный умножитель | 1988 |

|

SU1575175A1 |

| Устройство для умножения | 1978 |

|

SU769540A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

1

Изообретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных устройств, выполняющих алгоритм быстрого преобразования Фурье (БПФ).

Известно арифметическое устройство i,Ay), используемое для выполнения алгоритма БПФ. Устройство содержит регистры реальной и мнимой частей комплексных весовых коэффициентов, два регистра чисел, два сумматора поразрядных сумм и два сумматора чигсел С П.

Недостатком такого устройства является невысокая погрешность вычислений, обусловленная операцией округления на этапе умножения.

Наиболее близким к изобретению является арифметическое устройство npof: цессора быстрого преобразования -Фурье содержащее шесть регистров множителя, восемь регистров множимого, двенадцать блоков элементов И, шесть сумматоров первого уровня, восемь накапливающих сумматоров, каждый из которых состоит из сумматора и регистра сдвига ,2.

Недостатком известного устройства является большая длительность такта работы устройства, определяемая как сумма задержек на сумматорах всех уровней.

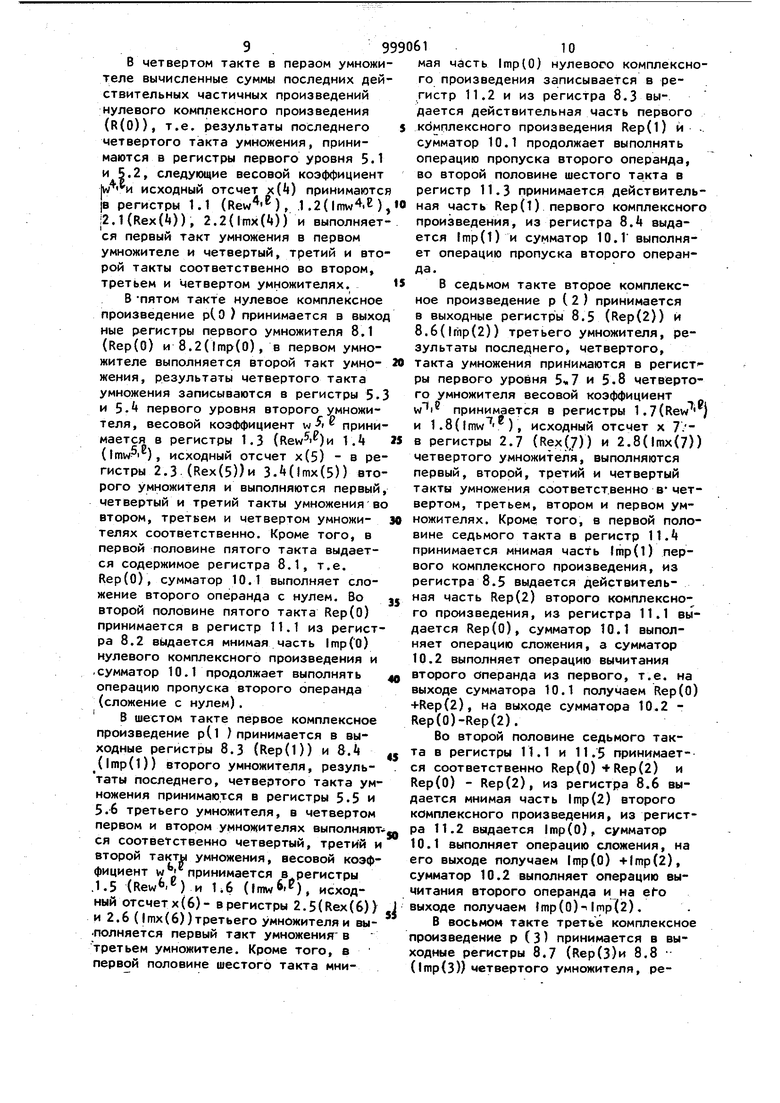

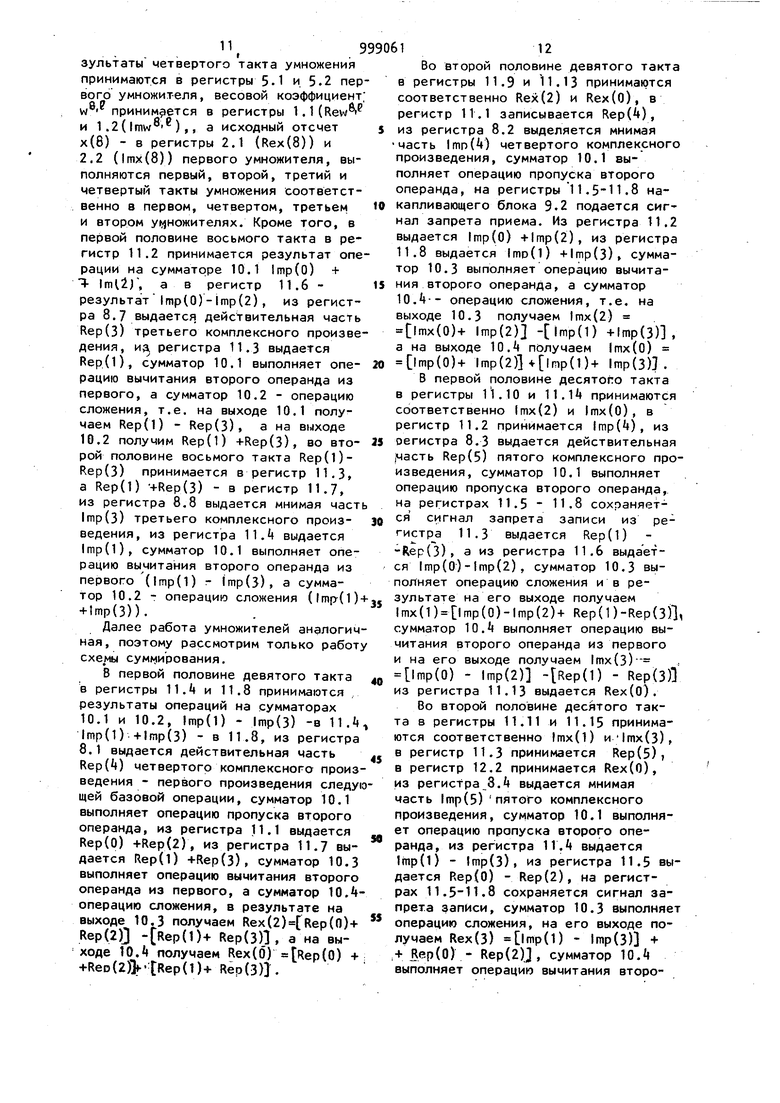

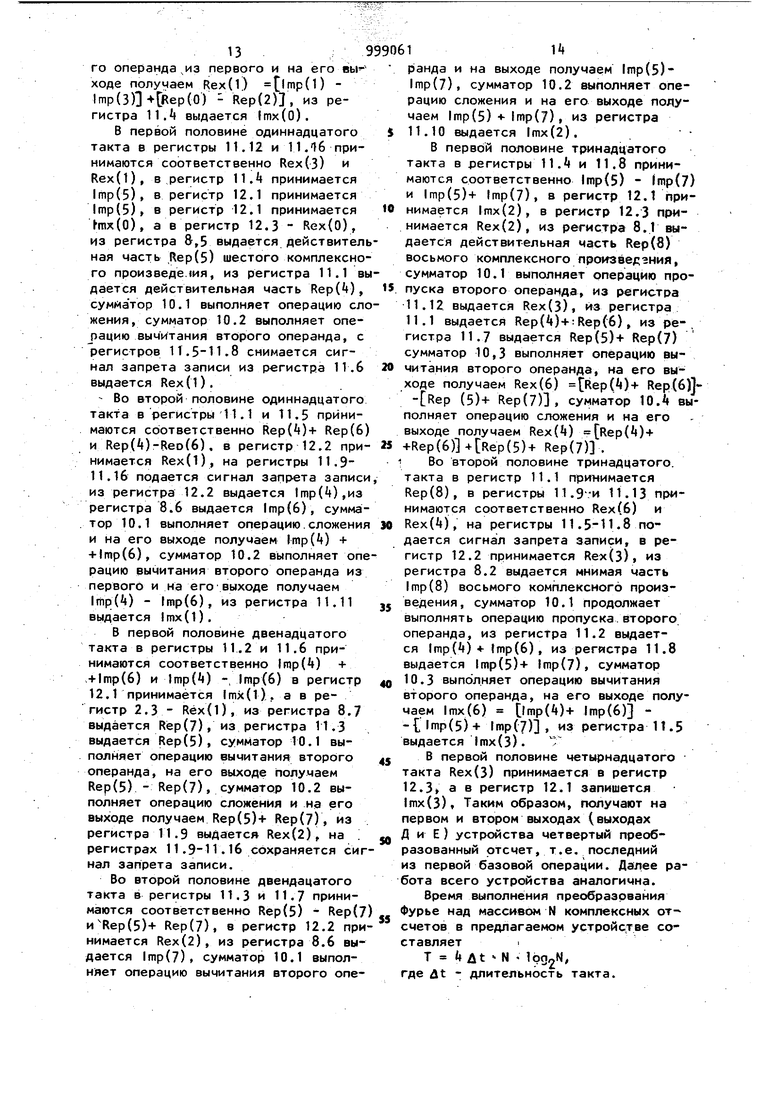

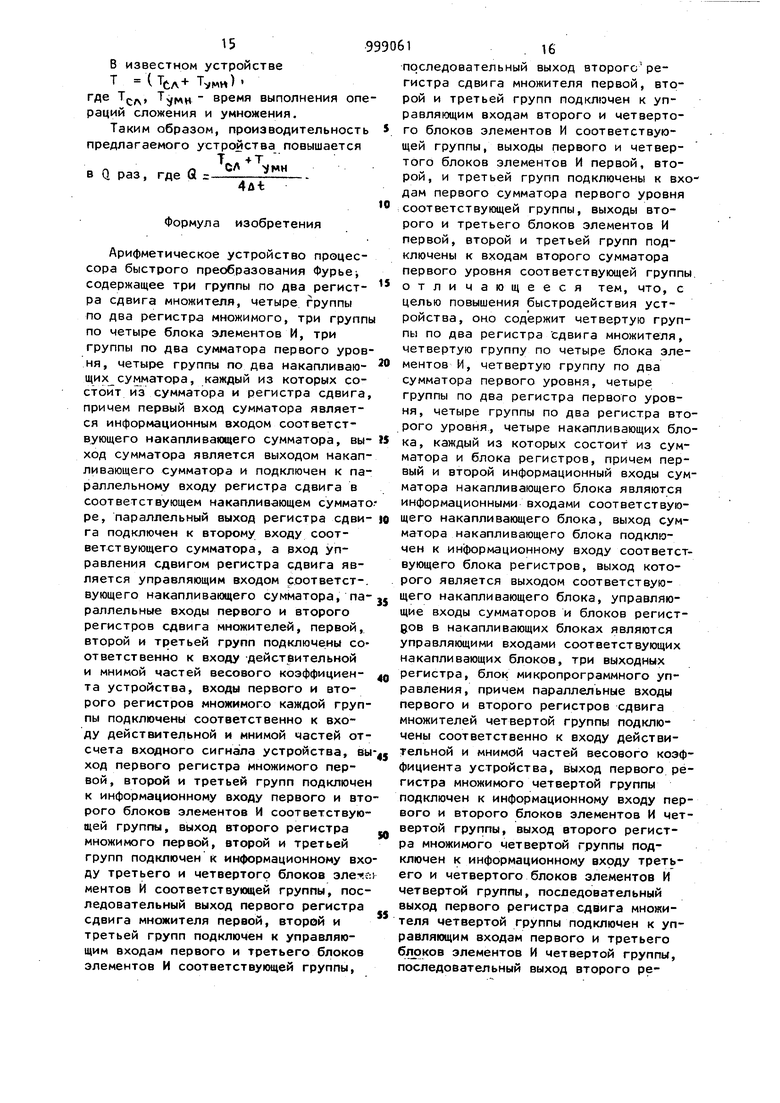

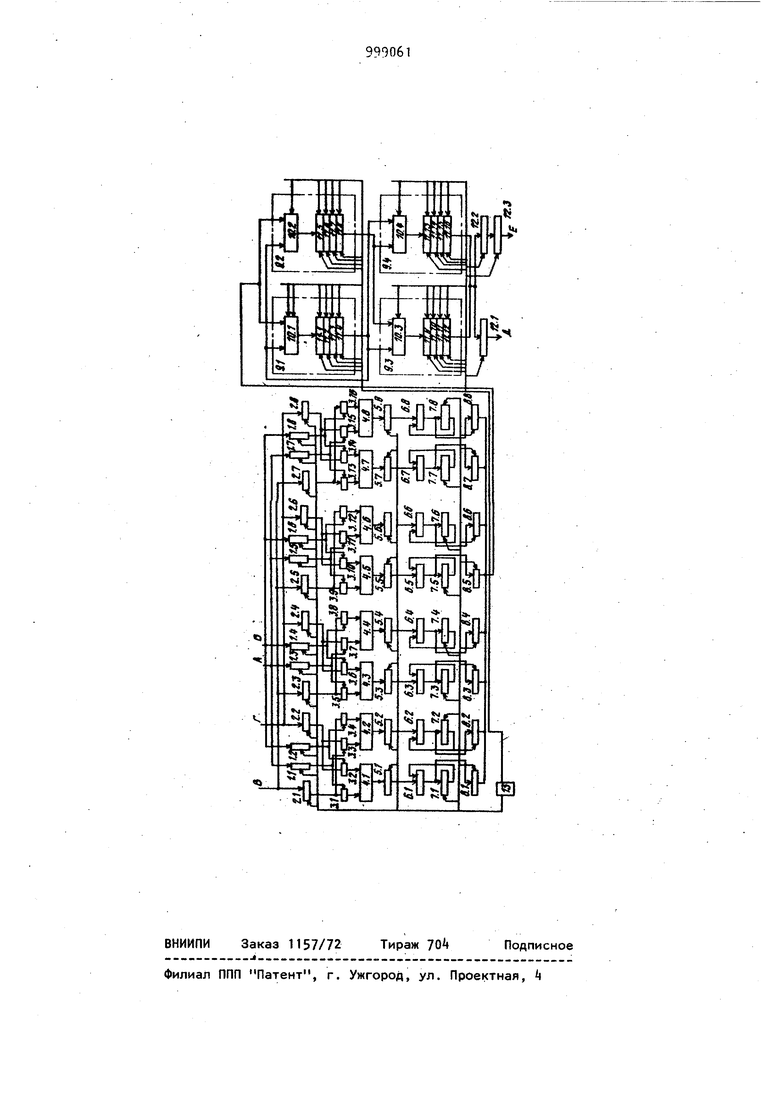

Кроме того, в нем нельзя а течение первой итерации выполнить умножение исходного массива на весовую функцию, например, вида 1/2 (1-cos 2 2Лп)/М), где ,1,2,.. .N-1. Heвoз oжнocть совмещения во времени выполнения первой итерации и умнржения исходных данных на весовую функцию обусловлено тем, что в известном устройстве выполняет2JJ ся только три комплексных умножения, iкоторых достаточно для выполнения базовой операции преобразования Фурье но недостаточно для умножения на весовую функцию. Целью изобретения является увеличение быстродействия устройства. Поставленная цель достигается тем что арифметическое устройство процес сора быстрого преобразования Фурье, с.одержащее три группы по два регистра сдвига множителя, четыре группы п два регистра множимого, три группы п четыре блока элементов И, три группы по два сумматора первого уровня, четыре группы по два накапливающих сум матора, каждый из которых состоит из сумматора и регистра сдвига, причем первый вход сумматора является инфор мационным входом соответствующего на капливающего сумматора, выход сумматора является выходом накапливающего сумматора и подключен к параллельном входу ре;;истра сдвига в соответствующем накапливающем, сумматоре, параллельный выход регистра сдвига под ключен к второму входу соответствующего сумматора, а вход управления сдвигом регистра сдвига является управляющим входом соответствующего накапливающего сумматора, параллельные входы первого и второго регистров сдвига множителей первой, второй и третьей групп подключены соответственно к входу деист, вительной и мнимой частей весового коэффициента устройства, входы первого и второго регистров множимого кйждрй группы подключены соответственно к входу действительной и мнимой частей отсчета входного сигнала устройства, выход первого регистра множимого первой, второй и третьей групп подключен к информационному входу первого и второго блоков элементов И соответствующей группы, выход второго регистра множимого первой, второй и третьей групп подключен к информационному входу третьего и четвертого блоков элементов И соответствующей группы, последовательный выход первого регистра сдвига множителя первой, второй и третье групп подключен к управляющим входам первого и третьего блоков элементов И соответствующей группы последовательный выход Btoporo регистра сдвига множителя первой, второй и третье групп подключен к управляющим входам второго и четвертого блоков элементов И соответствующей группы, выходы первого и четвертого блоков элементов И первой, второй и третьей гоупп подключены к входам первого сумматора первого уровня соответствующей группы, выходы второго и третьего блоков элементов И первой, второй и третьей групп подключены к входам второго сумматора первого уровня соответствующей группы, содержит четвертую группу по два регистра сдвига множителя, четвертую группу по четыре блока элементов И, четвертую группу по два сумматора первого уровня, четыре группы по два регистра первого уровня, четыре группы по два регистра второго уровня, четыре накапливающих блока, каждый из которых состоит из сумматора и блока регистров, причем первый и второй информационные входы сумматора накапливающего блока являются информационными входами соответствующего накапливающего блока, выход сумматора накапливающего блока подключен к информационному входу соответствующего блока регистров, выход которого является выходом соответствующего накапливающего блока, управляющие входы сумматоров и блоков регистров в накапливающих блоках являются управляющими входами соответствующих накапливающих блоков, три выходных регистра, блок микропрограммного управления, причем параллельные входы первого и второго регистров сдвига множителей четвертой группы подключены соответственно к входу действительной и мнимой частей весового коэффициента устройства, выход первого регистра множимого четвертой группы подключен к информационному входу первого и второго блоков элементов И четвертой группы, выход второго регистра множимого четвертой группы подключен к информационному входу третьего и четвертого блоков элементов И четвертой группы, последовательный выход первого регистра сдвига множителя четвертой группы подключен к управляющим входам первого и третьего блоков элементов И четвертой группы, последовательный выход второго регистра сдвига множителя четвертой группы подключен к управляющим входам второго и четвертого блоков элементов И четвертой группы, выходы первого и четвертого блоков элементов И четвертой группы подключены к входам первого сумматора первого уровня четвертой группы, выходы второго и третьего блоков Iэлементов И четвертой группы подключены к входам второго сумматора первого уровня четвертой .группы, выходы сумматоров первого уровня всех групп подключены к входам соответствующих регистров первого уровня, выходы которых подключены к информацй онным входам соответствующих накапливающих сумматоров, выходы накапливающих сумматоров подключены к инфор мационным входам соответствующих регистров, второго уровня, выходы всех регистров второго уровня подключены к первым информационным входам перво го и второго накапливающих блоков, первые информационные входы третьего и четвертого накапливающих блоков подключены к выходу второго накапливающего блока, вторые информационные входы первого, второго, третьего.и четвертого накапливающих блоков подключены к выходу первого накапливающего блока, выходы третьего и чет вертого накапливающих блоков подключ ны к информационным входам первого и второго выходных регистров, выход вт рого выходного регистра подключен к информационному входу третьего выход ного регистра, выходы первого и трет его выходных регистров являются выходами устройства, выходы блока микропрограммного управления подключены к управляющим входам регистров сдвига множителей, регистров множимо ГО, регистров первого и второго уров неи, накапливающих сумматоров, накап ливающих блоков и выходных регистров На чертеже представлена функциональная схема арифметического устройства процессора быстрого преобразования Фурье. Устройство содержит регистры 1.11.8 сдвига мнржителя, регистры 2.12.8 множимого, блоки элементов И 3.13.16, сумматоры . 1 -4.8 первого уровня,. регистры 5.1-58 первого уровня, сумматоры 6.1-6.8 и регистры сдвига 7.1-7.8 входящие в состав накапливающих сумматоров, регистры 8. второго уровня, накапливающие бло| 9.1 -9.. ) состоящие из сумматоров ,10.1-10. и блоков регистров 11.1111.16 выходные регистры 12.1-12.3, блок 13 микропрограммного управления. Регистры 1.1-1.8 сдвига множителя обеспечивают последовательный анализ разрядов множителя при умножении выходного отсчета на коэффициент методом накопления. Объединение выходов регистров 8.18.8 и регистров 11.1-11.16 накапливающих блоков 9.1-9.| можно осущест-. вить, используя, например, регистры с тремя состояниями на выходе. Имеющие управляющие входы выдачи информации, или используя мультиплексоры. В качестве сумматоров 10.1-10..А накапливающих блоков 9.1-9. можно использовать известные микросхемы арйфметикологических устройств, выполняющих операции сложения и вычитания, а для сумматора 10.1 еще и операцию пропуска второго операнда, т.е. сложение его с нулем. Структура, образуемая регистрами 1.1, 1.2 множителя регистрами 2.1,2.2 множимого,, блоками элементов И 3.1-3., сумматорами первого уровня «.I, .2, регистрами первого уровня 5.1, 5.2, накапливающими сумматорами, состоящими из сумматоров . 6.1, 6.2 и регистров 7.1, 7.2 и регистрами 8.1, 8.2, четырежды повторяясь, составляет первую часть схемы и представляет собой комплексный умножитель, выполняющий вычисления по формуле.р U, P()(i) jlmx(i) xTRew Vj Rex(()Rew - Гтх(Г)1т w« jtRex( Г) --lmw -Hmx(i)Rewy, Регистры 2.1, 2.2 множимого прииимают исходный отсчет, 2.1 - действительную часть Rex{i), 2.2 - мни- . мую часть Imx(i). Регистры 1.1, 1.2 множителя принимают весовой коэффициент, 1.1- действительную часть 2-- ТМИМУЮ часть Im.w.На первый вход сумматора . приходят частичные произведения Rex(i) Rew на второй -. частичные произведения Imx(i) . На выходе сумматора «.I получается разность этих частичных произведений. На первый вход сумматора 4.2 приходят .частичные произведения Imx(i) Rew , на второй - частичные произведения Rex (т) , на выходе сумматора 4.2 получается сумма этих частичных произведений. Затем выполняется накопление сумм частичных произведений на накапливаюих сумматорах 6.1, 7.1 и 6.2, 7.2 на регистры 8.1, 8.2 пpинимaюtcя ействительная Rep(О и мнимая 1гпр(1) части комплексного произвеения, Rep(l) - в 8.1, (mp(i) в 8.2. щая из четырех накапливающих блоков 9... и трех выходных регистров 12.1-12.3 представляет собой схему суммирования, которая формирует окон нательные результаты преобразования в соответствии с выражением x(i) ГВер()+ Rep(i-i-2)fRep(i + 1} + Rep()}b j(lmp{i) + lmn(i+2)) + / + (jrnp(H-l)+ fmp{i+3))}; х( 1+1 J Rep( i)-Rep( i-t-2) - 1тр( i + -lmp(i+3)+j C(Rep(i+l)-Rep(i+3) + + (|1га|)(т)-1тр(|+2); x(i+2)Rep(i)+ Rep(i+2) - ; (i + l) + Rep(i+3)+j ((l) + + lmp(i+2)-(lmp(i + l)+ lmp(i+3)) x(i+3)CRep.(i)-Rep(i+2)}fnmp(i + 1) - lrnp(-H)-j(Rep(i + l)-Rep(i+3) -(lmp(i)-lmp(i+2)) где p(i),p(i+l), p(i+2),p(i+3) - ком плексные произведения исходных отсче тов на весовые коэффициенты;Re(...) - действительная часть числа; 1т(...) - мнимая часть числа; x(i),x(i+l),x(i+2),x(i+3) -резул таты преобразования. Блок 13 микропрограммного управления может состоять из генератора синхронизирующих импульсов, счетчика тактов и блока памяти микрокоманд (ПЗУ), адресные входы которого соединены с выходами соответствующих разрядов счетчика тактов, а выходы являются выходами блока микропрограм-з5 много управления. Поскольку все составные части арифметического устройства, кроме сумматора 10.-1, должны работать не более чем в двух режимах (сложение - вычи- 40 тание, прием - запрет приема, выдача - зап|эет выдачи ), для каждого уп равляющего сигнала достаточно одног разряда. Для сумматора 10.1 требует ся два управляющих разряда, так как он должен работать в трех.режимах: сложение, вычитание второго операнда, пропуск второго операнда (сл ,жение его с нулем). Рассмотрим работу АУ при выполнении базовой операции. Для примера рассмотрим случай, когда весовые коэффициенты четырехразрядные, т.е. для умножения требуется четыре такта. Поскольку комплексные исходные отсчеты x(i) принимаются в умножители последовательно со сдвигом на такт, то результаты комплексных умн хо)цные регистры умножителей тоже со сдвигом на такт, причем в каждом такте принимаются параллельно действительная Rep(i) и мнимая Imp(i) части комплексных произведений. Организация схемы суммирования предполагает последовательный, поток действительных и мнимых частей комплексных произведений, поэтому за один такт схема суммирования должна успеть принять два числа: Rep(i) и imp(i) с тем, чтобы в следующем такте принять действительную Rep{i+1) и мнимую lmn(i+l) части следукхцего комплексного произведения. Таким образом, длительность.такта работы схемы суммирования в два раза меньше, чем временной интервал между приемом комплексных отсчетов в выходные регистры соседних умножителей Поэтому работу схемы суммирования мы будем рассматривать по половинам такта. Будем считать, что прием во все регистры осуществляется по началу такта для схемы суммирования - по началу такта и началу второй половины такта ). В нулевом такте весовой коэффициент w°i принимается в регистры 1.1 множителя (Rew ) и 1.2 (.a исходный отсчет х(о) - в регистры 2.1 множимого (Rex(о)) и 2.2{1тх(о) первого умножителя и выполняется первый такт умножения. В первом такте весовой коэффициент принимается в регистры 1.3 множителя (Rew) и 1.4 (), а исходный отсчет х(1) - в регистры 2.3 множимого (Rex (1)) и 2.А (lmx(l)). выполняется первый такт умножения во втором и второй такт в первом умножителях. Во втором такте принимается весовой коэффициент регистры 1.5 () и .1.6 (т , исходный отсчет х(2) - в регистры 2.5 (Rex(2) и 2.6 (тх(2) и выполняется первый такт умножения в третьем умножителе, второй и третий соответственно во втором и первом умножителях. В третьем такте весовой коэффициент w записывается в регистры 1.6 () и 1.8 (imw), исходный отсчет х(3) записывается в регистры 2.7 (Rex(3)) и 2.8 (1п1х(3)) и выполняются первый, второй, третий и четвертый такты умножения соответственно в четвертом, третьем, втором и первом умножителях. теле вычисленные суммы последних дей ствительных мастичных произведений нулевого комплексного произведения (R(O)), т.е. результаты последнего четвертого такта умножения, принимаются в регистры первого уровня 5.1 и 5.2, следующие весовой коэффициент исходный отсчет x.(k) принимаются IB регистры 1.1 (), .1.2( ) i2.1(Rex()), 2.2(Гп1х()) и выполняется первый такт умножения в первом умножителе и четвертый, третий и второй такты соответственно во втором, третьем и четвертом умножителях. В-пятом такте нулевое комплексное произведение р(0 ) принимается в выход ные регистры первого умножителя 8.1 (Вер(О) и 8.2(1тр(0), в первом умножителе выполняется второй такт умножения, результаты четвертого такта умножения записываются в регистры 5.3 и 5. первого уровня второго умножителя, весовой коэффициент принимается в регистры 1.3 {Rew)H 1.4 (), исходный отсчет х(5) - в регистры 2.3 (Кех(5))и 3.4(1тх(5)) второго умножителя и выполняются первый четвертый и третий такты умножения во втором, третьем и четвертом умножителях соответственно. Кроме того, в первой половине пятого такта выдается содержимое регистра 8.1, т.е. Rep(O), сумматор 10.1 выполняет сложение второго операнда с нулем. Во второй половине пятого такта Rep(О) принимается в регистр 11.1 из регистра 8.2 выдается мнимая часть Imp(О) нулевого комплексного произведения и .сумматор 10.1 продолжает выполнять операцию пропуска второго операнда (сложение с нулем). В шестом такте первое комплексное произведение p(l ) принимается в выходные регистры 8.3 (RepO)) и 8.4 (Iпр(1)) второго умножителя, результаты последнего, четвертого такта умножения принимаются в регистры 5.5 и 5.6 третьего умножителя, в четвертом первом и втором умножителях выполняют ся соответственно четвертый, третий и второй такты умножения, весовой коэффициент W принимается в регистры .1.5 ( ) и 1i6 (), исходный отсчет х( 6)-в регистры 2.5 (Rex (6) и 2.6 (1тх(6)}третьего умножителя и вы-полняется первый такт умноженияв трет ьем умножителе. Кроме того, в первой половине шестого такта мниго произведения записывается в регистр 11.2 и из регистра 8.3 выдается действительная часть первого комплексного произведения Rep(l) и сумматор 10.1 продолжает выполнять операцию пропуска второго операнда, во второй половине шестого такта в регистр 11.3 принимается действительмая часть Rep(1) первого комплексного произведения, из регистра 8.4 выдается 1тр(1) и сумматор 10.1 выполняет операцию пропуска второго операнда. В седьмом такте второе комплексное произведение р ( 2 ) принимается в выходные регистры 8.5 (Rep(2)) и 8.6(1 (Tip(2)) третьего умножителя, результаты последнего, четвертого. такта умножения принимаются в регист ры первого уровня и 5.8 четвертого умножителя весовой коэффициент IW jr mnvmtn I лл ocv wouti 1Ч(с цл4/| цпсп i wi принимается в регистры 1.7(Rew ) и 1.8(), исходный отсчет х 7.в регистры 2.7 (Rex(у)) 2.8(1тх(7)) четвертого умножителя, выполняются первый, второй, третий и четвертый такты умножения соответственно вчетвертом, третьем, втором и первом умножителях. Кроме того, в первой половине седьмого такта в регистр 11.4 принимается мнимая часть lrap(l) первого комплексного произведения, из регистра 8.5 выдается деиствительная часть Rep(2) второго комплексного произведения, из регистра 11.1 выдается Rep(о), сумматор 10.1 выполняет операцию сложения, а сумматор 10.2 выполняет операцию вычитания второго операнда из первого, т.е. на выходе сумматора 10.1 получаем Rep(O) +Rep(2), на выходе сумматора 10.2 Rep(0)-Rep(2). Во второй половине седьмого такта в регистры 11.1 и 11.5 принимается соответственно Rep(O) fRep(2) и Rep(O) - Rep(2), из регистра 8.6 выдается мнимая часть 1тр(2) второго комплексного произведения, из регист выдается 1тр(0}, сумматор 10.1 выполняет операцию сложения, на его выходе получаем Imp(O) +lmp(2), сумматор 10.2 выполняет операцию вычитания второго операнда и на eto выходе получаем Imp(O)-1тр(2). В восьмом такте третье комплексное произведение р (3) принимается в выходные регистры 8.7 (Лер(З)и 8.8 (1тр(3)) четвертого умножителя, результаты четвертого такта умножения принимаются в регистры 5.1 и 5.2 пер вого умножителя, весовой коэффициент W принимается в регистры 1.1(Rew и 1 .2( ) ,, а исходный отсчет х(6) - в регистры 2.1 (Rex(8)) и 2.2 (1тх(8)) первого умножителя, выполняются первый, второй, третий и четвертый такты умножения соответственно в первом, четвертом, третьем и втором у1 4ножителях. Кроме того, в первой половине восьмого такта в регистр 11.2 принимается результат опе рации на сумматоре 10.1 Imp(O) н1- ImUr, а в регистр 11.6 результат lmp(0)-imp(2), из регистра 8.7 выдается действительная часть Rep(3) третьего комплексного произве дения, ия регистра 11.3 выдается .. . .., „ Rep(1), сумматор 10.1 выполняет oneрацию вычитания второго операнда из первого, а сумматор 10.2 - операцию сложения, т.е. на выходе 10.1 получаем Rep(l) - Rep(3), а на выходе 10.2 получим Rep{l) +Rep(3), во второй половине восьмого такта Rep(l)Rep{3) принимается в регистр 11.3, а Rep(l) +Rep(3) - в регистр 11.7, из регистра 8.8 выдается мнимая част 1тр(3) третьего комплексного произведения, из регистра 11. выдается 1тр(1), сумматор 10.1 выполняет операцию вычитания второго операнда из первого (|глр(1) - 1тр(3), а сумматор 10.2 - операцию сложения (lmp(l) +tmp(3)). Далее работа умножителей аналогич ная, поэтому рассмотрим только работ схемы сум|| ирования. В первой половине девятого такта в регистры 11.4 и 11.8 принимаются результаты операций на сумматорах 10.1 и 10.2, Impd) - lmp{3) -в 11.i lmp(l) +lmp(3) - в 11.8, из регистра 8.1 выдается действительная масть RepC) четвертого комплексного произ ведения - первого произведения следу щей базовой операции, сумматор 10.1 выполняет операцию пропуска второго операнда, из регистра 11.1 выдается Rep(O) +Rep(2), из регистра 11.7 выдается Repd) +Rep(3), сумматор 10.3 выполняет операцию вычитания второго операнда из первого, а сумматор 10.4 операцию сложения, в результате на выходе 10.3 получаем Rex(2)Rep(0)+ Rep(2) (l)-f Rep(3n , a на выходе 10.i получаем Rex(6) (0) + 4-ReD{2)(1)+ Rep(3) . Во второй половине девятого такта в регистры 11.9 и 11.13 принимаются соответственно Rex(2) и Rex(O), в регистр 11.1 записывается Rep(4}, из регистра 8.2 выделяется мнимая часть Imn() четвертого комплексного произведения, сумматор 10.1 выполняет операцию пропуска второго операнда, на регистры 11..8 накапливающего блока 9.2 подается сигнал запрета приема. Из регистра 11.2 выдается Imp(O) +lmp(2), из регистра 11.8 выдается lmp(l) +1тр(3) сумматор 10.3 выполняет операцию вычитания второго операнда, а сумматор 10.-- операцию сложения, т.е. на выходе 10.3 получаем lnix(2) lmx(0)+ lmp(2) (1) +lmp(3)l, a на выходе 10. получаем Imx(O) lmp(0)+ lnip(2)(l)+ lmp(3)J . В первой половине десятого такта в регистры Il.lO и 11.Н принимаются соответственно 1тх(2) и Imx(O), в регистр 11.2 принимается ImpC), из оегистра 8.3 выдается действительная (Масть Rep(5) пятого комплексного произведения, сумматор 10.1 выполняет операцию пропуска второго операнда, на регистрах 11.5 - 11.8 сохраняется сигнал запрета записи из регистр а 11.3 выдается Rep(l) -Rep(3), а из регистра 11.6 выдается lmp(0)-lmp(2), сумматор 10.3 выполняет операцию сложения и в результате на его выходе получаем lmx(1) lmp(0)-lmp(2)+ Rep(1 )-Rep(3ni сумматор lO.i выполняет операцию вычитания второго операнда из первого и на его выходе получаем 1тх(3) 1тр(0) - 1тр(2) ) - Rep(3) из регистра 11.13 выдается Rex(O). Во второй половине десятого такта в регистры 11.11 и 11.15 принимаются соответственно lmx(l) и Мтх(З), в регистр 11.3 принимается Rep(5), в регистр 12.2 принимается Rex(O), из регистра 3. выдается мнимая часть 1тр(5)пятого комплексного произведения, сумматор 10.1 выполняет операцию пропуска второго операнда, из регистра И. выдается 1тр(1) - 1тр(3), из регистра 11.5 выдается Rep(O) - Rep(2), на регистрах 11.3-11.8 сохраняется сигнал запрета записи, сумматор 10.3 выполняет операцию сложения, на его выходе получаем Rex(3) Clnip(l) - lmp(3) + Rep(O) - Rep(2)j , сумматор 10.i выполняет операцию вычитания второго операнда из первого и на его выходе получаем Rex(1.) lmp(1) tnip(3)(0) - Rep(2), из регистра 11.it выдается Imx(O). В первой половине одиннадцатого такта в регистры 11.12 и 11.16 принимаются соответственно RexCS) и Rex(l), в регистр 11. принимается 1тр(5), в регистр 12.1 принимается 1тр{5), в регистр 12.1 принимается l-raxio), а в регистр 12.3 - Rex{0), из регистра 8,5 выдается действитель ная часть Rep(5) шестого комплексного произведе.жя, из регистра 11.1 вы дается действительная часть RepCt), сумматор 10.1 выполняет операцию сло жения, сумматор 10.2 выполняет операцию вычитания второго операнда, с регистров 11.5-11.8 снимается сигнал запрета записи из регистра 11.6 выдается Rex(l). Во второй половине одиннадцатого такта в регистры 11.1 и 11.5 принимаются соответственно Rep(4)+ Rep{6) и Rep()-ReD(6), в регистр 12.2 принимается Rex(l), на регистры 11.911.16 подается сигнал запрета записи из регистра 12.2 выдается тр(),из регистра 8.6 выдается 1тр(6), сумма. тор 10.1 выполняет операцию.сложения и на его выходе получаем ImpCf) + +lmp(6), сумматор 10.2 выполняет опе рацию вычитания второго операнда из первого и на его выходе получаем Imp(A) - lmp(6), из регистра 11.11 выдается Imx(l). В первой половине двенадцатого такта в регистры 11.2 и 11.6 принимаются соответственно 1гар(4) + + 1тр(6) и ImpC) -, lmp(6) в регистр 12.1 принимается lmx(l). а в регистр 2.3 - Rex(l), из регистра 8.7 выдается Rep(7), из регистра 11.3 выдается Rep(5), сумматор 10.1 выполняет операцию вычитания второго операнда, на его выходе получаем Rep(5) - Rep(7), сумматор 10.2 выполняет операцию сложения и на его выходе получаем Rep(5)+ Rep(7), из регистра 11.9 выдается Rex{2), на . регистрах 11.9-11.16 сохраняется сиг нал запрета записи. Во второй половине двендацатого такта в регистры П.З и 11.7 принимаются соответственно Rep(5) - Rep(7 HRep(5)+ Rep(7), в регистр 12.2 при нимается Rex(2), из регистра 8.6 выдается 1тр(7), сумматор 10.1 выполняет операцию вычитания второго опе9ранда и на выходе получаем 1тр(5)1тр(7), сумматор 10.2 выполняет операцию сложения и на его выходе получаем 1тр(5) «- 1тр(7), из регистра 11.10 выдается 1тх(2). В первой половине тринадцатого такта в регистры П. и 11.8 принимаются соответственно 1тр{5) - 1тр(7) и 1тр(5)+ 1тр(7), в регистр 12.1 принимается 1тх(2), в регистр 12.3 принимается Rex(2), из регистра 8.1 выдается действительная часть Rep(8) восьмого комплексного произведения, сумматор 10.1 выполняет операцию пропуска второго операнда, из регистра 11.12 выдается Rex(3), из регистра 11.1 выдается Rep(4) + :Rep(6), из ре-, гистра 11.7 выдается Rep(5)+ Яер(7) сумматор 10,3 выполняет операцию вычитания второго операнда, на его выходе получаем Rex (6) Rep(l)+ Rep(6) (5)+ Rep(7), сумматор 10. выполняет операцию сложения и на его выходе получаем RexCi) Rep{) + +Rep(6)(5)+ Rep(7) . Во второй половине тринадцатого, такта в регистр 11.1 принимается Rep(8) , в регистры 11.9И 11.13 принимаются соответственно Rex(6) и RexCt), на регистры 11..8 подается сигнал запрета записи, в регистр 12.2 принимается Rex(3), из регистра 8.2 выдается мнимая часть 1тр(8) восьмого комплексного произведения, сумматор 10.1 продолжает выполнять операцию пропуска.второго операнда, из регистра 11.2 выдается ImpC) ttnp{6), из регистра 11.8 выдается 1тр(5)+ 1тр(7), сумматор 10.3 выполняет операцию вычитания второго операнда, на его выходе получаем lfflx(6) tlmp(t)+ lmp(6) -1 lfnp(S)+ lmp(7) , из регистра It. 5 выдается Imx(3). В первой половине четырнадцатого такта Rex(3) принимается в регистр 12.3 а в регистр 12.1 запишется 1тх(3) Таким образом, получают на первом и втором выходах (выходах Д и Е ) устройства четвертый преобразованный отсчет, т.е. последний из первой базовой опера14ии. Далее работа всего устройства аналогична. Время выполнения преобразования Фурье над массивом N комплексных от счетов в предлагаемом устройстве составляетТ At N IpOgN, где At - длительность такта. 159 В известном устройстве Т ( ТсдЧ- ) где Т., - время выполнения опе раций сложения и умножения, Таким образом, производительность предлагаемого устройства повышается Т-.+Т СЛ в Q раз, где Q Формула изобретения Арифметическое устройство процессора быстрого преобразования Фурье, содержащее три группы по два регистра сдвига множителя, четыре группы по два регистра множимого, три группы по четыре блока элементов И, три группы по два сумматора первого уров ня, четыре группы по два накапливаю1цих сумматора, каждый из которых состоит из сумматора и регистра сдвига, причем первый вход сумматора является информационным входом соответствующего накапливающего сумматора, выход сумматора является выходом накапливающего сумматора и подключен к параллельному входу регистра сдвига в соответствующем накапливающем суммато ре, параллельный выход регистра сдвига подключен к второму входу соответствующего сумматора, а вход управления сдвигом регистра сдвига является управляющим входом роответст-. вующего накапливающего сумматора, параллельные входы первого и второго регистров сдвига множителей, первой, второй и третьей групп подключены соответственно к входу действительной и мнимой частей весового коэффициента устройства, входы первого и второго регистров множимого каждой груп пы подключены соответственно к входу действительной и мнимой частей от счета входного сигнала устройства, вы ход первого регистра множимого первой, второй и третьей групп подключе к информационному входу первого и вто рого блоков элементов И соответствую щей группы, выход второго регистра множимого первой, второй и третьей групп подключен к информационному вх ду третьего и четвертого блоков зле-г ментов И соответствующей группы, пос ледовательный выход первого регистра сдвига множителя первой, второй и третьей групп подключен к управляющим входам первого и третьего блоков элементов И соответствующей группы. 1 последовательный выход второгорегистра сдвига множителя первой, второй и третьей групп подключен к управляющим входам второго и четвертого блоков элементов И соответствующей группы, выходы первого и четвертого блоков элементов И первой, второй, и третьей групп подключены к вхо дам первого сумматора первого уровня соответствующей группы, выходы второго и третьего блоков элементов И первой, второй и третьей групп подключены к входам второго сумматора первого уровня соответствующей группы, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит четвертую группы по два регистра сдвига множителя, четвертую группу по четыре блока элементов И, четвертую группу по два сумматора первого уровня, четыре группы по два регистра первого уровня, четыре группы по два регистра второго уровня, четыре накапливающих блока , каждый из которых состоит из сумматора и блока регистров, причем первый и второй информационный входы сумматора накапливающего блока являются информационными входами соответствующего накапливающего блока, выход сумматора накапливающего блока подключен к информационному входу соответствующего блока регистров, выход которого является выходом соответствующего накапливающего блока, управляющие входы сумматоров и блоков регистров в накапливающих блоках являются управляющими входами соответствующих накапливающих блоков, три выходных регистра, блок микропрограммного управления, причем параллельные входы первого и второго регистров сдвига множителей четвертой группы подключены соответственно к входу действительной и мнимой частей весового коэффициента устройства, выход первого регистра множимого четвертой группы подключен к информационному входу первого и второго блоков элементов И четвертой группы, выход второго регистра множимого четвертой группы подключен к информационному входу третьего и четвертого блоков элементов И четвертой группы, последовательный выход первого регистра сдвига множителя четвертой группы подключен к управляющим входам первого и третьего блоков элементов И четвертой группы, последовательный выход второго регистра сдвига множителя четвертой группы подключен к управляющим входам второго и четвертого блоков элементов И четвертой группы, выходы первого и четвертого блоков элемеитов.И четвертой группы подключены к входам первого сумматора первого уро ня четвертой группы, выходы второго и третьего блоков элементов И четвер той группы подключены к входам второго сумматора первого уровня четвертой группы, выходы сумматоров пер вого уровня всех групп подключены к вхбдам соответствующих регистров пер вого уровня, выходы которых подключе ны к информацйонйым входам соответствующих накапливающих сумматоров, выходы накапливающих сумматоров подключены к информационным входам соот ветствующих регистров второго уровня выходы всех регистров второго уровня подключены к первым информационным входам первого и второго накапливающих блоков, первые информационные входы третьего и четвертого накапливающих блоков подключены к выходу второго накапливающего блока, вторые информационные входы первого, второго, третьего и четвертого иакапливаю6118щих блоков подключены к выходу первого накапливаю1цего блока, выходы третьего и четвертого накапливающих блоков подключены к информационным входам первого и второго выходных регистров, выход второго выходного регистра подключен к информационному входу третьего выходного регистра, выходы первого и третьего выходных регистров являются выходами устройства, выходы блока микропрограммного управления подключены к управляющим входам регистров сдвига множителей| регистров множимого регистров первого и второго уровней, накапливающих сумматоров, накапливающих бгоков и выходных регистров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 467356, кл.С 06 F 15/332, 1975. 2.Gottlieb Paut, Lorenzo Leonard J. d.e. Parallel data Stems and serial arithmetic for Fourier transform Process. Transactions on Acoust. Speech and Signal Process, 197, 2, p.11.1-117 (прототип).

Авторы

Даты

1983-02-23—Публикация

1981-06-05—Подача