оо

4:

оо

оо

Изобретение относится к электротехнике и может быть использовано в преобразовательной технике для управления вентильными преобразователями в структурах прецизионных систем электропитания.

Цель изобретения - повышение качества выпрямленного напряжения за счет обеспечения его инвариантности к низ- кочастотным помехам питающей сети.

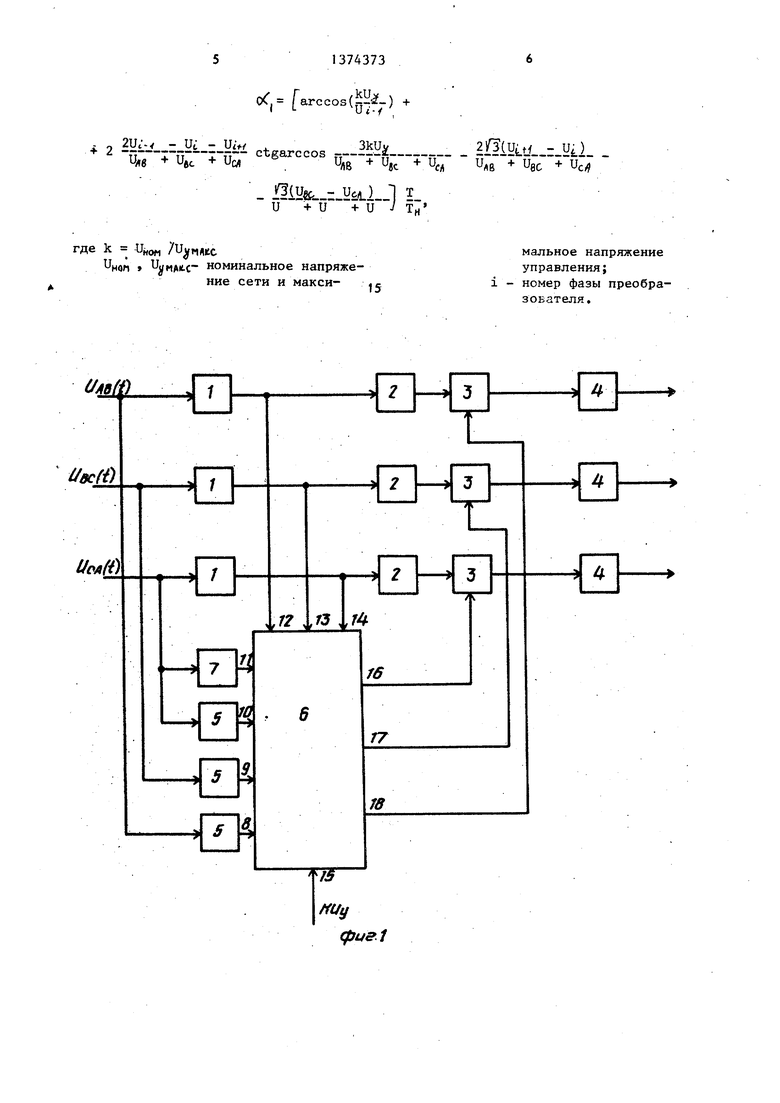

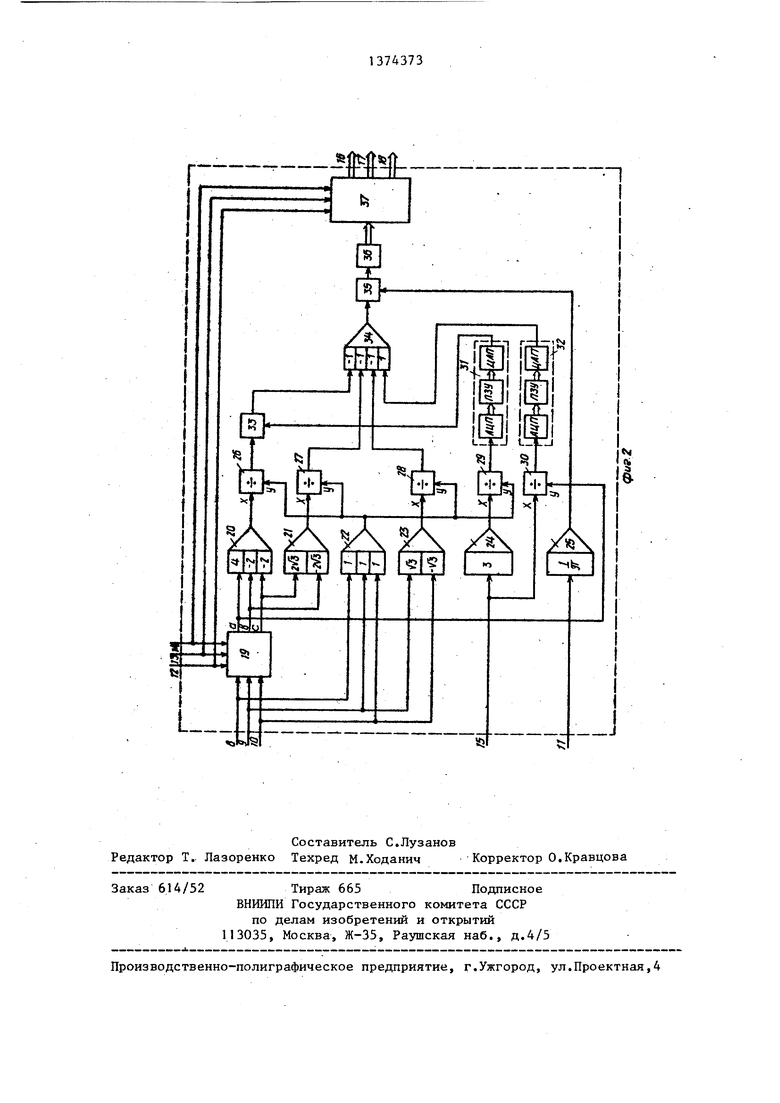

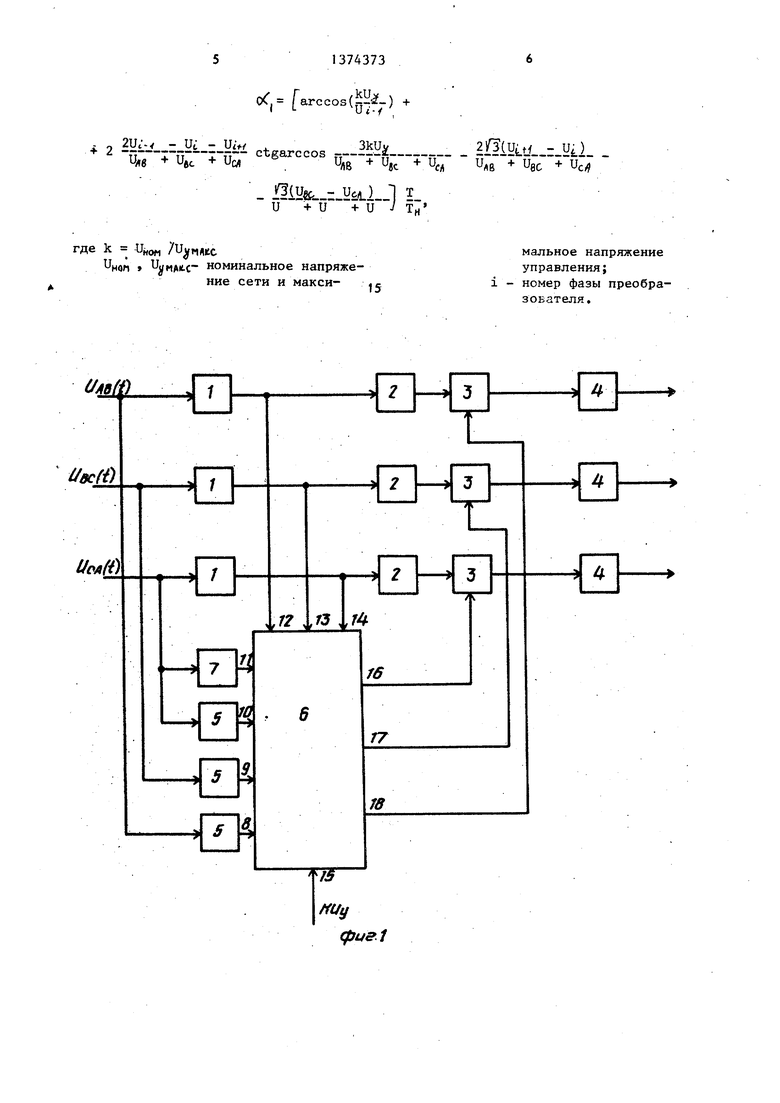

На фиг,1 приведен вариант трехка- нального устройства, реализующий предложенный способ управления; на фиг.2 - пример функциональной схемы вычислительного блока.

Каждый канал устройства содержит последовательно включенные формирователь 1 меандра, генератор 2 линейно изменяющегося напряжения развертки, нуль-орган 3 и формирователь 4 им- пуЛьс:ов.

Входы формирователей 1 меандра первого, второго и третьего каналов подключены соответственно к линейным напряжениям , ,11 , .U и через со- ответствзпощие блоки 5 измерения амплитуд напряжения подсоединены к входам вычислительного блока 6.

Вход формирователя 1 меандра треть его канала подключен к выходу измерителя 7 длительности периода. Блоки 5 и измеритель 7 подключены к входам 8-11 вычислительного блока 6. Входы 12 - 14 вычислительного блока 6 подключены к выходам формирователей 1 меандра первого, второго и третьего каналов соответственно. Вход 15 вычислительного блока 6 подсоединен к входу источника управляющего напря- жения, а выходы 16 - 18 вычислительного блока 6 подключены к вторым входам нуль-органов 3.

Входы 8-10 вьтислительного блока получающие с выходов блоков 5 измере- ния амплитуд сигналы, пропорциональные амплитудам соответствзтощих линейных напряжений, подключены через входы селектора 19 к сумматорам 20 и 21, входы 9 и 10 - к входам суммато- ров 22 и 23. Выходы а, Ъ, с селектора 19 подсоединены к входам сумматора 20, а выходы Ъ и с - к входам сумматора 21. Входы 12 - 14 вычислительного блока 6 подсоединены к входу усилителя 24, а вход 11 - к входу мДсштабного усилителя 25, выходы сумматоров 20 - 23 - к входам делителей 26 - 30, выход сумматора 22 д

5

0

5

5 0

5 0 5

к входам у делителей 26 - 29, а вход X последнех о - к выходу усилителя 24.

Выходы делителей 29 и 30 подсоединены к арккосинусным функциональным . преобразователям 31 и 32, выход делителя 26 - к блоку перемножения 33, второй вход которого подключен к выходу делителя 29 через функциональный преобразователь 31 вида ft ctg (arches об ).

Выход сумматора 34 подсоединен к блоку 35 перемножения. Выход аналого-цифрового преобразователя 36 подсоединен к входу демультиплексора 37, выходы которого являются выходами 16 - 18 вычислительного блока 6. УправляюЕще входы 12 - 14 вычислительного блока являются одновременно управляющими входами демультиплексора 37.

Устройство для реализаций предлагаемого способа работает следующим образом.

Формирователи 1 формируют из подводимых напряжений Пд, Ug, , 11. прямоугольные импульсы с длительностью, равной полупериоду сетевого напряжения (меандры), которые используются в блоках 2 дня формирования опорного пилообразного напряжения и одновременно выполняют функцию информационного кода для управления элементами вычислительного блока 6. Сформированное в блоках 2 пилообразное напряжение развертки поступает на первый вход компараторов 3, где сравнивается с напряжением задания, формируемым в вычислительном блоке 6. В момент их равенства компараторы 3 срабатывают, что фиксируется формирователем импульсов 4, который формирую ет импульсы для последующего распределения их по тиристорам.

Напряжение задания формируется в вычислительном блоке 6 в соответствии с предлагаемым законом по заданной величине управляющего напряжения и измеренным с помощью блоков 5 амплитуды линейных напряжений и с помощью блока 7 измеренной фактической длительности периода сетевых напряжений. Измеритель периода строится по принципам, основанным на считывании количества высокочастотной последовательности импульсов на периоде сети с преобразованием в двоичный код с последующим цифроаналоговым преобразованием. Блоки измерения амплитуд

также могут строиться по различным принципам.

В соответствии с кодом управляющего сигнала вычислительный блок 6 вычисляет величины напряжений задания в соответствии с предлагаемым способом. В качестве вычислительного блока 6 может быть использован микропроцессор или специализированное устройство, один из вариантов которого приведен на фиг.2. Реализация вычислительного блока может быть осуществлена как в цифровом, так и аналоговом вариантах.

Сигналы, соответствующие амплитудам и

АВ 6С

и

рд -линейных напряже

НИИ сети, поступают на информационны .входы 8-10 селектора 19, на управляющие входы которого 12 - 14 подается сигнал соответствз/ющего кода. В зависимости от управляющего кода на выходе селектора 19 входные напряжения перекбммутируются на выходы а, Ъ, с, с которых подаются на сумма трры 20 и 21, где суммир:лотся в соответствии с требуемыми масштабными преобразованиями. На сумматоры 22 и 23 напряжения подаются с входа вычислительного блока 6. Управляющий сигнал с входа 15 вычислительного блока поступает на масштабный усилитель 24. Дальнейшая процедура вычислений ясна из функциональной схемы вычислительного блока. Функциональные преобразователи 31 и 32 удобнее всего выполнить с использованием постоянных запоминающих устройств (ПЗУ), для чего аналоговьй сигнал преобразуется в цифровую форму с помощью аналого-цифрового преобразователя, а затем вновь осуществляется преобразование цифрового кода, снимаемого с выхода ПЗУ в аналоговую форму с помощью цифроаналогового преобразователя (ЦАП). Учет влияния изменения частоты сети на величину угла включения учитывается с помощью пере мнокителя 35, на один вход которого подается сигнал, пропорциональный углу включения вентилей с учетом колебаний, отклонений и несимметрии сети, снимаемьй с выхода сумматора 34, а на второй вход подается сиг-. нал, пропорциональный отношению периода сети к его номинальному значению поступающий с выхода масштабного усилителя 25.

5

0

0

5

5

0

5

0

С выхода перемножителя 35 сигнал задания подается на коммутатор, выполненный в виде последовательно, соединенных аналого-цифрового преобразователя и демультиплексора 37. Полученный сигнал поступает на второй вход компаратора. При линейном напряжении развертки, которое легче осуществить в цифровых генераторах развертки, величины фазового сдвига импульса, поступающего на управление тиристорами, образующегося на выходе компаратора строго пропорциональна величине напряжения задания, формируемого в вычислительном блоке, и тем самым в формировании углов включения вентилей используется закон управления, соответствующий предлагаемому способу.

При использовании предлагаемого способа обеспечивается эффективное снижение низкочастотных помех питающей сети в выпрямленном напряжении преобразователя, одновременно снижаются неканонические гармоники,, буждаемые в выпрямленном напряжении несимметрией питающей сети в 50- 100 раз при 2-3%; колебания и отклонения выпрямленного напряжения, обусловленные колебаниями и отклонениями напряжений питающей сети с частотами F 30 Гц в 30-50 раз. В такой же степени снижается влияние колебаний частоты питающей сети.

Формула из обре тения

Способ управления вентильным преобразователем, заключающийся в том, что формируют и подают импульсы управления на вентили каждой фазы преобразователя с углом ей , определяв напряжением управления и„, отличающийся тем, что, с J целью повышения качества выпрямленного напряжения за счет обеспечения его инвариантности к низкочастотным помехам питающей сети, измеряют амп-:: литуды линейных напряжений питающей сети Uj,, , и, , и,-, , длительность периода сетевого напряжения Т, задают номинальную длительность периода Т„, и для каждого из напряжений сети по заданному напряжению управления Uu формируют угол . в соответствии с формулой

51374373

ОС, farccos(§Hs) +

. „ 2Uc - - Ui - .3kUv

2 ------ ctgarccos

+ Ujc + UM q,g + u,t + U,

- туй, )i T

и + и + и j TH

де k

и мАк-с номинальное напряжение сети и макси- .2/5(u4.tf - и)

УЛВ + Ugc + Uc/

мальное напряжение

управления;

номер фазы преобразокателя.

..

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ компенсации неканонических гармоник выпрямленного напряжения | 1986 |

|

SU1415374A1 |

| Устройство для контроля и настройки систем импульсно-фазового управления вентильными электроприводами | 1985 |

|

SU1339501A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1169167A1 |

| Устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1363405A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1425832A1 |

| Устройство для управления процессом намотки | 1986 |

|

SU1390618A1 |

| Устройство для симметрирования токов трехфазных четырехпроводных сетей | 1990 |

|

SU1758773A1 |

| Преобразователь кода в угловое положение вала | 1987 |

|

SU1499500A1 |

Изобретение относится к электротехнике и может быть использовано в преобразовательной технике для создания устройств управления выпрямителями, к которым предъявляются высокие требования по качеству выходного напряжения. Цель изобретения - комплексное эффективное снижение низкочастотных помех в выпрямленном напряжении, обусловленных помехами питающей сети. Специфика способа управления вентильными преобразователями состоит в том, 4 io для формирования угла включения вентилей, подключенных к 1-й фазе трехфазной сети с амплитудами линейных напряже:ний Аб бс Сй измеряют амплитуды линейных напряжений U;,, U;, U; и длительность периода сети Т, задают номинальную длительность периода сети Тц и для каждого из напряжений сети по заданному напряжению управления Uu (Нормируют угол включения вентилей. . i (Л

N

ni

| Устройство для управления вентильным преобразователем | 1981 |

|

SU980245A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сидоренко В.А | |||

| и др | |||

| Повышение точности многоканальных систем им- пульсно-фазового управления | |||

| - В кн | |||

| Электротехническая промышленность | |||

| Сер | |||

| Преобразовательная техника | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-02-15—Публикация

1986-07-14—Подача