11

Изобретение относится к вычислительной технике и может быть использовано в специа.иизированных вычислителях при аппаратной реализации элементарных функций. .

Целью изобретения является расширение класса решаемых задач за счет возможности вычисления корня R-й степени (,3,...), возведения числа в R-ю степень, логарифмирования и потенциирования чисел.

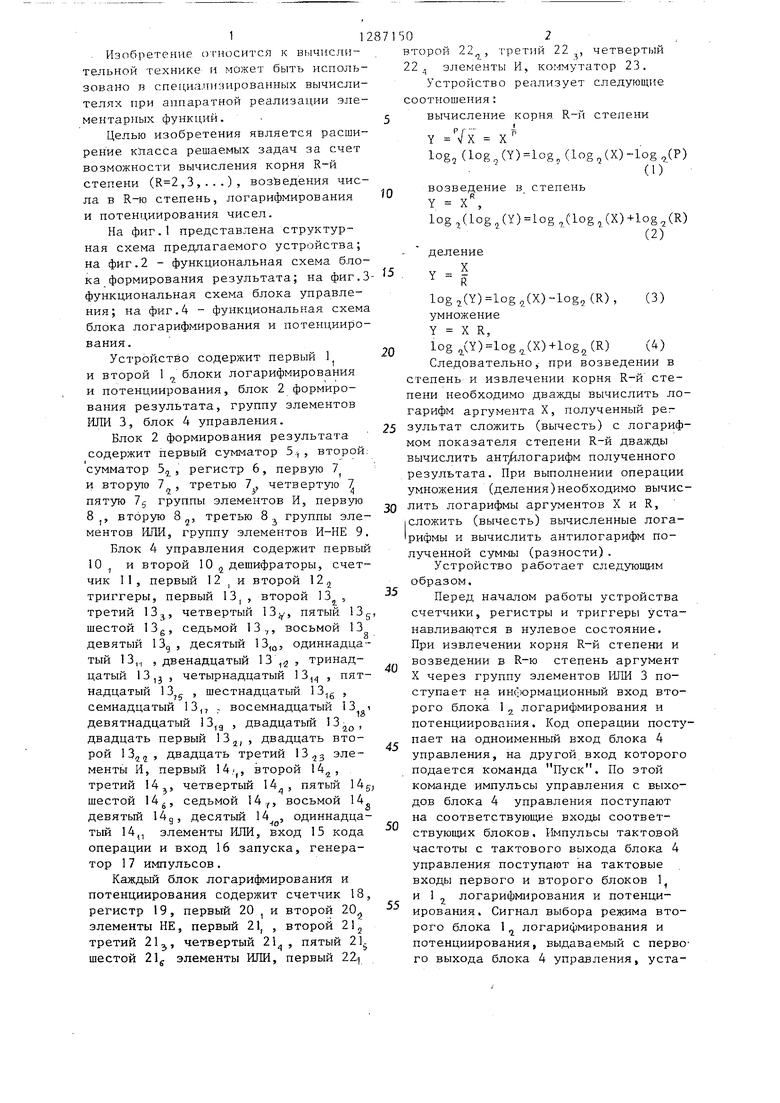

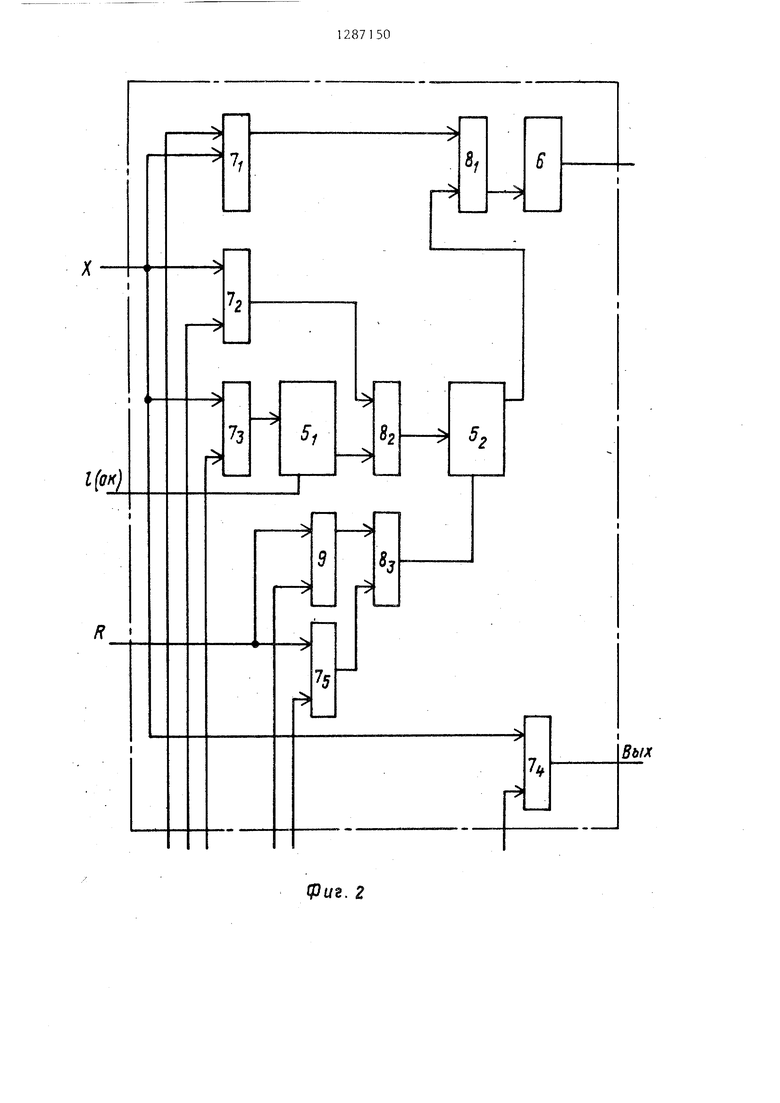

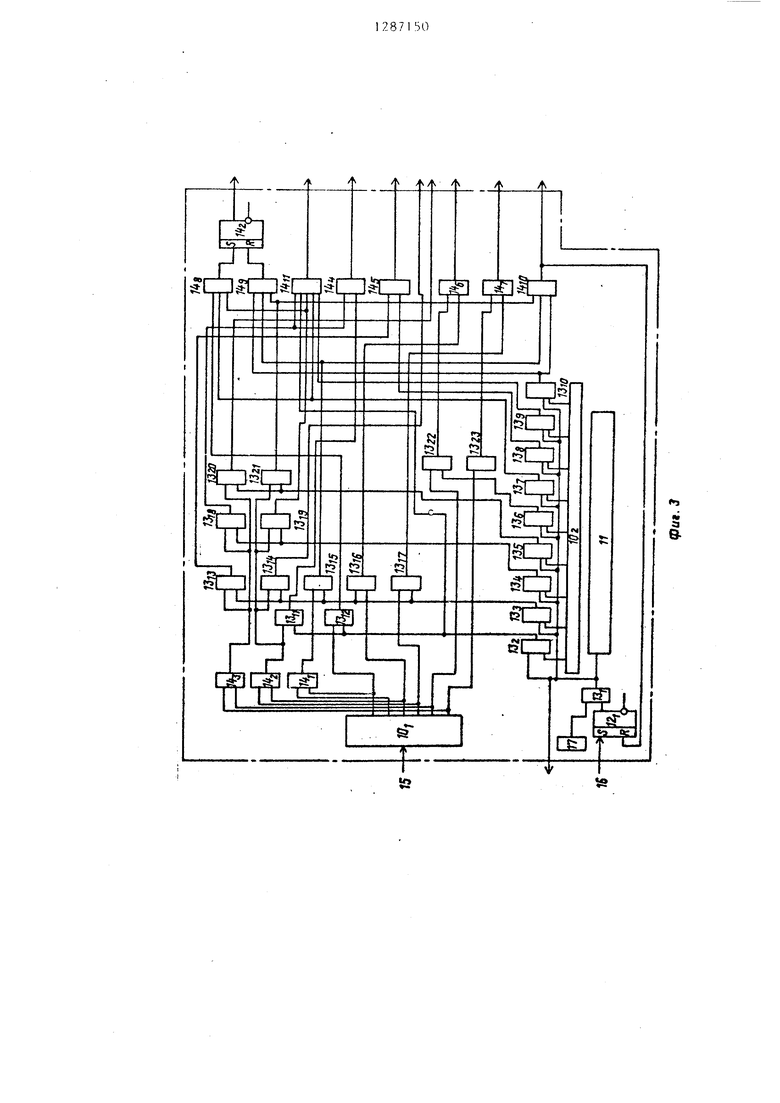

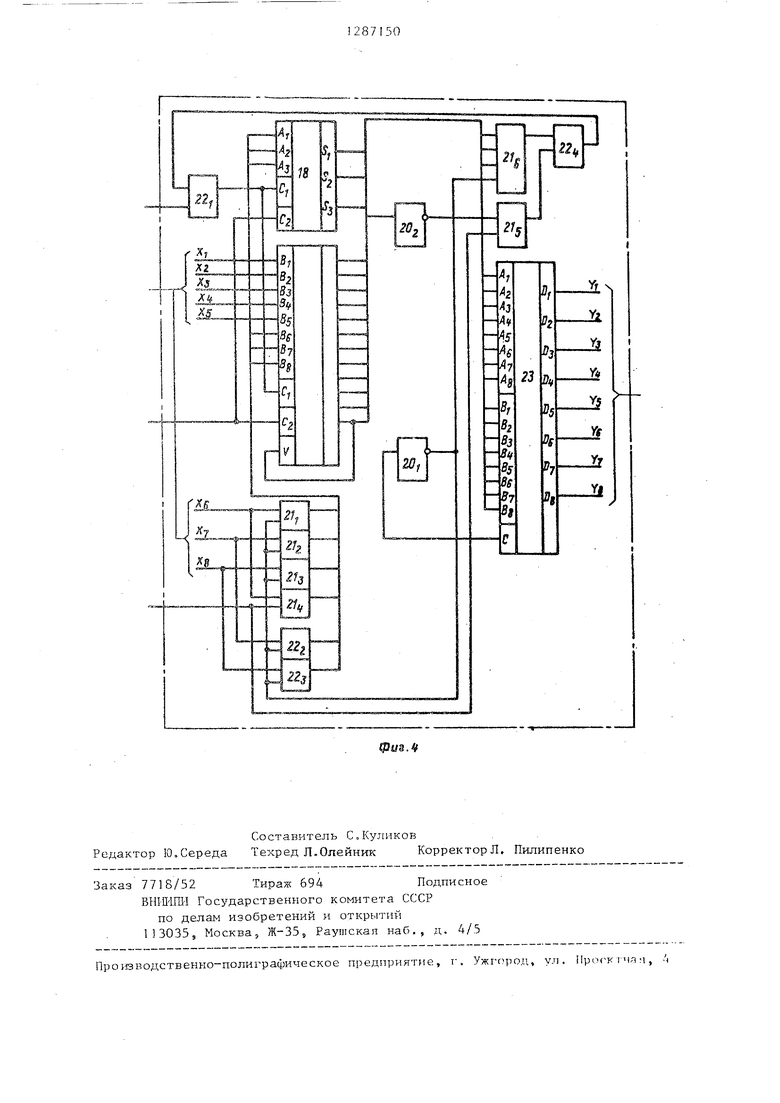

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - функциональная схема блока формирования результата; на фиг.З функциональная схема блока управления ; на фиг.4 - функциональная схема блока логарифмирования и потенциирования.

1

Устройство содержит первый 1 и второй 1 блоки логарифмирования и потенциирования, блок 2 формирования результата, группу элементов ИЛИ 3, блок 4 управления.

Блок 2 формирования результата содержит первый сумматор 5/, , второй сумматор 5,;,, регистр 6, первую 7 и вторую 7 , третью 7, четвертую 7 пятую 7 группы элементов И, первую 8 J, вторую третью 8, группы элементов ИЛИ, группу элементов И-НЕ 9.

Блок 4 управления содержит первый 10 и второй 10 2 дещифраторы, счетчик 11, первый 12 , и второй 122 триггеры, первый 13, , второй 13 , третий 13j, четвертый 13, пятый 13g шестой 13g, седьмой 13,, восьмой 13 девятый 13д , десятый 13,, одиннадцатый 13,., , двенадцатый П тринад„ I глw 1 П

цатыи 13,j , четырнадцатый 13, , пятнадцатый 13jj , шестнадцатый , семнадцатый 13,, , восемнадцатый 13 девятнадцатый 3,д , двадцатый 13, двадцать первый 13,j, , двадцать второй 1 , двадцать третий 13,j3 элементы И, первый , второй 14,., третий 14, четвертый „ , пятьш 14 шестой 14J, седьмой 14, восьмой 14 девятый 14д, десятьш 14 , одиннадцатый 14,, элементы ИЖ, вход 15 кода операции и вход 16 запуска, генератор 17 импульсов.

Каждый блок логарифмирования и потенциирования содержит счетчик 18, регистр 19, первый 20 , и второй 20,, элементы НЕ, первый 21, , второй 2I,j третий 2Ц, четвертый 21, пятый 21- шестой элементы ИЛИ, первый 22

502

второй 22, третий 22 , четвертый 22,, элементы И, коммутатор 23.

Устройство реализует следующие соот юшения :

вычисление корня R-й степени

Y 7Х Х

log, (log (Y)log(log (X)-log (Р)

(1)

возведение в степень Y Х log(log(Y)log,(log(X)+log(R)

(2) - деление

у X R

5

Л

и

(3)

log2(Y)log2(X)-log,,(R), умножение Y X R,

log(Y)log(X)+log,,(R) (4) Следовательно, при возведении в степень и извлечении корня R-й степени необходимо дважды вычислить логарифм аргумента X, полученный результат сложить (вычесть) с логарифмом показателя степени R-й дважды вычислить антилогарифм полученного результата. При выполнении операции умножения (деления)необходимо вычислить логарифмы аргументов X и R, сложить (вычесть) вычисленные логарифмы и вычислить антилогарифм полученной суммы (разности).

Устройство работает следующим образом.

Перед началом работы устройства счетчики, регистры и триггеры уста- навливак)тся в нулевое состояние. При извлечении корня R-й степени и возведении в R-ю степень аргумент X через группу элементов IfflH 3 поступает на ин(;)ормационный вход второго блока 1 ,, логарифмирования и потенциирования. Код операции поступает на одноименный вход блока 4 управления, на другой вход которого подается команда Пуск. По этой команде импульсы управления с выходов блока 4 управления поступают на соответствующие входы соответствующих блоков. Импульсы тактовой частоты с тактового выхода блока 4 управления поступают на тактовые входы первого и второго блоков 1 и логарифмирования и потенциирования. Сигнал выбора режима второго блока 1 логарифмирования и потенциирования, выдаваемый с перво го выхода блока 4 управления, уста

навливается раииым нулю. По управляющему сигналу СН,,, поступающему на стробируюишй второго блока

1 логарифмирования и потенциирова- ння, вычисляется двоичный логарифм арг умента X F lo-g,j(X) и выдается

на вход первого аргумента блока 2 формирования результата. Логарифм аргумента представляется в виде характеристики и мантиссы, т.е. ока зывается дробным. При вычислении корня R-й степени и возведении в R-io степень аргумент необходимо прологарифмировать дважды, т.е. необходимо вычислить двоичный логарифм от . двоичного логарифма аргумента X Однако вычисленный, логарифм оказывается дробным, а блок логарифмирования вычисляет двоичный логарифм целого числа. Для представления числа F целым умножим и разделим его на

2, где I - количество разрядов матиссы, т.е.:

Н --Т-, F F-2 ,

log(H) 1о&,(|г) logjF )(5)

С этой целью целое число пере- дается на выход итерации блока 2 фомирования результата и на вторые входы элементов ИЛИ группы элементов ИШ-1, с выхода которых на вход аргумента второго блока 12 -логариф- мирования и потенциирования. Одновременно на вход аргумента первого блока 1 , логарифмирования и потенциирования поступает число R, Значение сигнала выбора режима второго блока 12 логарифмирования и потен- циирорания не изменяется, а первого постоянно равно нулю. По сигналам (СК и СН ), поступающим на строби- рующие входы второго 1j и первого 1 , блоков логарифмирования и потенциирования, вычисляются двоичные логарифмы чисел F и R, которые подаются на входы блока 2 формирования результата, на третий вход которого поступает обратный код числа 1. В зависимости от кода вычисляемой функции блок управления выдает управляющие импульсы, по которым в блке 2 формирования результата произ- водится вычисление по соотношениям (5), (1) и (2). Следовательно в блоке 2 формирования результата произ

5

О -5 0

5

5 О 0 5

5

50

водится дважды операция вычитания или вычитание и сложение, причем вычитание заменяется сложением в обратном коде, т.е.

,(log(log,(Y))log(F)- ,{R),(6)

где F F-2 logjX) 2

Результат, полученный в соответствии с выражением (6), необходимо дважды пропотенциировать.

С этой целью полученный результат в виде характеристики и мантиссы с выхода итерации блока 2 формирования результата через группу элементов ИЛИ поступает на вход аргумента второго блока Ij логарифмирования и потенциирования. Сигнал выбора режима работы устанавливается равным единице, по сигналу СН вычисляется антилогарифм, который поступает на вход блока 2 формирования результата. Полученное значение по сигналу с выхода блока 4 управления, с выхода итерации блока 2 формирования результата через группу элементов ИЛИ поступает на вход аргумента второго блока 1,2 логарифмирования и потенци- ированр я. Значение сигнала Z не изменяется, а по сигналу СН производится повторное вычисление антилогарифма . Вычисленное значение Y поступает на вход блока 2 формирования результатаi По сигналу с выхода блока 4 управления значение Y выдается на зыход результата блока 2 формирования результата и на выход устройства .

Операции деления и умножения выполняются аналогичным образом. Отличие состоит в том, что логарифмы чисел X и R и антилогарифмы вычис - ляются один раз.

При выполнении операций логарифмирования и потенциирования вычисленное значение логарифма или антилогарифма с выходов блоков 1 логарифмирования и потенциирования выдается на входы блока 2 формирования результата и затем на выход устройства .

Формула изобретения

Устройство для вычисления функций, содержащее блок формирования результата, содержащий два сумматора и регистр и блок управления, отличающееся тем, что, с целью

расширения класса решаеьгых задач за счет возможности вычр слення корня R-H степени ( ;. 3 ; , с . ) , возведени числа в R-ю степень, погарифмнрова- кия и потенциирования чисел в него дополнительно введены два блока логарифмирования и потенциирования и группа элементов ИЛИ, З- в блок формирования результата дополнительно введены пять групп элементов И, три группы элементов ШЖ,, группа зла- ментов И-НЕ,, причем входы аргумента устройства соединены с первы: ш входами элементов ШШ группы, выходы которых соединень с входом аргумента второго блока логарифмирова- шiя и потенциирования5 тактовые вхо- дь первого и второго блоков логарифмирования и 11отенц 1ирова.ния объединены и соединеьгь; с тактовым выходом блока управления,, с.тробирующрш входы первого и второго блоков логарифмирования и потенциирования соединены соответственно с первым и вторым синхронизирующими выходами бл о- ка управления5 вход режима второго блока лoгapиф мpoвaния и потенциирования соединен с одноименным выходом блока упразлвьтя, вход выбора реж1-1ма первого блока логариф м-1рования и потенциирования соединен с входом логического нуля устройства, входы первого, второго и третьего операндов блока форкирова- ния результата соединены с выходами второго блока логарифмироваш-1я и потенциироваьшяS первого блока логарифмирования и потенциирования и входом коррекции устройства соответственно, с первого по шестой выходы управления формированием результата блока управления соединены с соот- ветствуюащми одноименными входами блока формирования реззшьтата,, выходы итерахщи блока формирования, результата соединены с вторыми входами элементов ЖИ группы, выход результата блока формирования результата является одноименным выходом устройства, входы кода опера- дни и запуска устройства соединены с одноименными входами блока управ- леьшя, содержащего генератор импульсов, дна дешифратора в два триг- repaj счетчик, двадцать три элемента И, одиннадцать элементов ИЛЙ причем входы запуска и кода операции блока управления соединены с входом установки первого триггера и входом

.

71506

первого дешифратора соответственно, выход первого т ригтера соединен с первым входом первог о элемента П второй вход которого соединен с вы- 5 ходом генератора импульсовj выход первого элемента i соединен со счетным входом счетчика и с первыми вхо- даг-ш с второго по десятый элементов

5

0

5

0

Hj вторые входы которых соединены с выходами второго дешифратора, вход которого соединен с выходом счетчика выход второго элемента И соеди- .. нвн с первыми входами одиннадцатого и двенадцатого элементов И, выход третьего элемента И соединен с первыми входами с тринадцатого по семнадцатый элементов И, выход четвертого элемента И соединен с первыми входа- ш восемнадцатого и девятнадцатого элементов И, выход нятого элемента И соединен с первыми входами двадцатого и двадцать первого элементов И, выход шестого элемента И соедиг Р5ен с первыми входами двадцать второго и двадцать третьего элементов И, первый выход первого дешифратора соединен с вторьм входом двенадцатого элемента И и первым входом первого, элемента ИЛИ, второй вход кот о- рого соединен с вторым выходом первого дешифратора, третий выход первого дешифратора соединен с вторым входом шестнадцатого элемента И и первьм входом второго элемента ИЛИ,

.5 второй вход которого соединен с вторым входом семнадцатого элемента И и четвертым выходом первого дешифратора, пятый выход первого дешифратора соединен с вторым входом

0 двадцать второго элемента И и первым входом третьего элемента ИЛИ, второй вход которого соединен с вторым входом двадцать третьего элемента И и с шестым выходом первого де5 шифратора, выход первого элемента ИШ1 соединен с вторым входом пятнадцатого элемента И, выход второго элемента ИЛИ соединен с вторыми входами одиннадцатого, четырнадца0 того, девятнадцатого и двадцать первого элементов И, выход третьего элемента ИЛИ соединен с вторыми входами тринадцатого, восемнадцатого и двадцатого элементов И, выходы

55 одиннадцатого и восемнадцатого элементов И соединены соответственно с первым и вторым входами четвертого элемента И, первый и второй входы пятого элемента ILHi соединены с

71

выходами соответственно тринадцатого и восьмого элементов И, первый и второй входы шестого элемента ИЛИ соединены с выходами соответственно шестнадцатого и двадцать второго элементов И, первый и второй входы седьмого элемента ИЛИ соединены с выходами соответственно семнадцатого и двадцать третьего элементов И, первый, второй и третий входы восьмого элемента ИЛИ соединены с выходами соответственно двенадцатого, седьмого и девятнадцатого элементов И, с первого по третий входы девятого элемента ИЛИ соединены с выходами соответственно десятого, пятнадцатого и двадцать первого элементов И, с первого по третий входы десятого элемента ИЛИ соединены соответственно с выходами двадцать первого, пятнадцатого и десятого элементов И, с первого по четвертый входы одиннадцатого элемента ИЛИ соединены с выходами соответственно восемнадца

того, второго, девятнадцатого, седьмого и девятого элементов И, выходы восьмого и девятого элементов ИЛИ соединены с входами соответственно установки и сброса второго триггера выход которого соединен с выходом выбора режима блока управления, выходы четвертого и одиннадцатого элементов ШШ соединены соответственно с вторым и первым синхронизирующими выходами блока управления, тактовый выход которого соединен с выходом первого элемента И, выход десятого элемента ИЛ1-1 соединен с входом сброса первого триггера, выходы пятого элемента ИЛИ, четырнадцатого элемента И, двадцатого элемента И, шестого элемента ИЛИ, седьмого элемента ИЛИ, десятого элемента ИЛИ соединены с первого по шестой выходами, управления формированием результата

508

блока управления соответственно, причем входа первого операнда блока форм1 1рования результата соединены с первыми входами элементов И групп с первой по четвертую, входы второго операнда блока формирования результата соединены с первыми входами элементов И пятой группы и с первыми входами элементов И-НЕ группы, выходы элементов И первой и второй групп соединены с первыми входами элементов ИЛИ соответственно первой и второй групп, выходы элементов И третьей группы соединены с входами первого слагаемого первого сумматора, вход второго слагаемого которого соединен с входом третьего операнда блока формирования результата, выходы первого сумматора соединены с вторыми входами элементов ИЛИ второй группы, выходы которых соединены с входами первого слагаемого второго сумматора, выходы которого соединены с вторыми входами элементов ИЛИ первой группы, выходы которых соединены с информационными входами регистра, выход которого соединен с выходом итерации блока формирования результата, вход второго слагаемого .-второго сумматора соединен с выходами элементов ИЛИ третьей группы, первые входы которых соединены с выходами элементов И-НЕ группы, вторые входы элементов ИЛИ группы соединены с выходами элементов И пятой группы, с первого по шестой входы управления формированием результата блока формирования- результата соединены с вторыми входами соответственно элементов И первой, второй и третьей групп, элементов И-НЕ группы, элементов И пятой группы и элементов И четвертой группы,выходы элементов И четвертой группы соединены с в ьк од ом результата блока формирования результата.

Фи2. 2

И

Составитель С.Куликов Редактор Ю.Середа Техред Л.Олейнкк КорректорЛ. Пилипенко

Заказ 7718/52 Тираж 694Подписное

BHimro-I Государственного комитета СССР

по делам изобретений и открытий ПЗОЗЗэ Москва, Ж-ЗЗ, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Ирогктчап, ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмов чисел | 1981 |

|

SU972504A1 |

| Функциональный преобразователь | 1986 |

|

SU1397905A1 |

| Устройство для логарифмирования | 1980 |

|

SU959072A1 |

| Устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1363405A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Система оптимизации управления непосредственно и косвенно управляемыми объектами | 1982 |

|

SU1080117A1 |

| Функциональный логарифмический преобразователь | 1987 |

|

SU1462303A1 |

Изобретение относится к области вычислительной техники и может быть применено в качестве функциональных расширителей в составе больших ЭВМ Код операции Пуск или в специализированных вычислителях при аппаратной реализации элементарных функций. Целью изобретения является расширение класса решаемых задач за счет возможности извлечения корня R-й степени (,3,...), возведение числа в R степень, деление и умножение чисел. Устройство содержит первый и второй блоки логарифмирования и потенциирования, блок 2 формирования результата, группу элементов ИЛИ 3, блок 4 управления. Устройство реализует элементарные функции путем замены прямых пре- .образований над аргументами преобразованием их логарифмов с последующим потенциированием результата. 4 ил. (О (Л

| Устройство для вычисления логарифмов чисел | 1981 |

|

SU972504A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Цифровое устройство для извлечения квадратного корня | 1978 |

|

SU763893A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления элементарных функций | 1974 |

|

SU560229A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-04-29—Подача