1

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике для снятия частотных характеристик сигналов в области низких частот.

Целью изобретения является уменьшение неравномерности сдвигов по частоте между сигналами в выходном многочастотном сигнале.

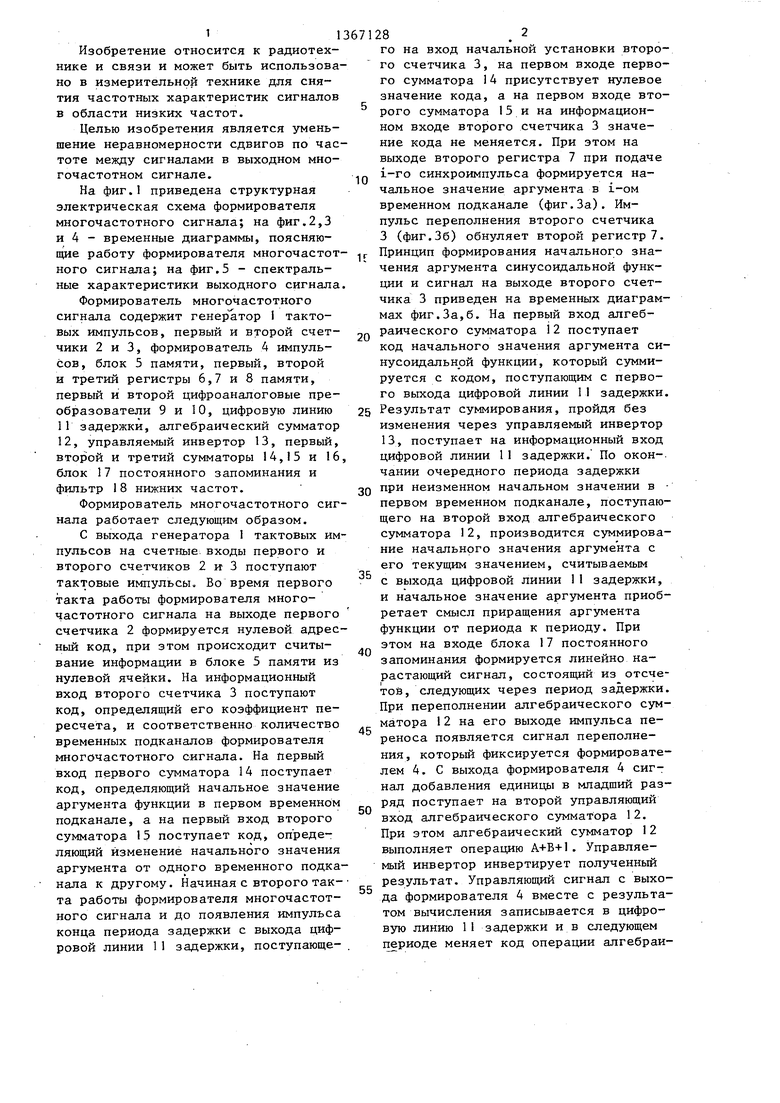

На фиг.1 приведена структурная электрическая схема формирователя многочастотного сигнала; на фиг.2,3 и 4 - временные диаграммы, поясняющие работу формирователя многочастот ного сигнала; на фиг.5 - спектральные характеристики выходного сигнала

Формирователь многочастотного сигнала содержит генер атор 1 тактовых импульсов, первый и второй счет- чики 2 и 3, формирователь 4 импульсов, блок 5 памяти, первый, второй и третий регистры 6,7 и 8 памяти, первый и второй цифроаналоговые преобразователи 9 и 10, цифровую линию 11 задержки, алгебраический сумматор 12, управляемый инвертор 13, первый, второй и третий сумматоры 14,15 и 16 блок 17 постоянного запоминания и фильтр 18 нижних частот.

Формирователь многочастотного сигнала работает следующим образом.

С выхода генератора I тактовых импульсов на счетные; входы первого и второго счетчиков 2 и 3 поступают тактовые импульсы. Во время первого такта работы формирователя многочастотного сигнала на выходе первого счетчика 2 формируется нулевой адресный код, при зтом происходит считывание информации в блоке 5 памяти из нулевой ячейки. На информационный вход второго счетчика 3 поступают код, определящий его коэффициент пересчета, и соответственно количество временных подканалов формирователя многочастотного сигнала. На первый вход первого сумматора 14 поступает код, определяющий начальное значение аргумента функции в первом временном подканале, а на первый вход второго сумматора 15 поступает код, определяющий изменение начального значения аргумента от одного временного подканала к другому. Начиная с второго такта работы формирователя многочастотного сигнала и до появления импульса конца периода задержки с выхода цифровой линии 11 задержки, поступающе-

0

71

n 5 Q

5

5

0

5

28. 2

го на вход начальной установки второго счетчика 3, на первом входе первого сумматора 14 присутствует нулевое значение кода, а на первом входе второго сумматора 15 и на информационном входе второго счетчика 3 значение кода не меняется. При этом на выходе второго регистра 7 при подаче i-ro синхроимпульса формируется начальное значение аргумента в i-ом временном подканале (фиг.За). Импульс переполнения второго счетчика 3 (фиг.Зб) обнуляет второй регистр 7. Принцип формирования начального значения аргумента синусоидальной функции и сигнал на выходе второго счетчика 3 приведен на временных диаграммах фиг.За,б. На первый вход алгебраического сумматора 12 поступает код начального значения аргумента синусоидальной функции, который суммируется с кодом, поступающим с первого вьпсода цифровой линии II задержки. Результат суммирования, пройдя без изменения через управляемый инвертор 13, поступает на информационный вход цифровой линии 1 1 задержки. По окон-, чании очередного периода задержки при неизменном начальном значении в - первом временном подканале, поступающего на второй вход алгебраического сумматора 12, производится суммирование начального значения аргумента с его текущим значением, считываемым с выхода цифровой линии 11 задержки, и начальное значение аргумента приобретает смысл приращения аргумента функции от периода к периоду. При этом на входе блока 17 постоянного запоминания формируется линейно нарастающий сигнал, состоящий из отсчетов, следующих через период задержки. При переполнении алгебраического сумматора 12 на его выходе импульса переноса появляется сигнал переполнения, который фиксируется формирователем 4. С выхода формирователя 4 сигнал добавления единицы в мпадший разряд поступает на второй управляющий вход алгебраического сумматора 12. При этом алгебраический сумматор 12 выполняет операцию А+В+1. Управляемый инвертор инвертирует полученный результат. Управляющий сигнал с выхода формирователя 4 вместе с результатом вычисления записывается в цифровую линию 11 задержки ив следующем периоде меняет код операции алгебраи31

ческого сумматора 12 с операции суммирования на операцию вычитания, которая выполняется до следующего появления сигнала переполнения. После

ЭТОГО выполняются операции А-В-1, а управляемый инвертор 13 инвертирует полученный результат. В следующем периоде управляющий сигнал меняет код операции алгебраического сумматора 12 с операции вычитания на операцию суммирования. Принцип формирования аргумента синусоидальной функции в одном временном подканале показан на фиг.2а,б. В остальных временных под- каналах в периоде задержки изменение значения аргумента происходит аналогично (фиг.4). Сигнал с выхода блока 17 постоянного запоминания поступает на вход первого цифроакапогового пре- образователя 9 и на второй вход третьего сумматора 16. Рециркуляционный накопитель, состоящий из третьего сумматора 16 и третьего регистра 8, производит суммирование отсчетов си- нусоидальных колебаний, сформированных во всех временных подканалах внутри каждого периода. При этом код временных подканалов преобразуются в один канал. Третий регистр 8 осу- ществляет задержку сигнала на один временной подканал. По окончании операции суммирования отсчетов синусоидальных колебаний вЬ всех временных подканалах в каждом из периодов третий регистр 8 устанавливается в нуль управляющим игналом, поступающим с выхода второго счетчика 3 на вход установки нуля третьего регистра 8. По отрицательному фронту того же сиг- нала, подаваемого на вход записи первого регистра 6, показанного на фиг.Зб, происходит перезапись информации с выхода третьего сумматора 16 в регистр 6. Сигнал с выхода регист- ра 6 . поступает на вход второго циф- роаналогового преобразователя 10, а с выхода-цифроаналогового преобразователя 10 через фильтр 18 нижних частот - на третий выход формирователя многочастотного сигнала. Принцип фор- мирования спектра сигналов на выходе второго цифроаналогового преобразователя 10 и на выходе фильтра нижних частот 18 показан на фиг.5а,б. Фор мула изобретения

Формирователь многочастотного сигнала, содержащий последовательно сое28

диненные первьш счетчик, блок памяти и второй счетчик, последовательно соединенные блок постоянного запоминания и первый цифроаналоговый преобразователь, выход которого является первым выходом формирователя многочастотного сигнала, последовательно соединенные первый регистр памяти и второй цифроаналоговый преобразователь, формирователь импульсов и генератор тактовых импульсов, отличающийся тем, что, с целью уменьшения неравномерности сдвигов по частоте между сигналами в выходном многочастотном сигнале, в него введены последовательно соединенные цифровая линия задержки, алгебраический сумматор и управляемый инвертор, последбвательно соединенные первый сумматор, второй сумматор и второй регистр памяти, последовательно соединенные третий сумматор и третий регистр памяти, выход которого соединен с первым входом третьего сумматора, и фильтр нижних частот, вход которого соединен с выходом второго цифроаналогового преобразователя, счетные входы первого и второго счетчиков объединены с входами синхронизации второго и третьего регистров памяти, формирователя импульсов и цифровой линии задержки и соединены с выходом генератора тактовых импульсов, второй и третий выходы блока памяти соединены с первьми входами соответственно первого и второго сумматоров, второй вход первого сумматора объединен с вторым входом алгебраического, сумматора и соединен с выходом второго регистра памяти, выход управляемого инвертора соединен с информационными входом цифровой линии задержки и с адресным входом блока постоянного запоминания, выход которого соединен с вторым входом третьего сумматора, выход третьего сумматора соединен с информационным входом первого регистра памяти, вход записи которого объединен с входами установки нуля второго и третьего регистров памяти и соединен с выходом второго счетчика, вход начальной установки второго счетчика соединен с вторым выходом цифровой линии задержки, третий выход которой соединен с первым управляющим входом алгебраического сумматора, выход импульса переноса алгебраического сум51367128 ,

матЬра соединен с информационным вхо- гебраического сумматора, выход блока дом формирователя импульсов, выход постоянного запоминания является вто- которого соединен с управляющим вхо- рым выходом формирователя многочас- дом управляемого инвертора, с управ- тотного сигнала, а выход фильтра нижних частот - третьим выходом формирователя многочастотного сигнала.

ляющим входом цифровой линии задержки и с вторым управляющим входом ал

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь многочастотного сигнала | 1987 |

|

SU1406708A1 |

| Формирователь многочастотного сигнала | 1986 |

|

SU1401554A1 |

| Генератор синусоидальных сигналов | 1990 |

|

SU1734189A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ ДЛЯ МНОГОЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2014 |

|

RU2566961C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ МНОГОЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2013 |

|

RU2536385C1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Функциональный преобразователь | 1986 |

|

SU1403078A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

Изобретение м.б. использовано в измерительной технике для снятия частотных х-к сигналов в области НЧ. Цель изобретения - уменьшение неравномерности сдвигов по частоте между сигналами в выходном многочастотном сигнале. Форм-ль содержит г-р 1 тактовых импульсов, счетчики 2 и 3, формирователь 4 импульсов, блок 5 памяти, регистры 6-8 памяти, ЦАП 9 - 10, цифровую линию II задержки, ал- гебраич. сумматор 12, управляемый инвертор 13, сумматоры 14 - 16; блок 17 постоянного запоминания и фильтр с (О

idh 1

fxf

«7

| Генератор спектра | 1982 |

|

SU1072244A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой генератор синусоидальных колебаний | 1983 |

|

SU1133646A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-15—Публикация

1985-12-06—Подача