LL

05

о 00

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике для снятия частотных характеристик различных устройств (например, фильтров, использующихся для реализации преобразования Фурье).

Целью изобретения является обеспечение независимой регулировки амплитуды каждой спектральной составляющей выходного многочастотного сигнала.

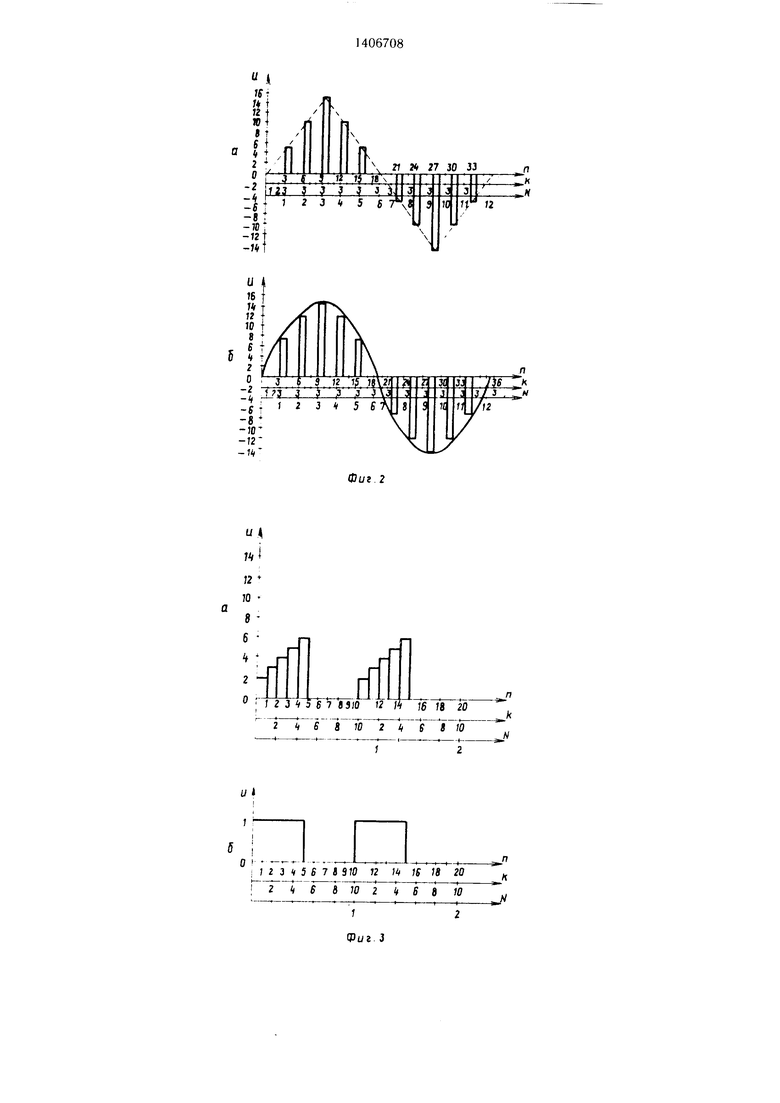

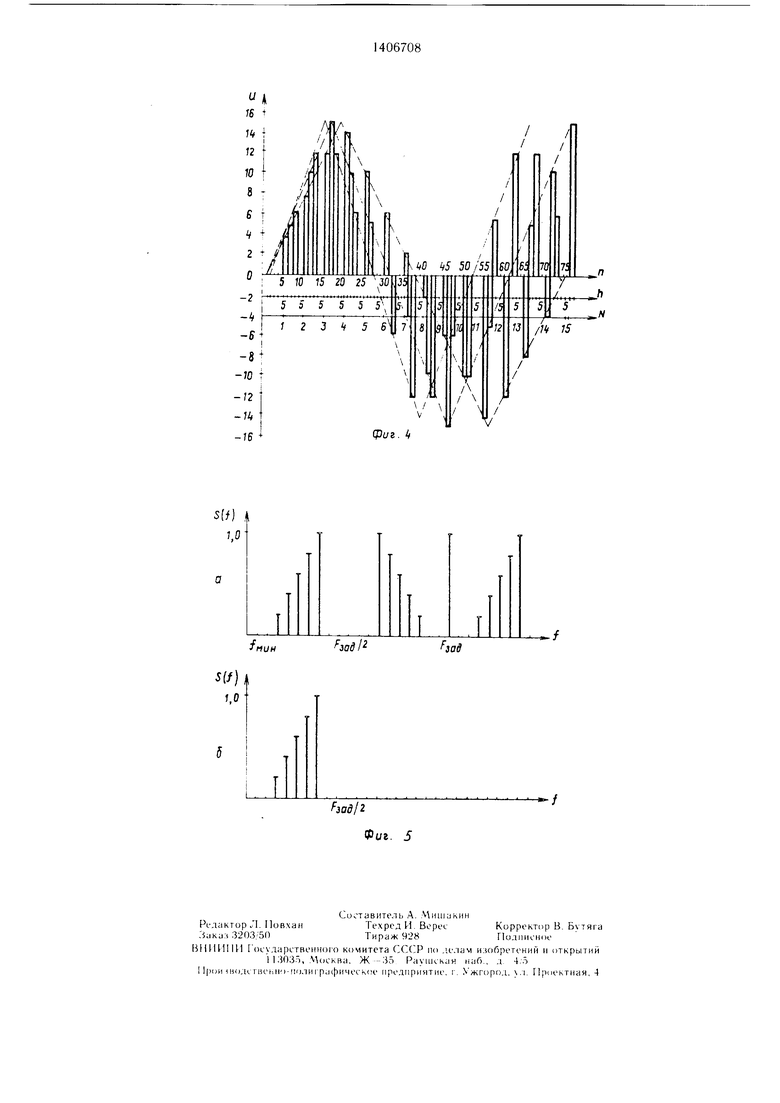

На фиг. 1 приведена структурная электрическая схема формирователя многочастотного сигнала; на фиг. 2-4 - временные диаграммы, поясняющие работу формирователя многочастотного сигнала; на фиг. 5 - спектральные характеристики выходного сигнала.

Формирователь многочастотного сигнала содержит генератор 1 тактовых импульсов, nepiibiii и второй счетчики 2 и 3, формиро- ваге.чь 4 импульсов, блок 5 памяти, третий, первый и второй регистры 6, 7 и 8 памяти, второй и нервьп цифроаналоговые преобразователи 9 и 10, цифровую линию 11 задержки, ал|-ебраический сумматор 12, управляемый инвертор 13, первый, второй и третий сумматоры 14, 15 и 16, первый и второй блоки 17 и 18 постоянного запоминания, фильтр 19 нижних частот и перемножитель 20.

Формирователь многочастотно1 о сигнала 1)аботает следующим образом.

( выхода генератора 1 тактовых импульсов па счетные входы первого и второго счетчиков 2 и 3 поступают тактовые им- . Во вре.ми первого такта работы формирователя многочастотного сигнала на выходе перво1Ч) счетчика 2 формируется нуле- Boii адресиьи код, при это.м происходит считывание информации из блока 5 намяти из Hy.ieiuni ячейки. На кодовый вход второго счетчика 3 поступает код, определяющий его коэффициент пересчета и, соответственно, к().1пчество времен}1ых подканалов формиро- вате.1я мпогочастотного сигнала. На первый вход первого сумматора 14 поступает код, определяющий начальное значение аргумента функции в первом вре.менном нодканале, а на второй вход второго су.мматора 15 поступает код, определяющий изменение начального значения аргумента от одного временного подканала к другому. Начиная со второго такта работы формирователя много- частотногч) сигнала я до появления импульса конца периода задержки с выхода цифровой .тинип 1 1 задержки, поступающего на вход начальной установки второго счетчика 3 на нервом входе первого су.мматора 14 присутствует пулевое значение кода, а на втором входе второго сумматора 15 и на кодовом входе второго счетчика 3 значение кода не меняется. При этом на выходе пер- вог о регистра 7 при подаче i-ro синхроимпульса формируется начальное значение аргумента в i-M временном подканале (фиг. За),

0

5

0

5

0

5

0

5

0

5

где k - номер временного подканала, импульс переполнения второго счетчика 3 (фиг. 3 б) обнуляет первый регистр 7. Принцип формирования начального значения аргумента синусоидальной функции и сигнала на выходе второго счетчика 3 приведен на временных диаграммах (фиг. 36), где п - номер текущей дискреты. На вход алгебраического сумматора 12 поступает код начального значения аргумента синусоидальной функции, который суммируется с кодом, поступающим с выхода цифровой линии 11 задержки. Результат суммирования, пройдя без изменения через управляемый инвертор 13, поступает на вход цифровой линии 1 1 задержки. По окончании очередного периода задержки при неизменном начальном значении в первом временном подканале, поступающем на другой вход алгебраического сумматора 12, производится суммирование начального значения аргумента с его текущим значением, считываемым с выхода цифровой линии 11 задержки, и начальное значение аргумента приобретает смысл приращения аргумента функции от периода к периоду. При этом на выходе первого блока 17 постоянного запоминания формируется линейно-нарастающий код, состоящий из отсчетов, следующих через период задержки. При переполнении алгебраического сумматора 12 на его выходе импульса переноса появ:1яется сигнал переполнения, который фиксируется формирователем 4. С выхода формирователя 4 сигнал добавления единицы в младщий разряд поступает на второй управляющий вход алгебраического сумматора 12. При этом алгебраический сумматор 12 выполняет операцию .Л + . Управляемый инвертор 13 инвертирует полученный результат. Управляющий сигнал с выхода формирователя 4 вместе с результатом вычисления записывается в цифровую линию 11 задержки и в следуюп ем периоде меняет код операции алгебраического сумматора 12 с операции суммирования на операцию вычитания, которая выполняется до следующего появления сигнала переполнения. После этого выполняется операция А--В-1, а управляемый инвертор 13 инвертирует полученный результат. В следующем периоде управляющий сигнал меняет код операции алгебраического сумматора 12 с операции вычитания на операцию суммирования. Принцип формирования аргумента синусоидальной функции в одном временном подканале показан на фиг. 2 а, б. В остальных временных подканалах в периоде задержки изменение значения аргумента происходит аналогично (фиг. 4, N - номер периода задержки). Сигнал с выхода первого блока 17 постоянного запоминания поступает на вход перемножителя 20 чисел, представленных цифровым кодом. На другой вход перемножителя 20 при подаче i-ro синхроимпульса поступает цифровой код с выхода

второго блока 18 постоянного запоминания, величина которого соответствует амплитуде спектральной составляющей, сформированной в i-M временном подканале.

Закон изменения амплитуд спектральных составляющих от одного временного подканала к другому представлен в виде цифровых кодов во втором блоке 18 постоянного запоминания. С выхода перемножителя 20 сигнал поступает на вход второго цифроаналогового преобразователя 9 и на другой вход третьего сумматора 16. Рециркуляционный накопитель, состоящий из третьего сумматора 16 и второго регистра 8, производит суммирование отсчетов синусоидальных колебаний, сформированных во всех временных подканалах внутри каждого периода. При этом временные подканалы преобразуются в один канал. Второй регистр 8 осуществляет задержку сигнала на один временной подканал. По окончании операции суммирования отсчетов синусоидальных колебаний во всех временных подканалах в каждом из периодов второй регистр 8 устанавливается в «О сигналом, поступающим с выхода второго счетчика 3 на вход установки нуля второго регистра 8. По заднему фронту того же сигнала, подаваемого на вход записи третьего регистра 6 (фиг. 36), происходит перезапись информации с выхода треьего сумматора 16 в третий регистр 6. Сигнал с выхода третьего регистра 6 поступает на вход первого цифроаналогового преобразователя 10, а с его выхода через фильтр 19 нижних частот на первый выход формирователя многочастотного сигнала. Принцип формирования спектра сигналов на первом выходе формирователя многочастотного сигнала для линейного закона распределения амплитуд спектральных составляющих показан на фиг. 5 а,, б.

На втором выходе формирователя многочастотного сигнала присутствует набор синусоидальных колебаний, а на третьем выходе формирователя многочастотного сигнала - коды набора синусоидальных колебаний.

Формула изобретения

Формирователь многочастотного сигнала, содержащий последовательно соединенные первый счетчик, блок памяти, первый сумматор, второй сумматор, первый регистр памяти, алгебраический сумматор, управляемый инвертор и цифровую линию задержки.

10

15

20

25

30

35

40

45

но соединенные второй регистр памяти, третий сумматор, третий регистр памяти, первый цифроаналоговый преобразователь и фильтр нижних частот, выход которого является первым выходом формирователя многочастотного сигнала, генератор тактовых импульсов, формирователь импульсов, второй счетчик, первый блок постоянного запоминания и второй цифроаналогоиый преобразователь, выход которого является вторым выходом формирователя многочастотного сигнала, при этом счетные входы первого и второго счетчиков объединены с входами синхронизации первого и второго регистров памяти, формирователя импульсов и цифровой линии задержки и соединены с выходом генератора тактовых импульсов, второй и третий выходы блока памяти соединены соответственно с кодовым входом второго счетчика и с вторым входом второго сумматора, второй вход первого сумматора подключен к выходу первого регистра памяти, адресный вход первого блока постоянного запоминания подключен к выходу управляемого инвертора, вход второго регистра памяти подключен к выходу третьего сумматора, вход записи третьего регистра памяти объединены с входами установки ну. neji- вого и второго регистров памяти и подключен к выходу второго счетчика, второй и третий выхрды цифровой линии задержки соединены соответственно с входом начальной установки второго счетчика и с первым управляющим входом а.тгебраического сумматора, выход импульса переноса алгебраического сумматора соединен с информационным входо.м формирователя импульсов, выход которого подключен к другому входу управляемого инвертора, к второму управляющему входу алгебраического сумматора и к управляющему входу циф1)овой линии задержки, вход второго цифроаналогового преобразователя объединен с другим

входом третьего сумматора, отличающийся тем, что, с целью обеспечения независимой регулировки амплитуды каждой спектра. 1ь- ной составляющей выходного многочастотного сигнала, введены последовательно соеди- не)1ные второй блок постоянного запоминания и перемножитель, вход которого соединен с выходом первого блока постоянного запоминания, а выход является третьим выходом формирователя мног очастотного сигнала и подключен к входу второго цифро- аналогового преобразователя, при этом нхол

выход которой подключен к другому входу СП второго блока постоянного запоминания соеалгебраического сумматора, последовательдинен с выходом первого счетчика.

0

5

0

5

0

5

0

5

но соединенные второй регистр памяти, третий сумматор, третий регистр памяти, первый цифроаналоговый преобразователь и фильтр нижних частот, выход которого является первым выходом формирователя многочастотного сигнала, генератор тактовых импульсов, формирователь импульсов, второй счетчик, первый блок постоянного запоминания и второй цифроаналогоиый преобразователь, выход которого является вторым выходом формирователя многочастотного сигнала, при этом счетные входы первого и второго счетчиков объединены с входами синхронизации первого и второго регистров памяти, формирователя импульсов и цифровой линии задержки и соединены с выходом генератора тактовых импульсов, второй и третий выходы блока памяти соединены соответственно с кодовым входом второго счетчика и с вторым входом второго сумматора, второй вход первого сумматора подключен к выходу первого регистра памяти, адресный вход первого блока постоянного запоминания подключен к выходу управляемого инвертора, вход второго регистра памяти подключен к выходу третьего сумматора, вход записи третьего регистра памяти объединены с входами установки ну. neji- вого и второго регистров памяти и подключен к выходу второго счетчика, второй и третий выхрды цифровой линии задержки соединены соответственно с входом начальной установки второго счетчика и с первым управляющим входом а.тгебраического сумматора, выход импульса переноса алгебраического сумматора соединен с информационным входо.м формирователя импульсов, выход которого подключен к другому входу управляемого инвертора, к второму управляющему входу алгебраического сумматора и к управляющему входу циф1)овой линии задержки, вход второго цифроаналогового преобразователя объединен с другим

входом третьего сумматора, отличающийся тем, что, с целью обеспечения независимой регулировки амплитуды каждой спектра. 1ь- ной составляющей выходного многочастотного сигнала, введены последовательно соеди- не)1ные второй блок постоянного запоминания и перемножитель, вход которого соединен с выходом первого блока постоянного запоминания, а выход является третьим выходом формирователя мног очастотного сигнала и подключен к входу второго цифро- аналогового преобразователя, при этом нхол

П второго блока постоянного запоминания соединен с выходом первого счетчика.

А

гИ

12 0 8 - 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь многочастотного сигнала | 1985 |

|

SU1367128A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| Формирователь многочастотного сигнала | 1986 |

|

SU1401554A1 |

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

| Устройство для передачи дискретных сигналов | 1984 |

|

SU1277419A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| РЕЛЕ СИНХРОНИЗАЦИИ | 2003 |

|

RU2231849C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ МОНОИМПУЛЬСНОГО РАДИОЛОКАТОРА | 2005 |

|

RU2287171C1 |

Изобретение относится к области радиотехники и связи и м.б. использовано в измерительной технике для снятия частотны.х х-к различных устр-в. Цель изобретения - обеспечение независимой регулировки амплитуды каждой спектральной составляющей выходного многочастотного сигнала (МЧС). Формирователь Л1ЧС содержит генератор тактовых импульсов 1. счетчики 2, 3, формирова- те. 1ь 4 импульсов, б, юк памяти 5, регистры 6, 7, 8 па.мяти, Ц.ЛП 9, 10, цифровую линию задержки И, а.лгебраический сумматор 12, управляемый инвертор 13, сумматоры 14, 15, 16, б, 1ок постоянного заноминания 17, фильтр нижних частот 19. Постав.пенная н.е,1ь достигается введением в стр-во вторО Ч) б, юка постоянного запоминания 18 и перемножителя 20. Закон изменения амп,:п(туд спектральных составляющих от одного времен- HOI4J подканала к другому представлен в виде таблицы цифровых кодов в блоке постоянного запоминания 18. 5 ил.

1 г 3 fi е 1 6910 гг ;

iteBwzit eiw

u

I

I 1 Z 3 ч 5 Б 7 1310 12 )ii1S 18 20

2 В 2 ifi 8 w

f2

Фиг 3

го

w

J7

k

N

,/

5 ГО :5 20 25

55555 5

Г 2 3 V 5 6 7

J5

фиг.

-yJ 50/55

fO,

6j

70

п

/5

h

/v

;

;j

75

/ / / N|

фиг.

V

| Цифровой генератор синусоидальных колебаний | 1983 |

|

SU1133646A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Формирователь многочастотного сигнала | 1985 |

|

SU1367128A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1987-01-12—Подача