- J- Ч

/5

/V

:о

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации функций ИСКЛЮЧАЮЩЕЕ ИЛИ.

Цель изобретения - расширение функциональных возможностей за счет реализации мажоритарных функций и функций ИСКЛЮЧАЮЩЕЕ ИЛИ.

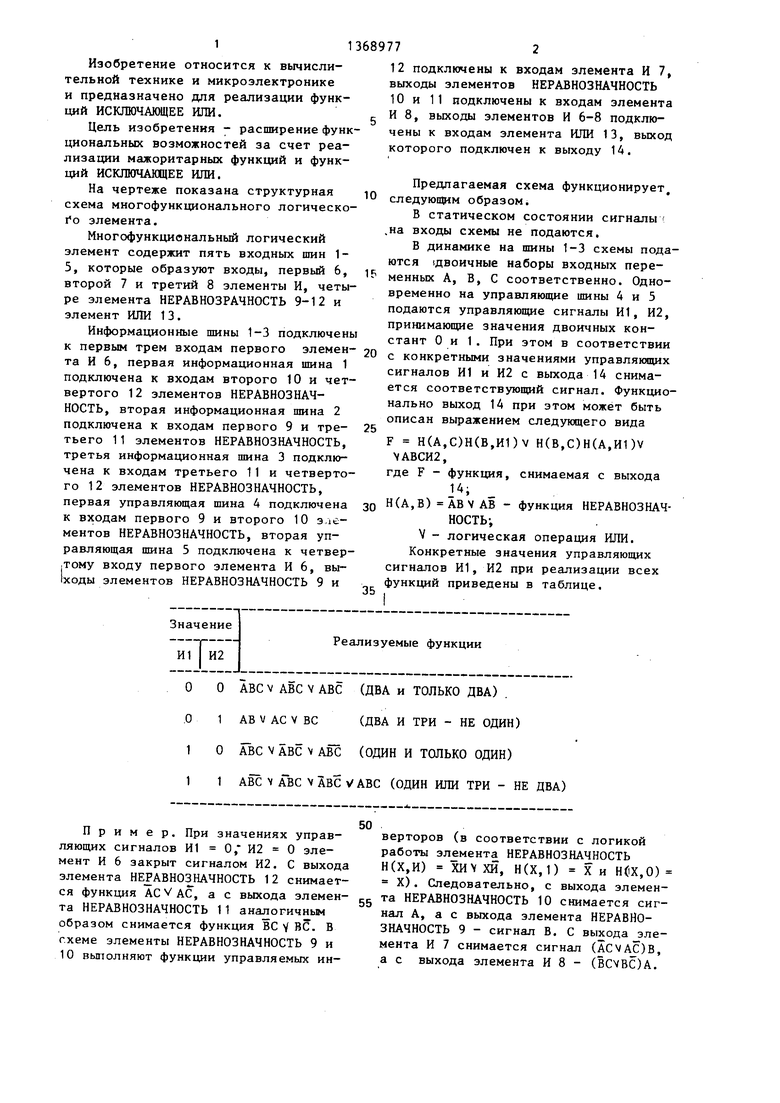

На чертеже показана структурная ю схема многофункционального логического элемента.

Многофункциональный логический элемент содержит пять входных шин 1 - 5, которые образуют входы, первый 6, if второй 7 и третий 8 элементы И, четыре элемента НЕРАВНОЗРАЧНОСТЬ 9-12 и элемент ИЛИ 13.

Информационные шины 1-3 подключены к первым трем входам первого элемен- 2о та И 6, первая информационная шина 1 подключена к входам второго 10 и четвертого 12 элементов НЕРАВНОЗНАЧНОСТЬ, вторая информационная шина 2 подключена к входам первого 9 и тре- 25 тьего 11 элементов НЕРАВНОЗНАЧНОСТЬ, третья информационная шина 3 подключена к входам третьего 11 и четвертого 12 элементов НЕРАВНОЗНАЧНОСТЬ,

12 подключены к входам элемента И 7, выходы элементов НЕРАВНОЗНАЧНОСТЬ 10 и 11 подключены к входам элемента J- ИВ, выходы элементов И 6-8 подключены к входам элемента ИЛИ 13, выход которого подключен к выходу 14.

Предлагаемая схема функционирует, следующим образом,

В статическом состоянии сигналы ,на входы схемы не подаются.

В динамике на шины 1-3 схемы подаются (двоичные наборы входных переменных А, В, С соответственно. Одновременно на управляющие шины 4 и 5 подаются управляющие сигналы И1, И2, принимающие значения двоичных констант О и 1. При этом в соответствии с конкретными значениями управляющих сигналов И1 и И2 с выхода 14 снимается соответствующий сигнал. Функционально выход 14 при этом может быть описан выражением следующего вида

F Н(А,С)Н(В,И1)V Н(В,С)Н(А,И1)У АВСИ2, где F - функция, снимаемая с выхода

первая управляющая шина 4 подключена зо H(A,B)ABVAB - функция НЕРАВНОЗНАЧк входам первого 9 и второго 10 3,ie-НОСТЬ;

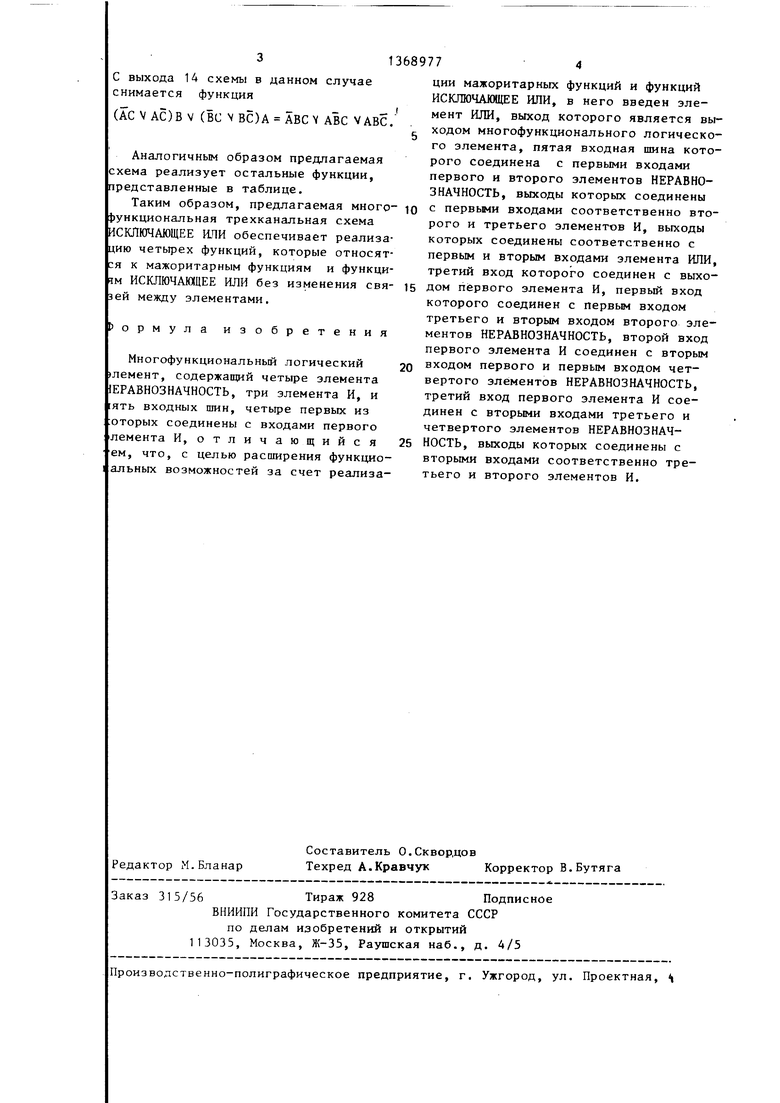

V - логическая операция ИЛИ. Конкретные значения управляющих сигналов И1, И2 при реализации всех функций приведены в таблице.

ментов НЕРАВНОЗНАЧНОСТЬ, вторая управляющая шина 5 подключена к четвер- ,тому входу первого элемента И 6, вы- 1ходы элементов НЕРАВНОЗНАЧНОСТЬ 9 и

35

12 подключены к входам элемента И 7, выходы элементов НЕРАВНОЗНАЧНОСТЬ 10 и 11 подключены к входам элемента ИВ, выходы элементов И 6-8 подключены к входам элемента ИЛИ 13, выход которого подключен к выходу 14.

Предлагаемая схема функционирует, следующим образом,

В статическом состоянии сигналы ,на входы схемы не подаются.

В динамике на шины 1-3 схемы подаются (двоичные наборы входных переменных А, В, С соответственно. Одновременно на управляющие шины 4 и 5 подаются управляющие сигналы И1, И2, принимающие значения двоичных констант О и 1. При этом в соответствии с конкретными значениями управляющих сигналов И1 и И2 с выхода 14 снимается соответствующий сигнал. Функционально выход 14 при этом может быть описан выражением следующего вида

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический элемент | 1989 |

|

SU1667241A1 |

| Устройство для арифметической и логической обработки двоичных чисел | 1981 |

|

SU983705A1 |

| Устройство для мажоритарного декодирования двоичных кодов | 1980 |

|

SU945988A1 |

| Многофункциональный логический модуль | 1986 |

|

SU1348816A1 |

| СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2566946C1 |

| Многофункциональный логический модуль | 1983 |

|

SU1083180A1 |

| Пневматическое мажоритарное устройство | 1983 |

|

SU1112370A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля чередования фаз @ -фазной сети | 1981 |

|

SU1029301A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение функциональных возможностей устройства. Логический элемент содержит элементы И 6-8 и элементы НЕРАВНОЗНАЧНОСТЬ 9-12. Введение элемента ИЛИ 13 позволяет, устройству реализовать мажоритарные функции и функции ИСКЛЮЧАЮЩЕЕ ИЛИ. 1 табл., 1 ил.

Значение

ТИ1 И2

Реализуемые функции

0ОABC V ABC V ABC (ДВА и ТОЛЬКО ДВА) .

.01АВ V АС V ВС (ДВА И ТРИ - НЕ ОДИН)

1ОABC V ABC V ABC (ОДИН И ТОЛЬКО ОДИН)

11ABC V ABC VSBC VABC (ОДИН ИЛИ ТРИ - НЕ ДВА)

Пример. При значениях управляющих сигналов И1 О, И2 0 элемент И 6 закрыт сигналом И2. С выхода элемента НЕРАВНОЗ НАЧНОСТЬ 12 снимается функция АС VAC, а с выхода элемента НЕРАВНОЗНАЧНОСТЬ 11 аналогичным образом снимается функция ВС V ВС. В г.хеме элементы НЕРАВНОЗНАЧНОСТЬ 9 и 10 вьшолняют функции управляемых ин

верторов (в соответствии с логикой

работы элемента НЕРАВНОЗНАЧНОСТЬ Н(Х,И) ХИЧ ХЙ, Н(Х, 1) X и Н(1Х,0) X). Следовательно, с выхода элемен- та НЕРАВНОЗНАЧНОСТЬ 10 снимается сигнал А, а с выхода элемента НЕРАВНОЗНАЧНОСТЬ 9 - сигнал В. С выхода эле- мента И 7 снимается сигнал (АСVAC)В, а с выхода элемента И 8 - (BCVBC)A.

с выхода 14 схемы в данном случае снимается функция

(АС VAC) В V (ВС V ВС)А ABCV ABC VABC.

Аналогичным образом предлагаемая схема реализует остальные функции, редставленные в таблице.

Таким образом, предлагаемая много уикциональная трехканальная схема СКПЮЧАЮЩЕЕ ИЛИ обеспечивает реализа ;ию четьфех функций, которые относят я к мажоритарным функциям и функци м ИСКЛЮЧАЮЩЕЕ ИЛИ без изменения свя ей между элементами.

-

ормула изобретения

Многофункциональный логический лемент, содержащий четыре элемента ЕРАВНОЗНАЧНОСТЬ, три элемента И, и ять входных шин, четыре первых из оторых соединены с входами первого лемента И, отличающийся ем, что, с целью расошрения функцио- альных возможностей за счет реализа

689774

ции мажоритарных функций и функций ИСКЛЮЧАЮЩЕЕ ИЛИ, в него введен эле- мент ИЛИ, выход которого является вы- г ходом многофункционального логического элемента, пятая входная шина которого соединена с первыми входами первого и второго элементов НЕРАВНОЗНАЧНОСТЬ, выходы которых соединены

10 с первыми входами соответственно второго и третьего элементов И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, третий вход которого соединен с выхо- 15 дом riispBoro элемента И, первый вход которого соединен с первым входом третьего и вторым входом второго элементов НЕРАВНОЗНАЧНОСТЬ, второй вход первого элемента И соединен с вторым

20 входом первого и первым входом четвертого элементов НЕРАВНОЗНАЧНОСТЬ, третий вход первого элемента И соединен с вторыми входами третьего и четвертого элементов НЕРАВНОЗНАЧ25 НОСТЬ, выходы которых соединены с вторыми входами соответственно третьего и второго элементов И.

Авторы

Даты

1988-01-23—Публикация

1986-05-26—Подача