1

Иаобрегение относится к вычислительной f технике и может использоваться щри построении устройств одновременного вьшопнения нескольких операций обработки двоичных чисел.

Известен угравляемый функциональный модуль, который позволяет реализовать любые операции логической обработки трех двоичных чисел 1

Недостатком известного устройства ляется то, что оно не реализует арифметической операции сложения. Это ограничивает область применения фн построении арифметико-логических устройств.

Наиболее близким к изобретению по технической сущности является устройство, содержащее в каждом разряде два мультиплексора, элементы И, ИЛИ и ИСКЛЮЧАв ЮЩЕЕ ИЛИ. Управляющие входы мульти-2в плексоров попарно объединены и подключены к информационным входам разряда, а их информационные входы - к угфавляю- щим входам устройства. Выход первого ,

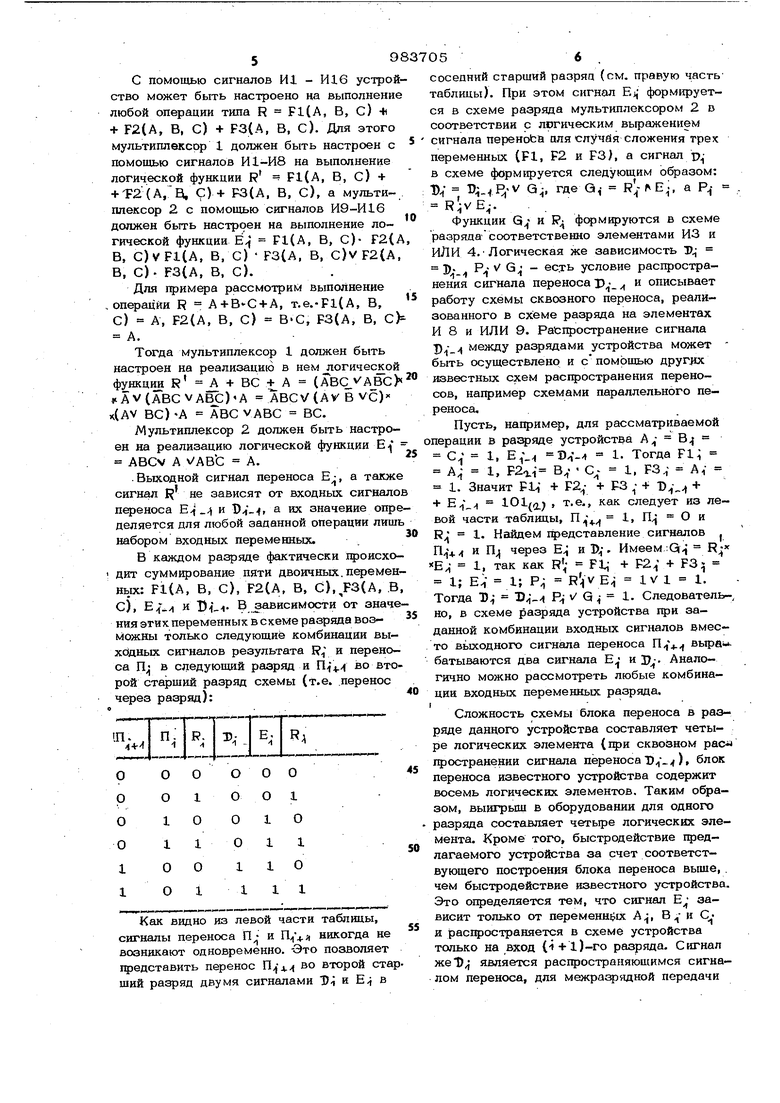

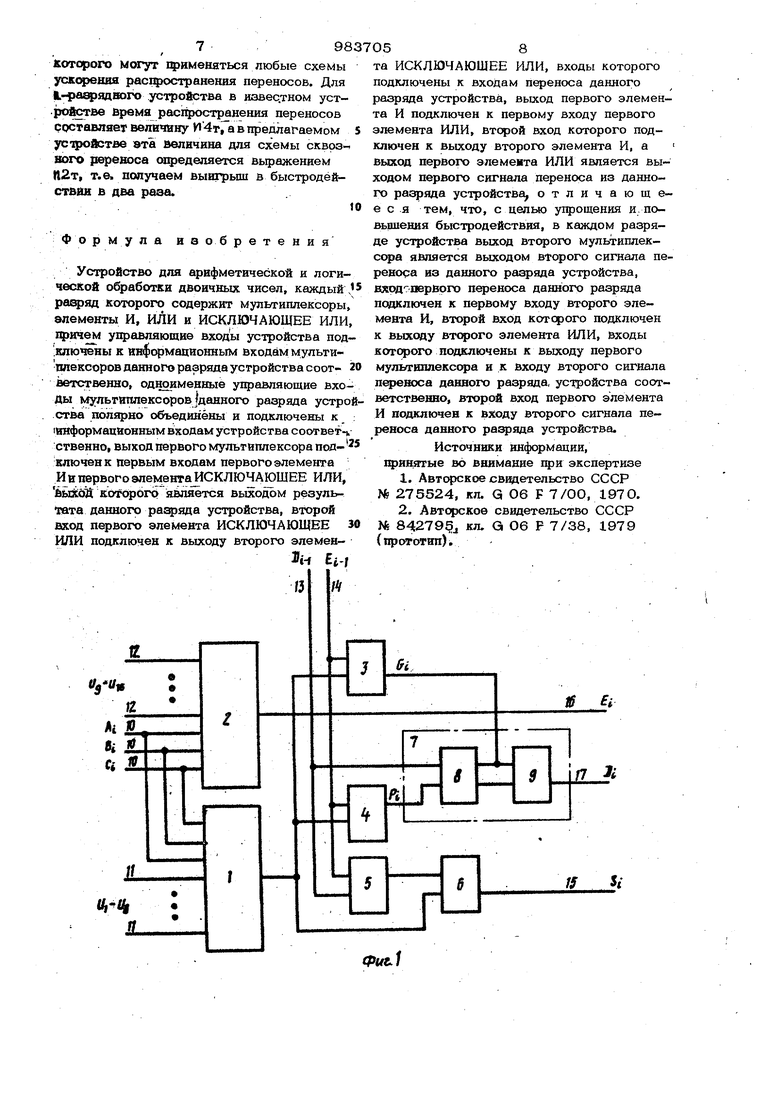

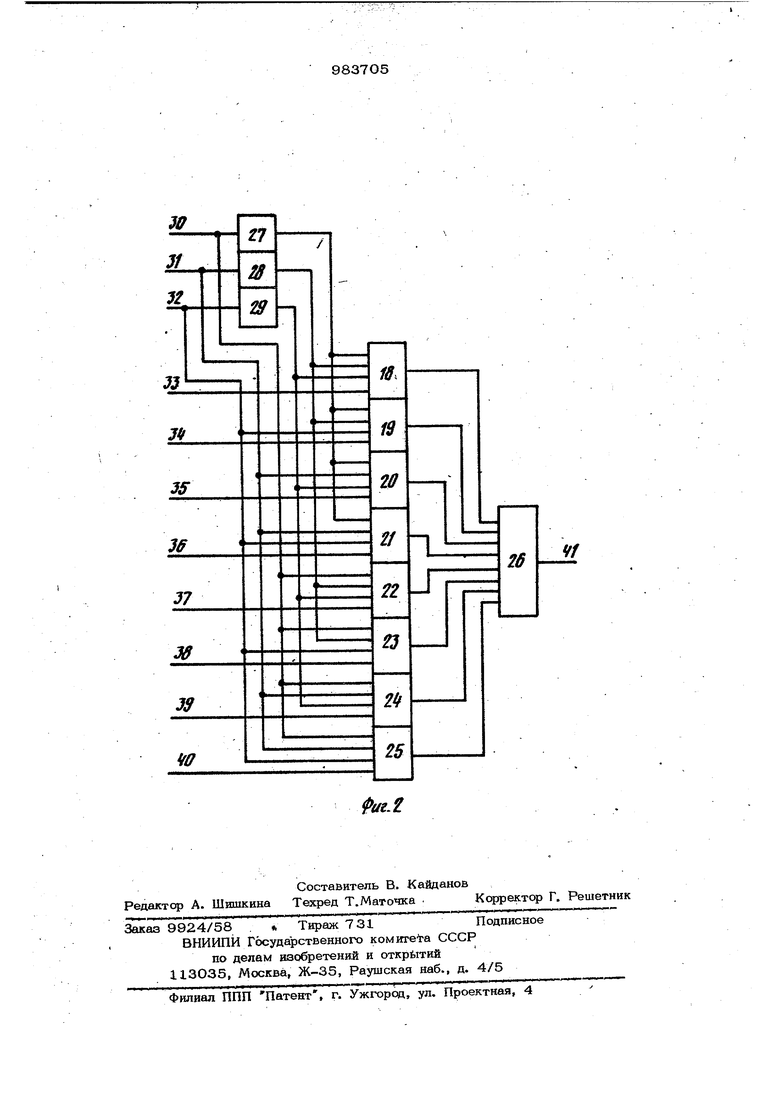

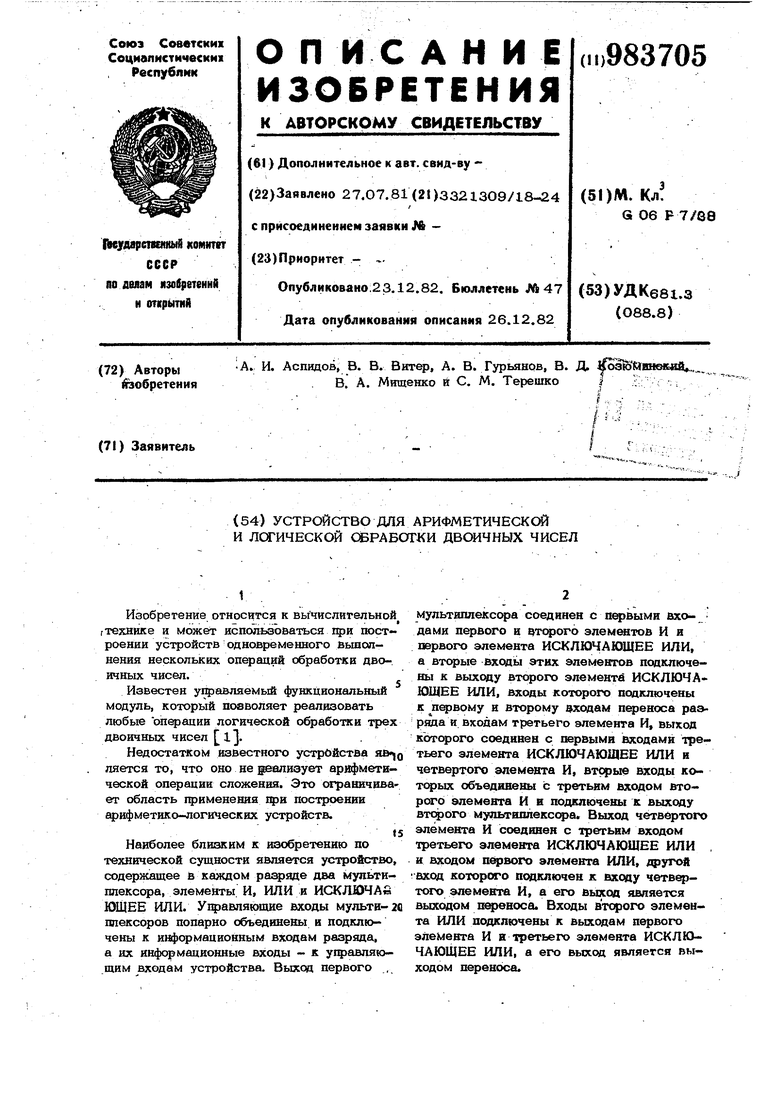

мультиплексора соединен с первыми вхо- да ми первого и второго эпеиевпов И и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а вторые входы этих элементов подключены к выходу второго элементй ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого подключены к первому и второму хоа&м переноса разряда и вкодам третьего элемента И, выход которого соединен с первыми входами третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертого элемента И, вторые входы которых объединены с третьим входом второго элемента И и подключены к выходу втфого мупьтшшекссфа. Выход четвертого элемента И соединен с третьим входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ , и входом нового элемента ИЛИ, другоЛ ВХОД которого подключен к входу четвертого элемента И, а его выход $1вляется выходом переноса. Входы второго элемента ИЛИ подключены к выходам первого элемента И и третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а его выход является выходом переноса. 398 Данное устройство реализует путем настройки любые операции типа С F1(X1 Х2,..., Х) + F2(X1, Х2,..., Xyj) + F3(X1, Х2,..., XJ), где F (Xi, Х2, ..., Х) - произвольная логическая функция от VI входных сигналов 2. Недостатками известного устройства являются сложность конструкции из-за сложности схем формирования выходных сигналов перенос,, а также низкое быстродействие. Низкое быстродействие объясняется возможностью только последовательного распространения сигналов переноса между разрядами устройства, а так , „„„„„„„ ,„ „ же задержкой сигнала переноса в каждом разряде, на время до 4 т, где т - время задержки одного логического элемента. Цель изобретения - упрощение и повышение быстродействия устройства для арифметической и логической обработки двоичliA frMXrrf r V Jf Ttl T UTTT/Ar Vf fY sR-r Г ГпИ -чИгж ных чисел. Поставленная цель достигается тем, что в устройстве для арифметической и логической обработки двоичных чисел, каждый разряд которого содержит мультиплексоры, элементы И, ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ, причем управляющие входы устройства подключены к информационным входам мультиплексоров данного разряда устройства соответственно, одноименные управляющие входы мультиплексоров данного разряда устройстваполярно объединены и подключены к информационным входам устройства соответственно, выход первого муль.тшшексора подключен к первым входам первого элемента И и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом результата данного разряда устройства, второй вход первого элемен та ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к выходу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого подключены к входам переноса данного разряда устройства, выход первого элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, а выход первого элемента ИЛ является выходом первого сигнала переноса из данного разряда устройства, в каждом разряде выход второго мультиплексора является выходом второго сигнала переноса из данного разряда устройства, вход первого переноса данного разряда подключен к первому входу второго элемента И, второй вход которого подключен к выходу Второго элемента ИЛИ, входы которого подключены к выходу первого Мультиплексора и к входу второго сигнала переноса О54 данного разряда устройства соответственно, второй вход первого элемента И .подключен к входу второго сигнала переноса данного разряда устройства. На фиг. 1 изображена схема разряда устройства; на фиг. 2 - схема мультиплексора. Устройство (фиг. 1) содержит мультиплексоры 1 и 2, элемент И 3, элемент ИЛИ 4, два элемента 5 и 6 неравнозначности, блок 7 распространения сигнала переноса, выполненный в качестве примера на элементах И 8 и ИЛИ 9, информационные входы 1О, две группы управляю, „ но t xi тих входов 11 и 12, два входа 13 и 14 переноса, выход 15 результата и два выхода 16 и 17 переноса. Схема мультиплексора (фиг. 2) содержит элементы И 18-25, ИЛИ 2в, НЕ ,71фашяювде в;оды Зо1з2,формационные входы 33-40 и выход 41. Одноименные управляющие входы мультиплексоров 1 и 2 попарно объединены и подключены к информационным входам 1О раунда, а их информационные входы подключены соответственно к группам управляющих входов 11 и 12. Выход мультиплексора I подключен к входам элементов И 3, ИЛИ 4 и элемента 6 неравнозначности, выход которого является выходом 15 результата, а его другой вход подключен к выходу элемента 5 неравнозначности, входы которого подключены к входам 13 и 14 переноса. Другие одноименные входы элементов И 3 н ИЛИ 4 объединены и подключены к входу 14 переноса. Выход элемента ИЛИ 9 блока 7 распространения сигнала переноса является выходом 17 сигнала переноса из данного разряда, а входы элемента ИЛИ 9 подключены к выходу элементами 3 и выходу элемента И 8, входы которого подключены к выходу элемента И 4 и входу 13 переноса. Выход мультиплексора 2 является выходом 16 сигнала переноса из данного разряда. Схема устройства работает следующим образом. На информационные входы Ю подаются одноименные разряды опера вдов А , В и . На входы 13 и 14 переноса подаются сигналы переноса Щ|- и Т),,-.,, из предьодущего разряда. На группы уравляющих входов 12 подаются сигналы настройки соответственно И1 - И8 и И9 - И16. С выходов 16 и 17 снимаются сигналы переноса в следующий разряд Е, к J):, а с выхода 15 -сигнал результага операции R,-. с помощью сигналов И1 - И16 устрой ство может быть настроено на выполнени любой операции типа R Fl(A, В, С) + F2(A, В, С) + F3(A, В, С). Для этого мультиплексор 1 должен быть настроен с помощью сигналов И1-И8 на выполнение логической функции R F1{A, В, C)+F2 (Л.Ц, С) + F3{A, В. с), а мультиплексор 2 с помощью сигналов И9-И16 должен быть настроен на выполнение логической функции Ё-{ F1(A, В, С)- F2( В, С) V F1(A, В, с) РЗ(А, В, C)V F2(A В, С). РЗ{А, В, с).. Для примера рассмотрим выполнение , операции R А+В-С + А, T.e.-Fl(A, В, с) А, F2(A, В, С) ВС, F3(A, В, С А. Тогда мультиплексор 1 должен быть настроен на реализацию в нем логичес сой функции R А + вс + А (АВС.АВС) «AV(ABCVABC)A BCV(AyBVC)p. x(AV ВС) А ABC VABC ВС. Мультиплексор 2 должен быть настроен на реализацию логической функции Е{ ABCV А ч/АВС А. .Выходной сигнал переноса Е-, а также сигнал R не зависят от входных сигнало переноса E-t и B/i-, а их значение опре деляется для любой заданной операции лищь набором входных переменных. В каждом разряде фактически гфоисхо- дит суммирование пяти двоичных. nqieMeH Hbix: F1(A, В, С), F2(A, В, C),,F3(A, В с), и В зависимости от значе ния этих переменных в скеме разряда возможны только следующие комбинации выходных сигналов результата и переноса П в следующий разряд и . во второй старшкё. разряд схемы (т.е. .перенос через разряд): -..-. ,h,u, ь, UjR, 41 -I-- ---1--- ,,.Это определяется

Как видно из левой части таблицы, сигналы переноса П и никогда не возникают одновременно. -Это позволяет представить перенос . во второй старщий разряд двумя сигналами Di и Е в 9

ВИСИТ только от переменней А, В - и Си распространяется в схеме устройства только на вход (i + l)-ro разряда. Сигнал жеТ) является распространяющимся сигналом переноса, для межраг ядной передачи 056 . сосепний старший разряд (см. правую часть таблицы). При этом сигнал EJ, форм{фуется в схеме разряда мультиплексором 2 в соответствии с логическим выражением сигнала переноЬа аля случая сложения трех переменных (F1, F2 и F3), а сигнал схеме формируется следующим образом: D D.+ Q:J. где Q,- ., a . . , Функции G и формируются в схеме разряда-соответственно элементами ИЗ и ИЛИ 4, Логическая же зависимость D. Р.- V - есть условие распространения сигнала переноса и описывает работу схемы сквозного переноса, реализованного в сХеме разряда на элементах И 8 и ИЛИ 9. Распространение сигнала Т)- между разрядами устройства может быть осуществлено и с помощью друглх известных схем распространения переносов, например схемами параллельного переноса. Пусть, например, для рассматриваемой перации в устройства - В 1, 1. Тогда F1-; - 1, F2г1 . F3.,- AV А,- 1. Значит Fli 4- -ь РЗ - -f Т)-„ + + , т.е., как следует из левой части таблицы, 1, П О и 1. Найдем федставление сигналов и П через Е и . Имеем R 1, так как FJ + F2 1; Е,- 1; Р IV 1 Тогда D Р V Q - 1. Следователь-, но, в схеме разряда устройства при заданной комбинации входных сигналов вместо вьссодного сигнала переноса ПY4- вьфа- батываются два сигнала и . Аналогично можно рассмотреть любые комбинации входных переменных разряда. Сложность схемы блока переноса в разряде данного устройства составляет четыре логических элемента (при сквозном раса гфостранении сигнала переноса ), блок переноса известного устройства содержит восемь логических элементов. Таким образом, выигрьЕЦ в оборудовании для одного разряда составляет четыре логических элемента. Кроме того, быстродействие предлагаемого устройства за счет соответствующего построения блока переноса выще,. чем быстродействие известного устройства. тем, что сигнал Е за98Которого могут применяться любые схемы ускорения расщюстранения переносов. Для ||1-1)аарадвого устройства в иавес,тном устpoSteTBe Время распространения переносов составляет величину И 4т, а в предлагаемом устройстве эта величина для схемы скврз-. ного ререаоса определяется выражением Л2т, т.е. получаем выигрьпи в быстродействии в два раза. Фор мула р е т е н и я Устройство для арифметической и логической обработки двоичных чисел, каждый, равряд которого содержит мультиплексоры, элементы И, ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ 1 ичв1М управляющие входы устройства подключены к информационным входам мультиплексоров данного разряда усгройсгва соответственно, одноименные управляющие вхоДы мультиплексоров|данного разряда устро ства полярно объединены и подключены к (информационным входам устройства соответ-k ственно, выход первого мультиплексора под- ключей к первым входам первого элемента Иитарвогоэлемента ЮКЛЮЧАЮЩЕЕ ИЛИ, Которого является вькодом результата данного разряда устройства, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ 3 ИЛИ подключен к выходу второго элемен-Bi-f ЕЙ 05 та ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого подключены к входам переноса данного разряда устройства, выход первого элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, а выход первого элемеита ИЛИ является выходом первого сигнала переноса из данного разрада устройства, отличающееся тем, что, с целью ущзощения и повьщ1ения быстродействия, в каждом разряде устройства выход второго мультиплексора является выходом второго сигнала переноса из данного разряда устройства, входсперврго переноса данного разряда подключен к первому входу второго элемента И, второй вход которого подключен к выходу элемента ИЛИ, входы кот(5)ого подключены к выходу первого мультиплексора и к входу второго сигнала перевеса данного разряда, устройства соответственно, второй вход первого элемента и подключен к входу второго сигнала переноса данного разряда устройства. Источники информации, л ищггые во внимание при экспертизе 1.Авторское сввдетельство СССР № 275524, кл. Q 06 F 7/00, 1970. 2.Авторское свидетельство СССР № 842795j кл. Q Об F 7/38, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| БАЛАНСНАЯ ЧАСТОТНАЯ СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1992 |

|

RU2073910C1 |

| Вычислительная система | 1983 |

|

SU1233159A1 |

| Программируемое устройство для вычисления логических функций | 1987 |

|

SU1444744A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| САМОКОНТРОЛИРУЕМЫЙ АВТОМАТ | 2011 |

|

RU2502121C2 |

| СЧЕТЧИК ГРУППОВОЙ СТРУКТУРЫ С СОХРАНЕНИЕМ КОЛИЧЕСТВА ЕДИНИЦ В ГРУППАХ | 2020 |

|

RU2736704C1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО МАГАЗИННОГО ТИПА | 1991 |

|

RU2081459C1 |

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

Авторы

Даты

1982-12-23—Публикация

1981-07-27—Подача