ел

00

Изобретение относится к автомяти- ке и вычислительной технике и может быть использовано при проектировании вычислительных систем и устройств повышенной надежности.

Цель изобретения - повышение надежности системы за счет диагностирования и блокировки отказавших модулей.

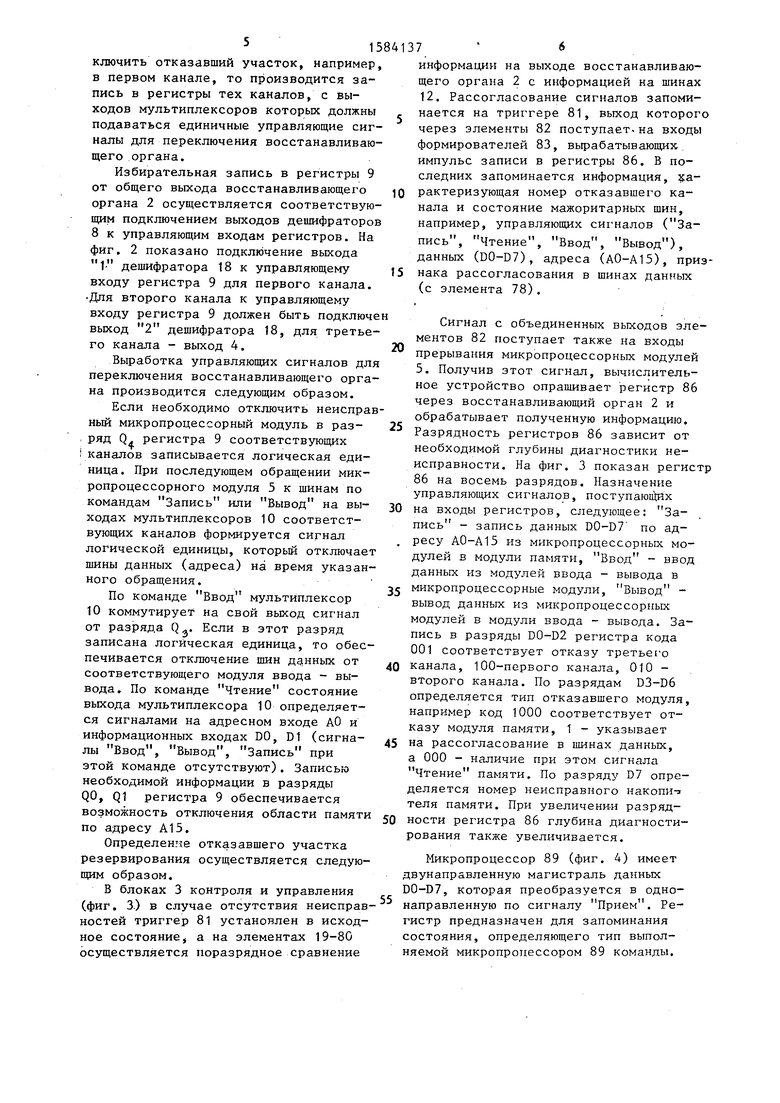

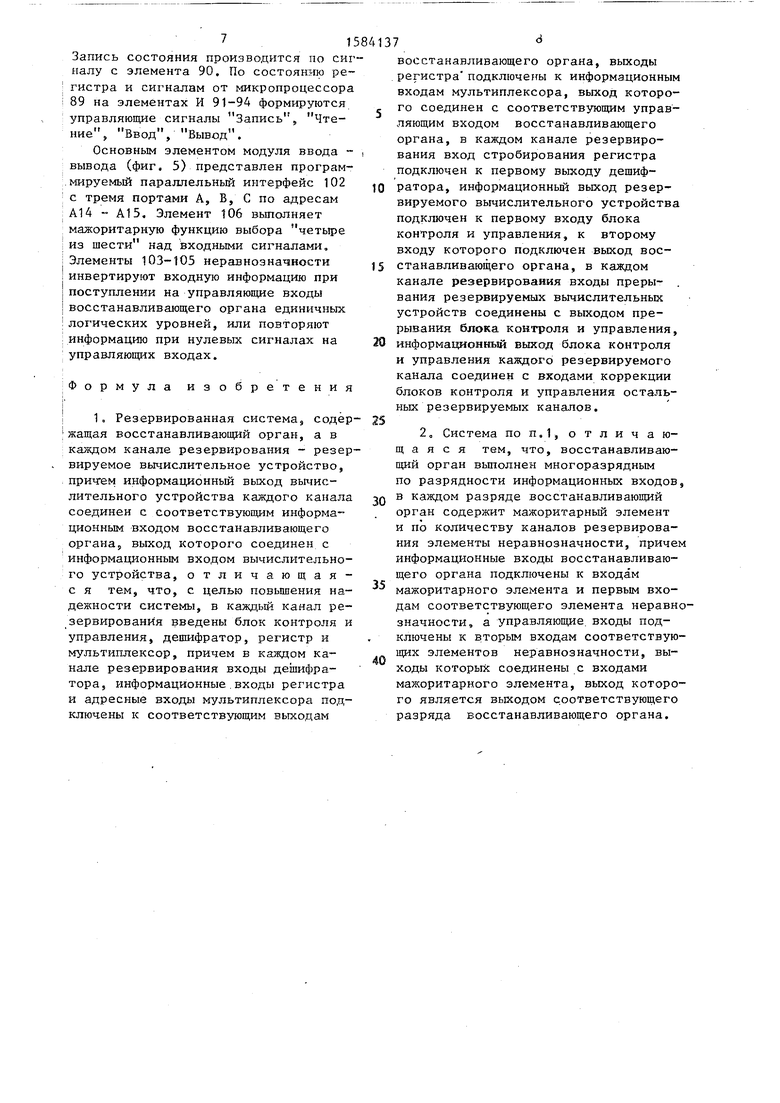

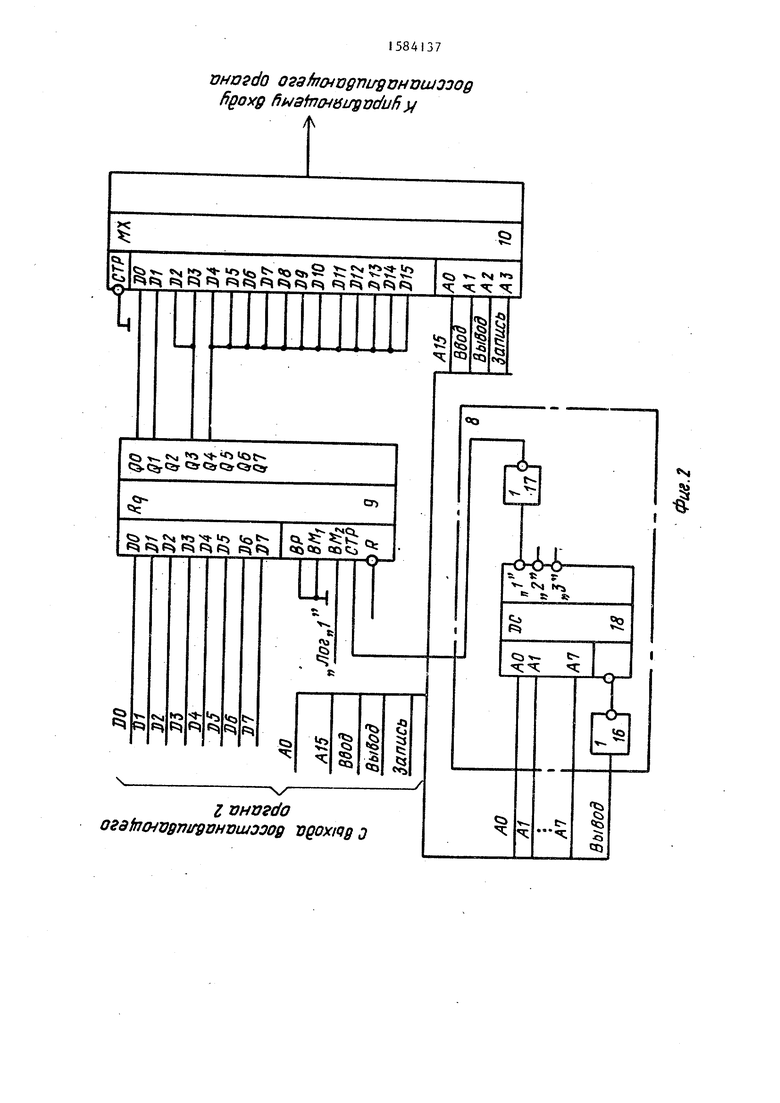

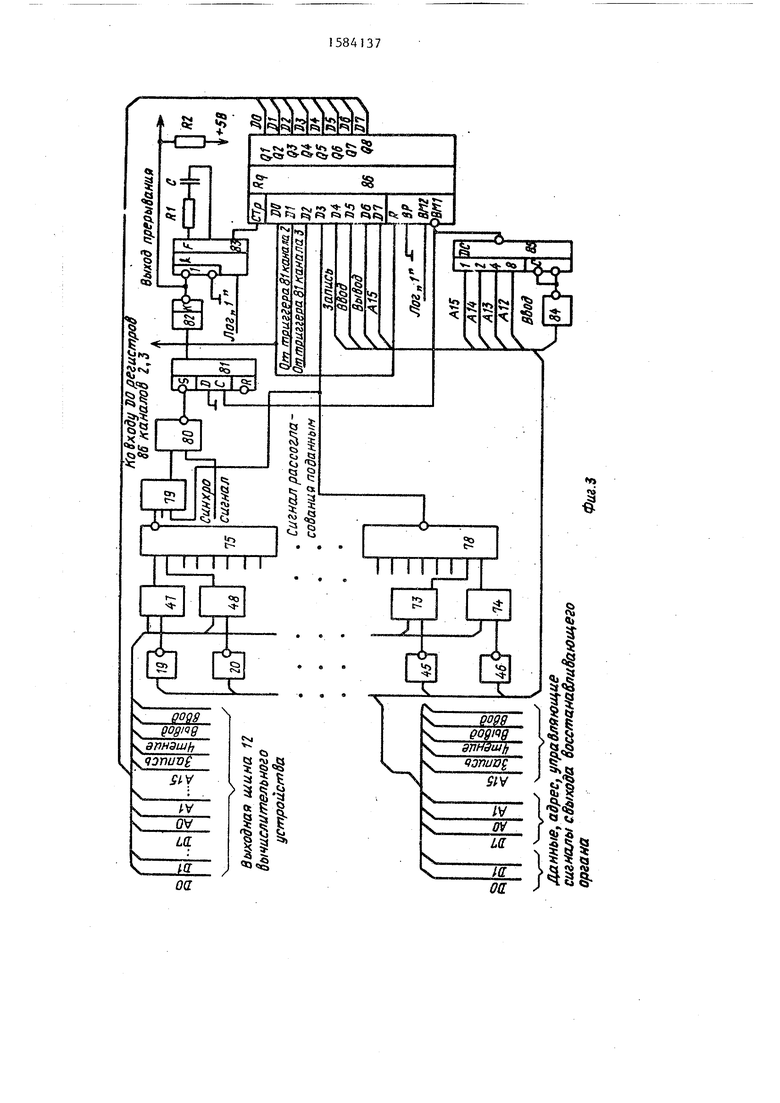

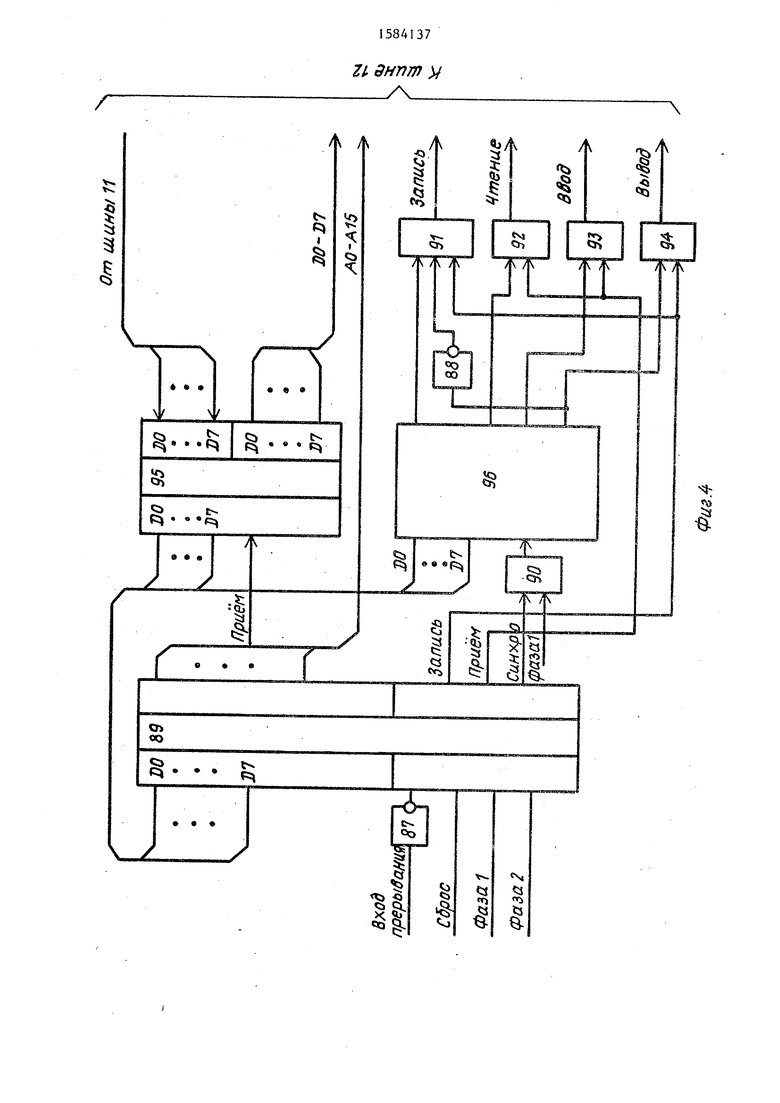

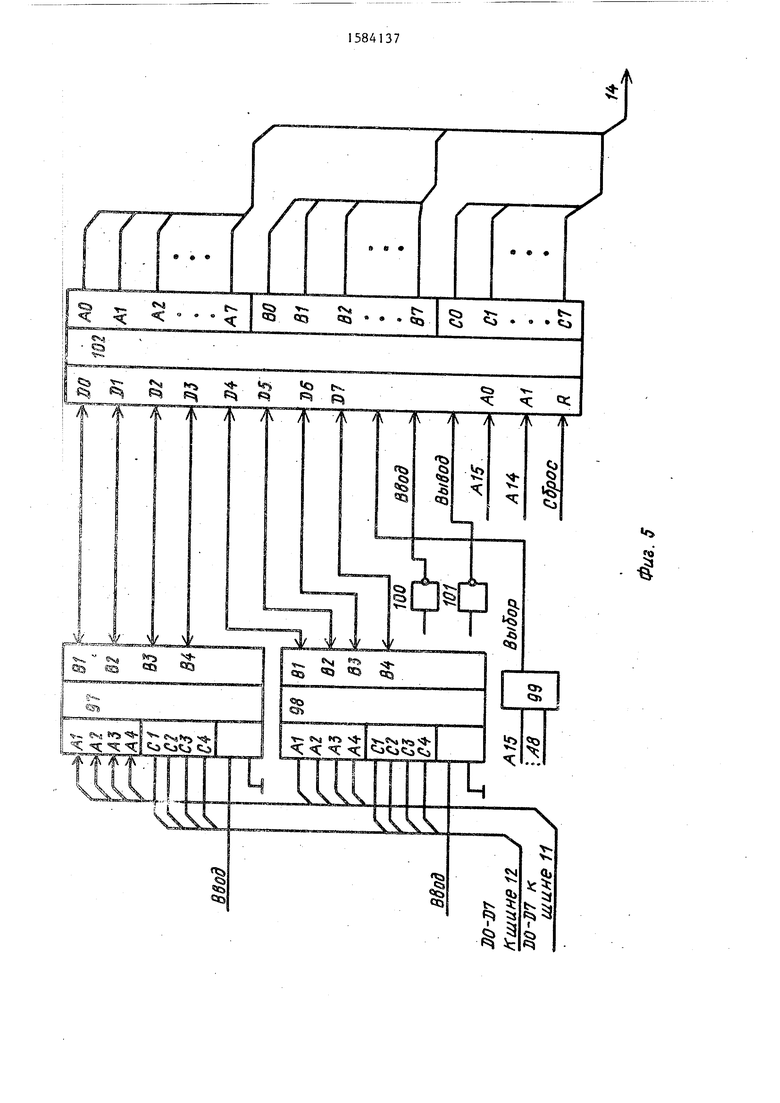

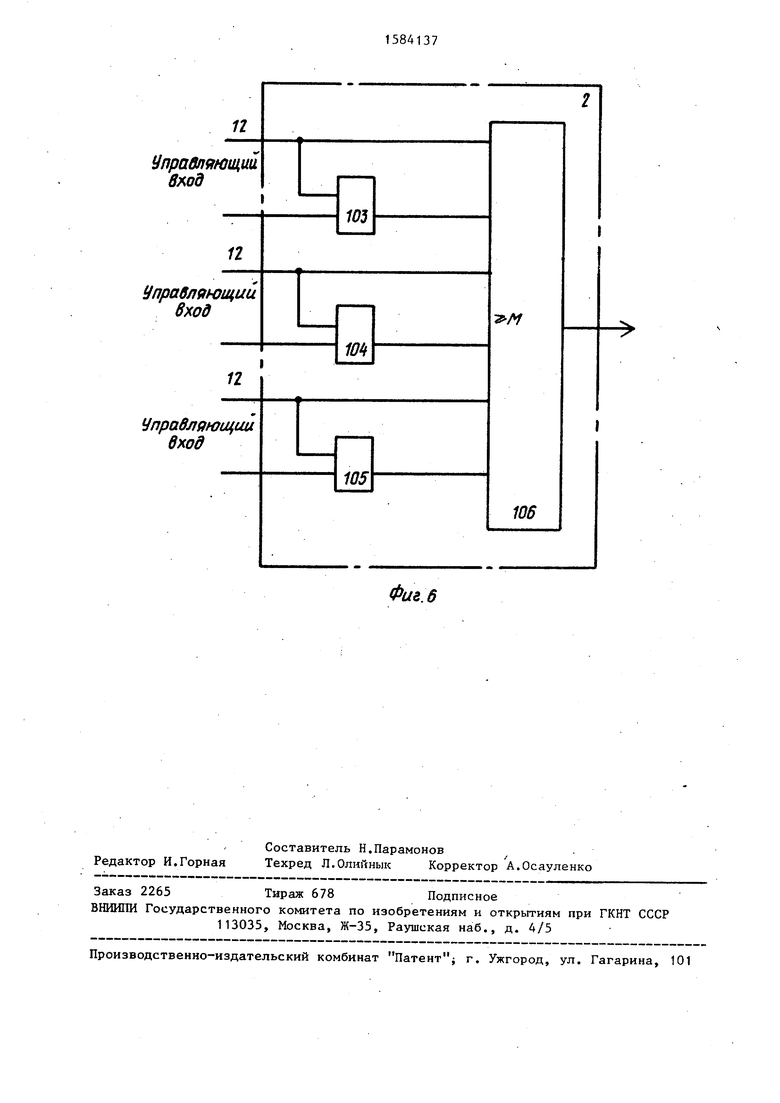

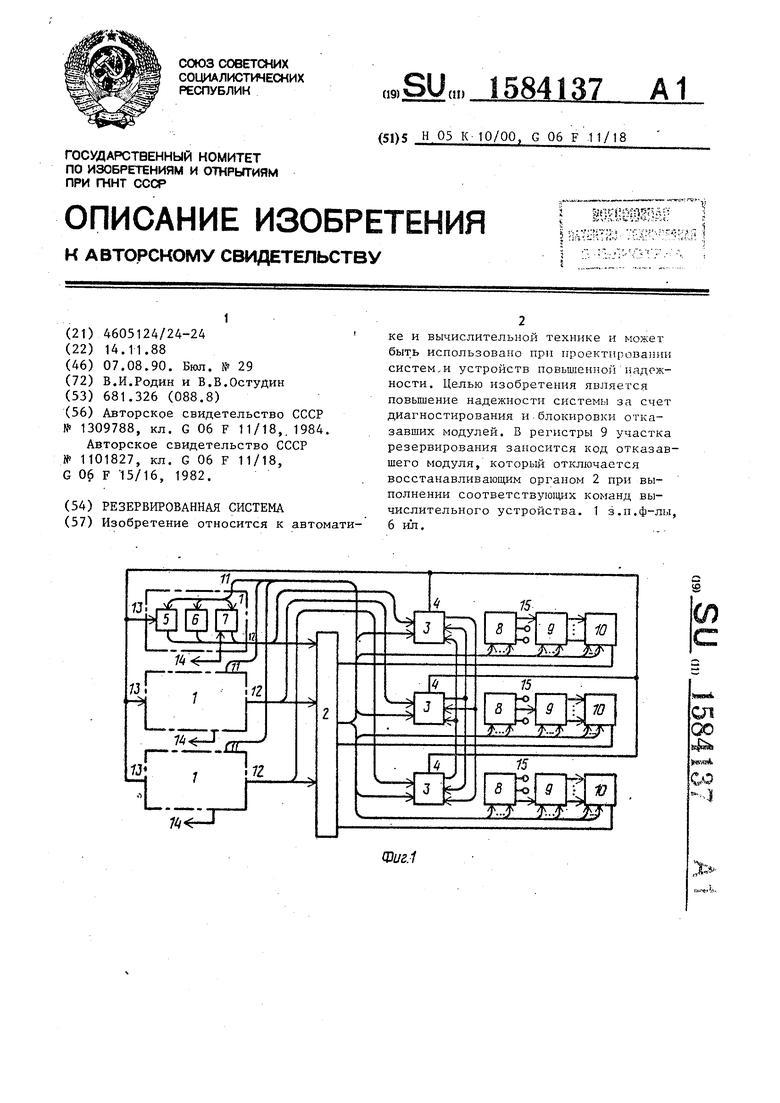

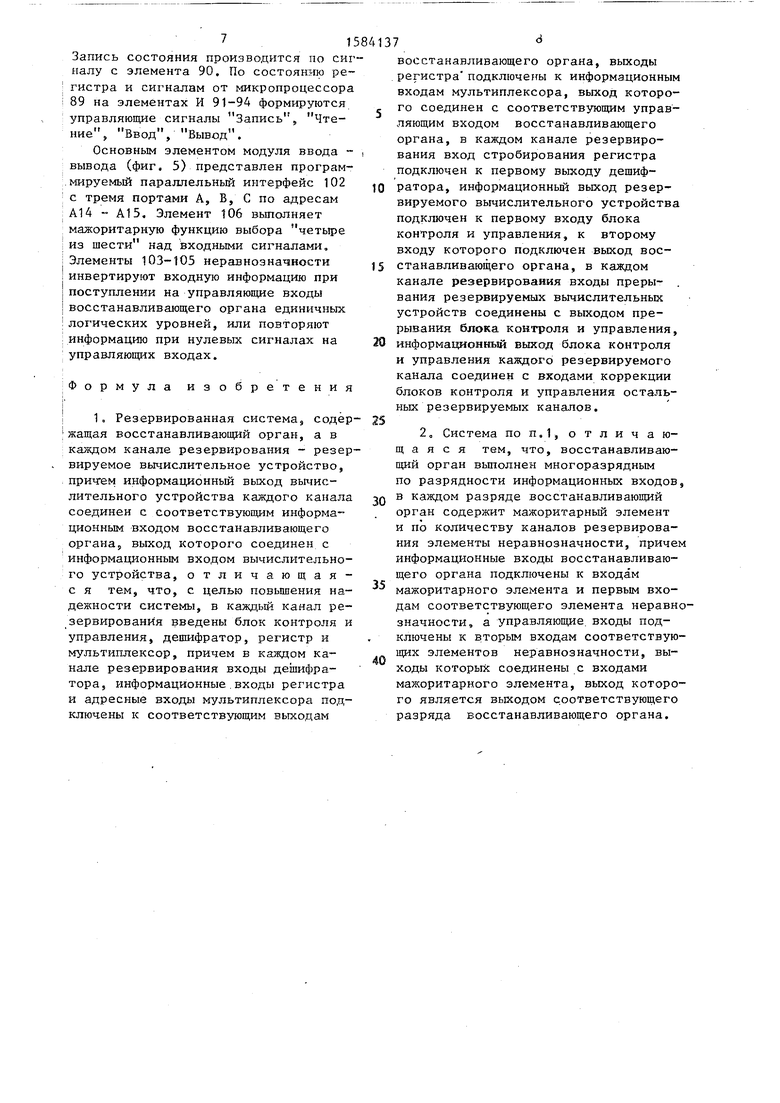

На фиг. 1 показана функциональная схема резервированной системы; на фиг, 2 - вариант подключения информационных входов мультиплексора к выходу регистра; на фиг. 3 - ваг риант реализации блока контроля и управления; на фиг. 4 - схема микропроцессорного модуля; на фиг. 5 - схема модуля ввода - вывода; на фиг. 6 - схема восстанавливающего органа.

Резервированная система (фиг. 1) состоит из резервируемых вычислительных устройств 1, восстанавливающего органа 2, блоков 3 контроля и управления, выходов 4 прерывания, микропроцессорного модуля 5, модуля 6 памяти, модуля 7 ввода - вывода, дешифратора 8, регистра 9 (номера участка резервирования), мультиплексора 10, входной шины 11, выходной шины 12, входов 13 прерывания, двунаправленной шины 14 устройства 1 и выходов 15 дешифраторов„ Система содержит также инверторы 16 и 17 и дешифратор 18.

Блок 3 контроля и управления (фиг. 3) состоит из инверторов 19-46 элементов 47-74 неравнозначности, 8-входовых элементов И-НЕ 75-78, элементов ИЛИ 79 и И-НЕ 80, триггера 81 элемента 82 с открытым коллектором, формирователя 83, инвертора 84, дешифратора 85 и регистра 86.

Микропроцессорный модуль 5 (фиг. 4 содержит инверторы 87 и 88, микропроцессор 89, элементы И 90-94 и шинные формирователи 95 и 96,

Модуль .7 ввода - вывода (фиг. 5) состоит из шинных формирователей 97 и 98, дешифратора 99, инверторов 100 и 101 и параллельного программируемого интерфейса 102,

На фиг. 6 показан восстанавливающий opiаи 2 на один разряд, выполненный на элементах 103-105 неравнозначности и мажоритарных элементах 106.

Система работает спедующим образом.

o

5

0

5

В устройствах 1 три микропроцессорных модуля 5 работают синхронно по одинаковым программам, хранимым в модулях 6 памяти. Обмен информацией устройств 1 с периферийными производится через модули 7 ввода - вывода по двунаправленным шинам 14. Выходные шины 12, предназначенные для передачи адреса, данных и управляющих сигналов, представляют собой совокупность линий связи, идущих от микропроцессорных модулей 5 через восстанавливающий орган 2 и входные шины 11 к модулям 6 памяти и ввода - вывода 7 и, наоборот, от модулей па-. мяти 6 и ввода - вывода 7 к микропроцессорным модулям 5. Система продолжает правильно функционировать при отказе любого из резервируемых компонентов.

При обнаружении отказа конкретного модуля или участка резервирования в системе имеется возможность переключения восстанавливающего органа в режим работы от одного из двух оставшихся исправными модулей данного типа. Восстанавливающий орган выполняет мажоритарную функцию выбора два из трех над входными сигналами. По управляющим сигналам он транслирует информацию от одного из двух исправных каналов на свой выход.

В исходном режиме регистры 9 (фиг. 1 и 2) установлены в нулевое состояние. При работе системы в случае отсутствия записи в регистры 9 на выходах мультиплексоров 10 присутствуют также нулевые сигналы. Восстанавливающий орган 2 при этом выполняет мажоритарную функцию. Переключение восстанавливающего органа в режим работы от одного исправного канала осуществляется подачей на соответствующие входы единичных управляющих сигналов от мультиплексоров 10. Если обнаружен отказ в первом канале, то единичные сигналы должны подаваться от мультиплексоров первого и второго (или третьего) ка- 0 налов, при отказе во втором канале - от мультиплексоров второго и третьего (или первого) каналов, в третьем канале - от первого и третьего (или второго) каналов.

0

5

0

5

При обнаружении отказа в регистры 9 записывается информация, соответствующая номеру отказавшего участка резервирования. Если необходимо отключить отказавший участок, например, в первом канале, то производится запись в регистры тех каналов, с выходов мультиплексоров которых должны подаваться единичные управляющие сигналы для переключения восстанавливающего органа.

Избирательная запись в регистры 9 от общего выхода восстанавливающего органа 2 осуществляется соответствующим подключением выходов дешифраторов 8 к управляющим входам регистров. На фиг. 2 показано подключение выхода 1- дешифратора 18 к управляющему входу регистра 9 для первого канала. Для второго канала к управляющему входу регистра 9 должен быть подключе выход 2 дешифратора 18, для третьего канала - выход 4.

Выработка управляющих сигналов для переключения восстанавливающего органа производится следующим образом.

Если необходимо отключить неисправный микропроцессорный модуль в разряд Q. регистра 9 соответствующих каналов записывается логическая единица. При последующем обращении микропроцессорного модуля 5 к шинам по командам Запись или Вывод на выходах мультиплексоров 10 соответствующих каналов формируется сигнал логической единицы, который отключает шины данных (адреса) на время указанного обращения.

По команде Ввод мультиплексор Ю коммутирует на свой выход сигнал от разряда Qу Если в этот разряд записана логическая единица, то обеспечивается отключение шин данных от соответствующего модуля ввода - вывода. По команде Чтение состояние выхода мультиплексора 10 определяется сигналами на адресном входе АО и информационных входах DO, D1 (сигналы Ввод, Вывод, Запись при этой команде отсутствуют). Записью необходимой информации в разряды QO, Q1 регистра 9 обеспечивается возможность отключения области памяти по адресу А15.

Определение отказавшего участка резервирования осуществляется следующим образом.

В блоках 3 контроля и управления (фиг. 3) в случае отсутствия неисправностей триггер 81 установлен в исходное состояние, а на элементах 19-80 осуществляется поразрядное сравнение

Q 5 0

5

0

5

0

5

0

информации на выходе восстанавливающего органа 2 с информацией на шинах 12. Рассогласование сигналов запоминается на триггере 81, выход которого через элементы 82 поступает-на входы формирователей 83, вырабатывающих- импульс записи в регистры 86. В последних запоминается информация, характеризующая номер отказавшего канала и состояние мажоритарных шин, например, управляющих сигналов (Запись, Чтение, Ввод, Вывод), данных (DO-D7), адреса (АО-А15), признака рассогласования в шинах данных (с элемента 78).

Сигнал с объединенных выходов элементов 82 поступает также на входы прерывания микропроцессорных модулей 5. Получив этот сигнал, вычислительное устройство опрашивает регистр 86 через восстанавливающий орган 2 и обрабатывает полученную информацию. Разрядность регистров 86 зависит от необходимой глубины диагностики неисправности. На фиг. 3 показан регистр 86 на восемь разрядов. Назначение управляющих сигналов, поступающих на входы регистров, следующее: Запись - запись данных DO-D7 по адресу АО-А15 из микропроцессорных модулей в модули памяти, Ввод - ввод данных из модулей ввода - вывода в микропроцессорные модули, Вывод - вывод данных из микропроцессорных модулей в модули ввода - вывода. Запись в разряды DO-D2 регистра кода 001 соответствует отказу третьего канала, ЮО-первого канала, 010 - второго канала. По разрядам D3-D6 определяется тип отказавшего модуля, например код ЮОО соответствует отказу модуля памяти, 1 - указывает на рассогласование в шинах данных, а 000 - наличие при этом сигнала Чтение памяти. По разряду D7 определяется номер неисправного накопи- теля памяти. При увеличении разрядности регистра 86 глубина диагностирования также увеличивается.

Микропроцессор 89 (фиг. 4) имеет двунаправленную магистраль данных DO-D7, которая преобразуется в одно- направленную по сигналу Прием. Регистр предназначен для запоминания состояния, определяющего тип выполняемой микропроцессором 89 команды.

71584137

Запись состояния производится по сигналу с элемента 90. По состоянию регистра и сигналам от микропроцессора 89 на элементах И 91-94 формируются

управляющие сигналы Запись, Чтение, Ввод, Вывод.

Основным элементом модуля ввода - вывода (фиг. 5) представлен программируемый параллельный интерфейс 102 с тремя портами А, В, С по адресам А14 - А15. Элемент 106 выполняет мажоритарную функцию выбора четыре из шести над входными сигналами, Элементы 103-105 неравнозначности инвертируют входную информацию при поступлении на управляющие входы восстанавливающего органа единичных логических уровней, или повторяют информацию при нулевых сигналах на управляющих входах.

Формула изобретения

1. Резервированная система, содержащая восстанавливающий орган, а в каждом канале резервирования - резервируемое вычислительное устройство, причтем информационный выход вычислительного устройства каждого канала соединен с соответствующим информационным входом восстанавливающего органа, выход которого соединен с информационным входом вычислительного устройства, отличающая- с я тем, что, с целью повышения надежности системы, в каждый канал резервирования введены блок контроля и управления, дешифратор, регистр и мультиплексор, причем в каждом канале резервирования входы дешифратора, информационные входы регистра и адресные входы мультиплексора подключены к соответствующим выходам

0

5

0

0

5

0

восстанавливающего органа, выходы регистра подключены к информационным входам мультиплексора, выход которого соединен с соответствующим управляющим входом восстанавливающего органа, в каждом канале резервирования вход стробирования регистра подключен к первому выходу дешифратора, информационный выход резервируемого вычислительного устройства подключен к первому входу блока контроля и управления, к второму входу которого подключен выход восстанавливающего органа, в каждом канале резервирования входы прерывания резервируемых вычислительных устройств соединены с выходом прерывания блока контроля и управления, информационный выход блока контроля и управления каждого резервируемого канала соединен с входами коррекции блоков контроля и управления остальных резервируемых каналов.

2. Система по п.1, отличающаяся тем, что, восстанавливающий орган выполнен многоразрядным по разрядности информационных входов, в каждом разряде восстанавливающий орган содержит мажоритарный элемент и по количеству каналов резервирования элементы неравнозначности, причем информационные входы восстанавливающего органа подключены к входам мажоритарного элемента и первым входам соответствующего элемента неравнозначности, а управляющие входы подключены к вторым входам соответствующих элементов неравнозначности, выходы которых соединены с входами мажоритарного элемента, выход которого является выходом соответствующего разряда восстанавливающего органа.

:ь.

С ffb/хода восстанавливающего органа 2

хч

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированная система | 1990 |

|

SU1785087A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Резервированное устройство | 1982 |

|

SU1059710A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Многоканальное резервированное устройство | 1983 |

|

SU1111263A1 |

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Резервированное устройство для управления электропневмоклапанами | 1989 |

|

SU1647512A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Многоканальное резервированное устройство | 1981 |

|

SU991628A1 |

| Дешифратор с коррекцией ошибок | 1981 |

|

SU1012262A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании систем и устройств повышенной надежности. Целью изобретения является повышение устройства за счет диагностирования и блокировки отказавших модулей. В регистры 9 участка резервирования заносится код отказавшего модуля, который отключается восстанавливающим органом 2 при выполнении соответствующих команд вычислительного устройства. 1 з.п. ф-лы, 6 ил.

$

J

§

« si

Nj

A 3

ГГГ

I

L-OJ

I

03

CtJ

c,

«)

ъ.

Oj K

Ь c

К управляющему входу восстанавливающего органа

ct

I

3J

Ј

ta

4s

td

0

td

9

I

4

-, ОО 43 ta Js э ta

|O) л Фч O V Ci

to

U -«i

«ja « o

ta 5 tafcj tdtdtdN ta

I

ca

3

Данные, адрес, управляющие сигналы с Выхода восстанавливающего органа

(п

СО

-рLO-J

Фиг.З

Фиг. 6

| Авторское свидетельство СССР № 1309788, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-07—Публикация

1988-11-14—Подача