Од

4

to

00

to

113

Изобретение относится к автоматике и импульсной технике и может быть использовано в приборах для измере.- ния максимальных амплитудных значе- НИИ аналоговых сигналов.

Цель изобретения - упрощение устройства.

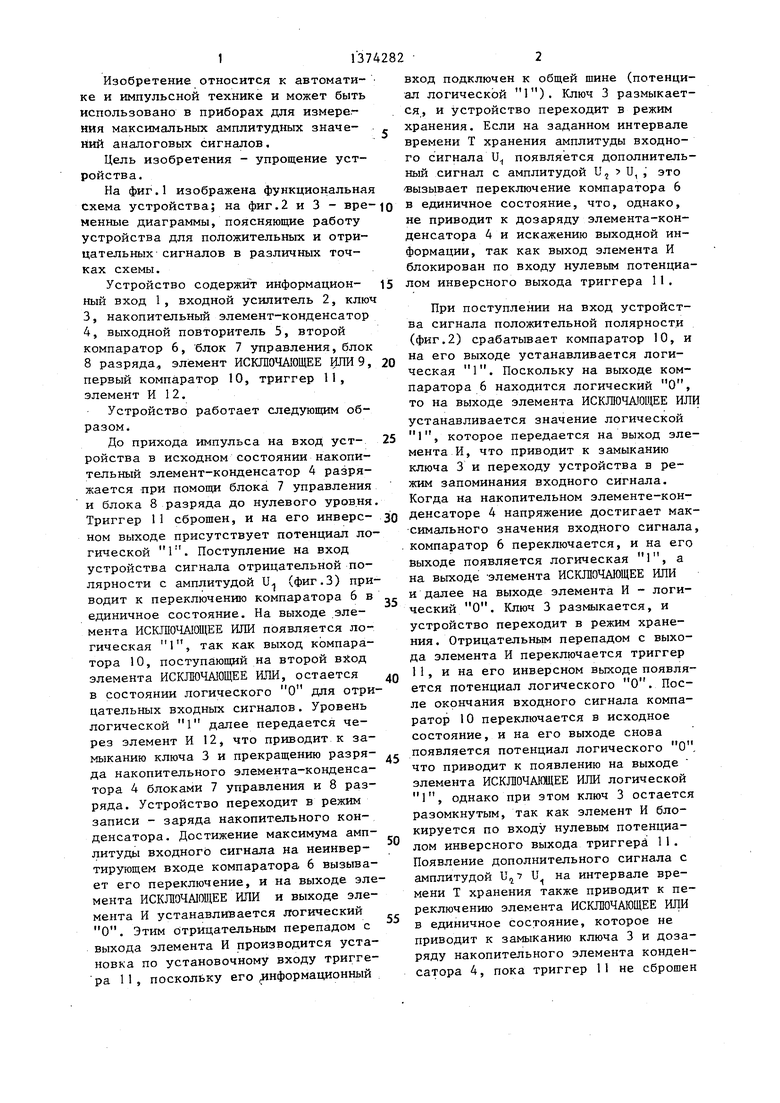

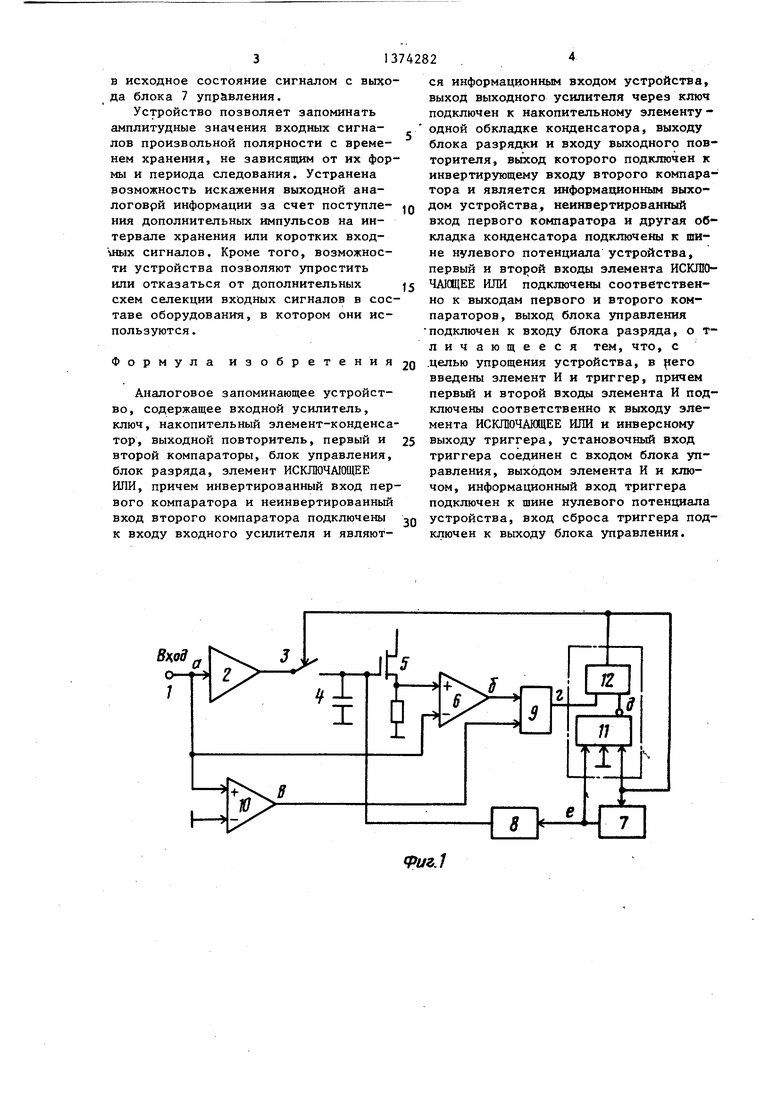

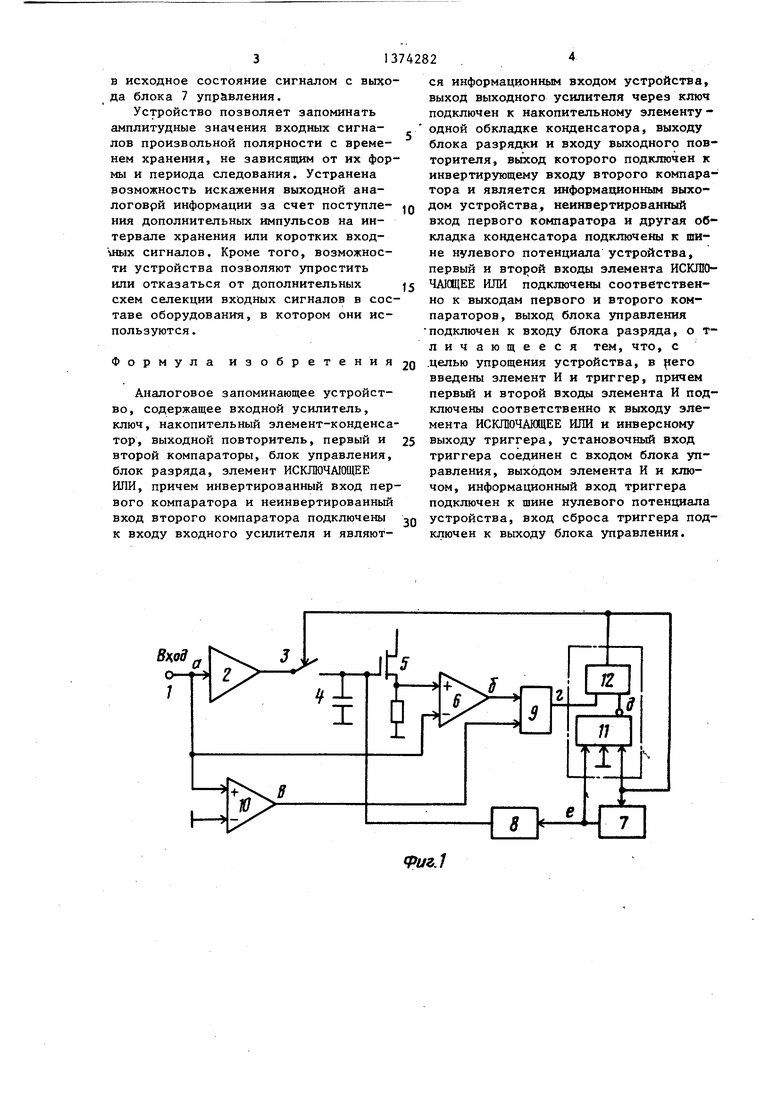

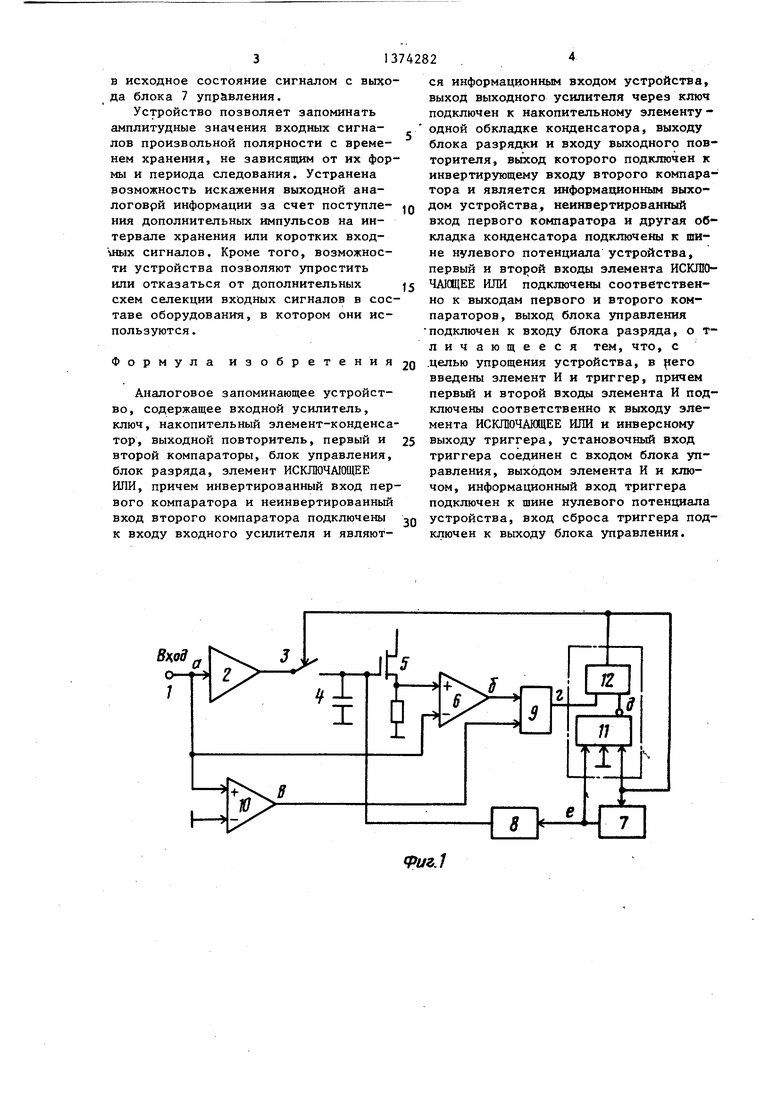

На фиг.1 изображена функциональна схема устройства; на фиг.2 и 3 - вре менные диаграммы, поясняющие работу устройства для положительных и отрицательных сигналов в различных точках схемы.

Устройство содержит информацион- ный вход 1, входной усилитель 2, клю

3,накопительный элемент-конденсатор

4,выходной повторитель 5, второй компаратор 6, блок 7 управления, блок

8 разряда, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, первый компаратор 10, триггер 11, элемент И 12.

Устройство работает следующим образом.

До прихода импульса на вход устройства в исходном состоянии накопительный элемент-конденсатор 4 разряжается при помощи блока 7 управления и блока 8 разряда до нулевого уровня Триггер 11 сброщен, и на его инверсном выходе присутствует потенциал логической 1. Поступление на вход устройства сигнала отрицательной полярности с амплитудой U (фиг.З) приводит к переключению компаратора 6 в единичное состояние. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ появляется логическая 1, так как выход компаратора 10, поступающий на второй вХод элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, остается в состоянии логического О для отрицательных входных сигналов. Уровень логической 1 далее передается через элемент И 12, что приводит к замыканию ключа 3 и прекращению разряда накопительного элемента-конденсатора 4 блоками 7 управления и 8 разряда. Устройство переходит в режим записи - заряда накопительного конденсатора. Достижение максимума амплитуды входного сигнала на неинвертирующем входе компаратора 6 вызывает его переключение, и на выходе элемента ИСКЛОЧАЮЩЕЕ ИЛИ и выходе элемента И устанавливается логический О. Этим отрицательным перепадом с выхода элемента И производится установка по установочному входу триггера 11, поскольку его .информационный

5

5

0

0

5

0

5

0

5

вход подключен к общей шине (потенциал логической 1). Ключ 3 размыкается, и устройство переходит в режим хранения. Если на заданном интервале времени Т хранения амплитуды входного сигнала и появляется дополнительный сигнал с амплитудой U, U, , это -вызывает переключение компаратора 6 в единичное состояние, что, однако, не приводит к дозаряду элемента-конденсатора 4 и искажению выходной информации, так как выход элемента И блокирован по входу нулевым потенциалом инверсного выхода триггера 11.

При поступлении на вход устройства сигнала положительной полярности (фиг.2) срабатывает компаратор 10, и на его выходе устанавливается логическая 1. Поскольку на выходе компаратора 6 находится логический О, то на выходе элемента ИСКЛ10ЧА ОЩЕЕ ИЛИ устанавливается значение логической 1, которое передается на выход элемента И, что приводит к замыканию ключа 3 и переходу устройства в режим запоминания входного сигнала. Когда на накопительном элементе-конденсаторе 4 напряжение достигает максимального значения входного сигнала, компаратор 6 переключается, и на его выходе появляется логическая 1, а на выходе элемента ИСКЛОЧАЮЩЕЕ ИЛИ и далее на выходе элемента И - логический О. Ключ 3 размыкается, и устройство переходит в режим хранения . Отрицательньт перепадом с выхода элемента И переключается триггер 11, и на его инверсном выходе появляется потенциал логического О. После окончания входного сигнала компаратор 10 переключается в исходное состояние, и на его выходе снова появляется потенциал логического О, что приводит к появлению на выходе элемента ИСКЛОЧАЩЕЕ ИЛИ логической 1, однако при этом ключ 3 остается разомкнутым, так как элемент И блокируется по входу нулевым потенциалом инверсного выхода триггера 11. Появление дополнительного сигнала с амплитудой U на интервале времени Т хранения также приводит к переключению элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в единичное состояние, которое не приводит к замыканию ключа 3 и доза- ряду накопительного элемента конденсатора 4, пока триггер 11 не сброшен

в исходное состояние сигналом с выхода блока 7 управления.

Устройство позволяет запоминать амплитудные значения входных сигналов произвольной полярности с временем хранения, не зависящим от их формы и периода следования. Устранена возможность искажения выходной ана- логоврй информации за счет поступления дополнительных импульсов на интервале хранения или коротких вход- шых сигналов. Кроме того, возможности устройства позволяют упростить или отказаться от дополнительных схем селекции входных сигналов в составе оборудования, в котором они используются .

Формула изобретен и я 20

Аналоговое запоминающее устройство, содержащее входной усилитель, ключ, накопительный элемент-конденсатор, выходной повторитель, первый и второй компараторы, блок управления, блок разряда, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем инвертированный вход первого компаратора и неинвертированный вход второго компаратора подключены к входу входного усилителя и являют10

20

15

25о 4282 .4

ся информационным входом устройства, выход выходного усилителя через ключ подключен к накопительному элементу - одной обкладке конденсатора, выходу блока разрядки и входу вьпсодного повторителя, выход которого подключен к инвертирующему входу второго компаратора и является информационным выходом устройства, неиивертир.ованный вход первого компаратора и другая обкладка конденсатора подключены к шине нулевого потенциала устройства, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены соответственно к выходам первого и второго компараторов, выход блока управления подключен к входу блока разряда, о т- личающееся тем, что, с .целью упрощения устройства, в рего введены элемент И и триггер, причем первый и второй входы элемента И подключены соответственно к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и инверсному выходу триггера, установочный вход триггера соединен с входом блока управления, выходом элемента И и ключом, информационный вход триггера подключен к шине нулевого потенциала устройства, вход сброса триггера подключен к выходу блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудно-временной анализатор | 1986 |

|

SU1413714A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

| Устройство для измерения рассогласования между углом и кодом | 1985 |

|

SU1277397A1 |

| Логарифмический преобразователь амплитуды импульсов | 1980 |

|

SU903906A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU543983A1 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Амплитудный детектор | 1987 |

|

SU1444674A1 |

Изобретение относится к автоматике и импульсной технике и может быть использовано в приборах для измерения максимальных амплитудных значений аналоговых сигналов. Цель изобретения - упрощение устройства. Поставленная цель обеспечивается з а счет устранения зависимости времени хр ане- ния от формы входных сигналов и периода их следования. Устройство обеспечивает запоминание амплитудных значений входных сигналов любой полярности на заданный промежуток времени, в течение которого блокируется выработка управляющих сигналов на коммутирующий элемент схемы и предотвращается возможная потеря и искажение выходной аналоговой информации. Устройство содержит усилитель, два компаратора, накопительный элемент- конденсатор, повторитель, блоки управления и разрядки, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и И, триггер. 3 ил. (Л

Bwd

(риг.1

| Аналоговое запоминающее устройство | 1976 |

|

SU639022A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU728162A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-02-15—Публикация

1986-06-09—Подача